文章目錄

- 下述將以stm32f407 為例

- 1. 時鐘系統及頻率分析

- 2. 時鐘配置

下述將以stm32f407 為例

1. 時鐘系統及頻率分析

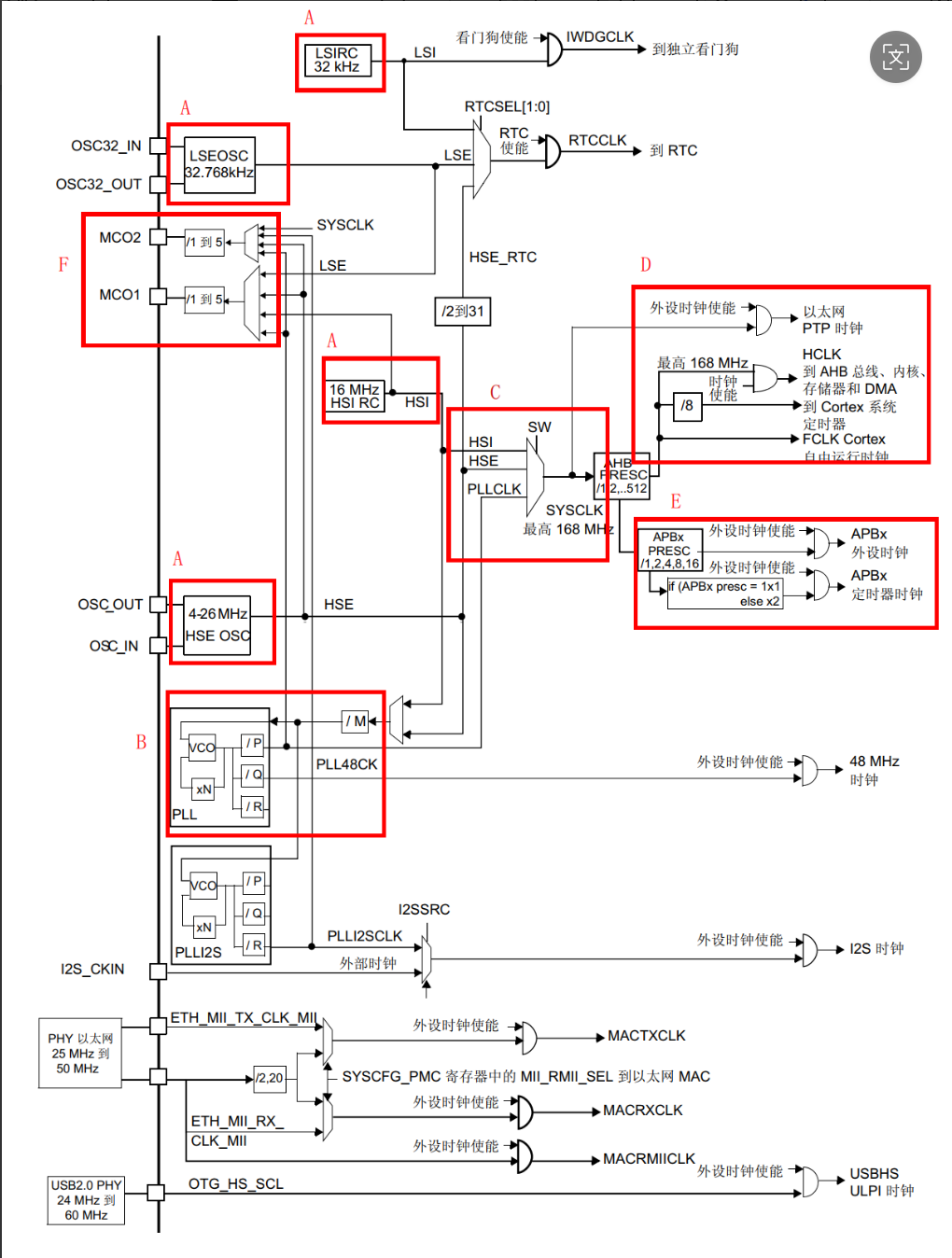

上述STM32F4時鐘系統圖解析入下:

- STM32F407 系列微控制器(基于 Cortex-M4 內核,帶 FPU)的工作頻率配置如下,其核心及外設時鐘均由時鐘樹(通過 PLL 倍頻、分頻器等從外部 / 內部振蕩器衍生)生成:

-

- 核心時鐘(FCLK Cortex clock,即 HCLK)

- 最高頻率:168 MHz(這是 STM32F407 的標稱最高主頻)。

- 作用:作為 Cortex-M4 內核的工作時鐘,直接決定 CPU 執行指令的速度(運算、數據處理等),是整個系統的 “核心頻率”。

-

- 系統時鐘(SYSCLK)

- 最高頻率:168 MHz(與核心時鐘同源,通常通過 PLL 從外部晶振(HSE)或內部高速振蕩器(HSI)倍頻得到)。

- 例如:外部 8 MHz 晶振(HSE)經 PLL 倍頻(8 MHz × 21 = 168 MHz)后作為系統時鐘。

-

- 總線時鐘

- AHB 總線時鐘(HCLK):最高 168 MHz(直接來自系統時鐘,或經 AHB 預分頻器分頻,通常配置為與系統時鐘同頻),為內核、內存(SRAM、Flash)及 AHB 外設(如 DMA、ETH 等)提供時鐘。

- APB1 總線時鐘(PCLK1):最高 42 MHz(低速外設總線)。

- 掛載外設:USART25、SPI23、I2C13、CAN、TIM27 等。

- APB1 定時器時鐘:當 APB1 預分頻器 > 1 時,定時器時鐘 = 2 × PCLK1(最高 84 MHz)。

- APB2 總線時鐘(PCLK2):最高 84 MHz(高速外設總線)。

- 掛載外設:USART1、SPI1、ADC1~3、TIM1、TIM8、GPIO 等。

- APB2 定時器時鐘:當 APB2 預分頻器 > 1 時,定時器時鐘 = 2 × PCLK2(最高 168 MHz)。

-

- 其他關鍵時鐘

- USB OTG FS 時鐘:固定 48 MHz(由 PLL 分頻得到,用于 USB 通信)。

- 以太網(ETH)時鐘:通常為 50 MHz(通過外部 PHY 或內部 PLL 生成,用于以太網通信)。

- 內部振蕩器:

- HSI(高速內部振蕩器):16 MHz(默認啟動時鐘,可作為 PLL 輸入)。

- LSI(低速內部振蕩器):40 kHz(用于 RTC、獨立看門狗等)。

- 外部振蕩器(HSE):通常為 8 MHz 或 25 MHz(硬件設計決定,精度高于內部振蕩器,常用作 PLL 輸入以獲得穩定高頻時鐘)。

總結

STM32F407 的最高核心頻率為 168 MHz,外設時鐘根據總線類型(APB1/APB2)和功能需求(如 USB、ETH)有不同的最高限制。實際應用中可通過 STM32CubeMX 配置時鐘樹,在功耗與性能之間平衡(例如降低主頻以減少功耗)。

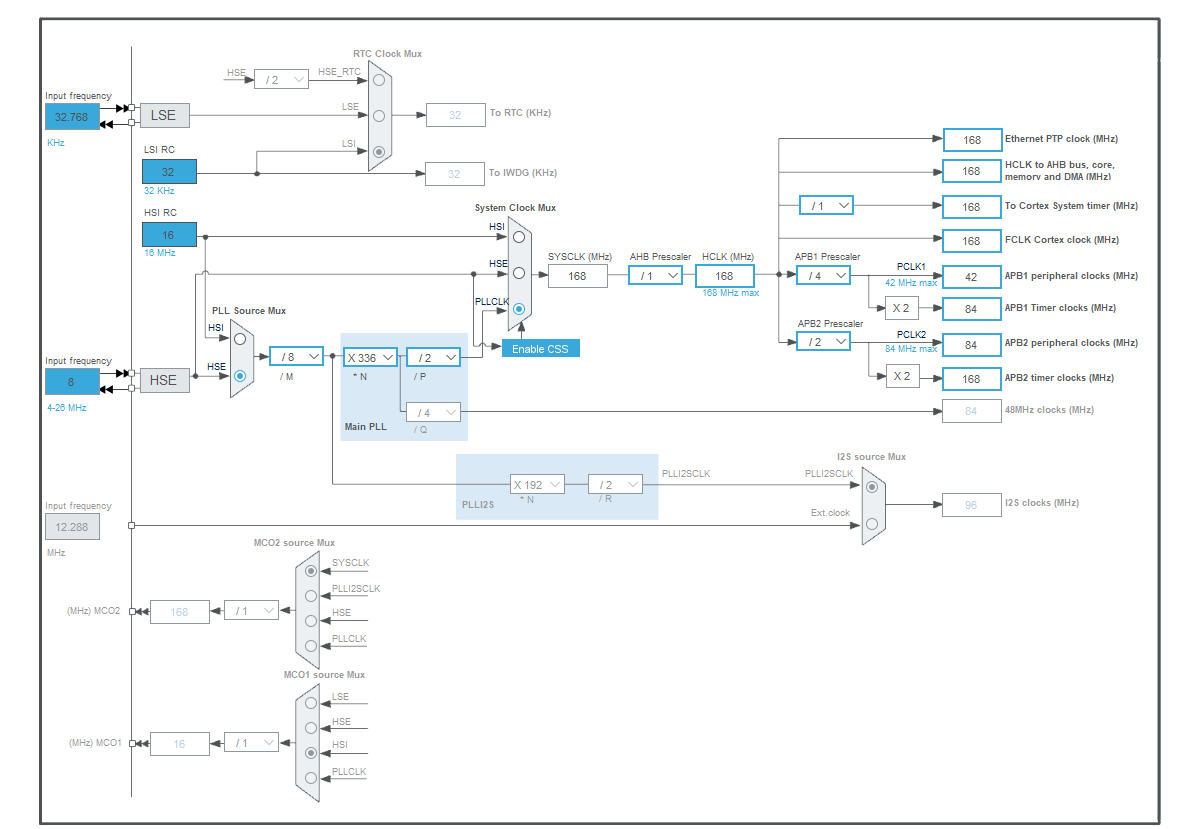

2. 時鐘配置

以正點原子的開發板, 開發板的外部高速晶振和外部低速晶振分別是:8MHz和32.768KHz, 通過stm32cubemx 通過分頻倍頻后配置如下:

)

)

)