目錄

2. The Cortex??A715 core

2.1 Cortex??A715 core features

2.2 Cortex??A715 core confifiguration options

2.3 DSU-110 dependent features

2.4 Supported standards and specifications

2.6 Design tasks

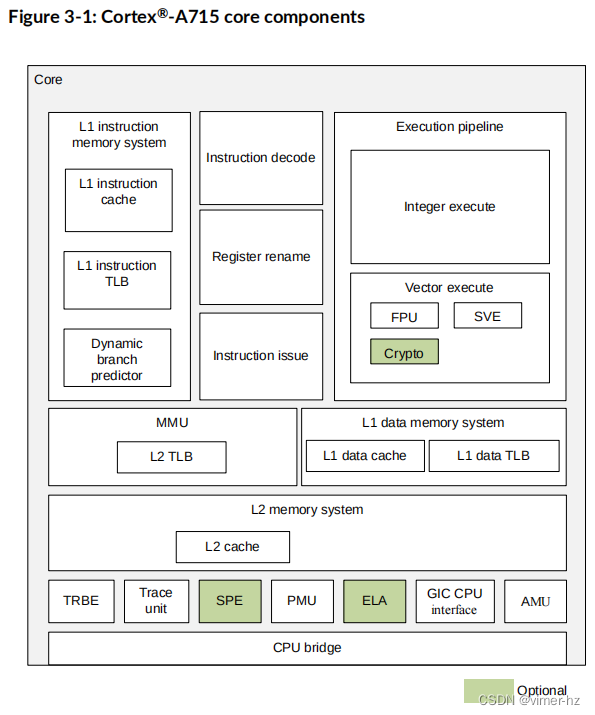

3. Technical overview

3.1 Core components

3.2 Interfaces

3.3 Programmers model

4. Clocks and resets

5. Power management

5.1 Voltage and power domains

5.2 Architectural clock gating modes ? ?//架構級的時鐘門控模式

5.3 Power control

5.4 Core power modes

5.5 Performance and power management

5.6 Cortex??A715 core powerup and powerdown sequence

5.7 Debug over powerdown

6. Memory management

6.1 Memory Management Unit components

6.2 TLB entry content ? ?//TLB條目的內容

6.3 TLB match process ? ?//TLB匹配過程

6.4 Translation table walks ? ?//轉換表遍歷

6.5 Hardware management of the Access flag and dirty state ? ?//訪問標志(Access Flag)和臟位(Dirty State)的硬件管理

6.6 Responses

6.7 Memory behavior and supported memory types

6.8 Page-based hardware attributes

7. L1 instruction memory system

7.1 L1 instruction cache behavior

7.2 L1 instruction cache Speculative memory accesses ? ?//L1指令緩存的推測性內存訪問

7.3 Program flow prediction

8. L1 data memory system

8.1 L1 data cache behavior

8.2 Write streaming mode

8.3 Instruction implementation in the L1 data memory system

8.4 Internal exclusive monitor ? ?//內部獨占監視器

8.5 Data prefetching

9. L2 memory system

9.1 L2 cache

9.2 Support for memory types

9.3 Transaction capabilities ? ?//事務能力

10. Direct access to internal memory

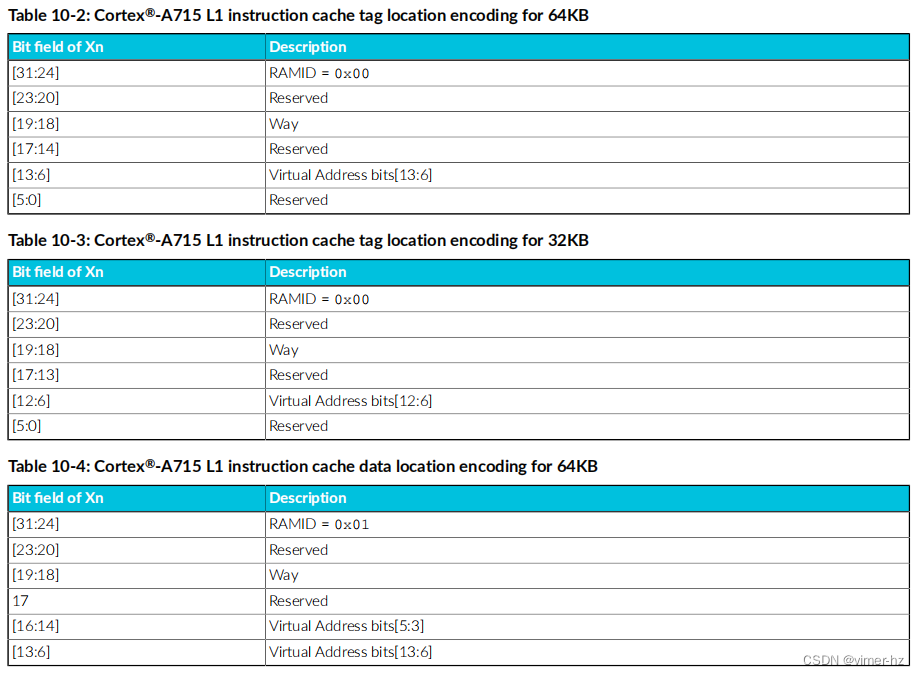

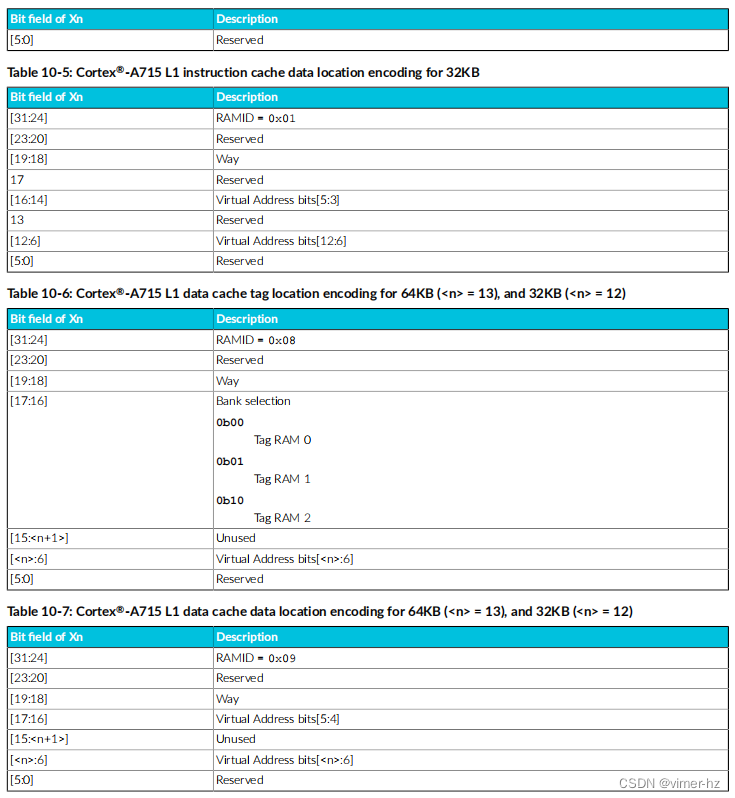

10.1 L1 cache encodings

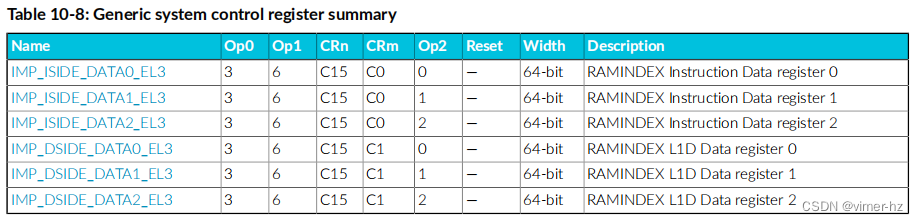

10.2 L2 cache encodings

10.3 L2 TLB encodings

11. RAS Extension support

11.1 Cache protection behavior

11.2 Error containment ? ?//錯誤隔離

11.3 Fault detection and reporting

11.4 Error detection and reporting

11.5 Error injection ? ?//錯誤注入

11.6 AArch64 RAS registers

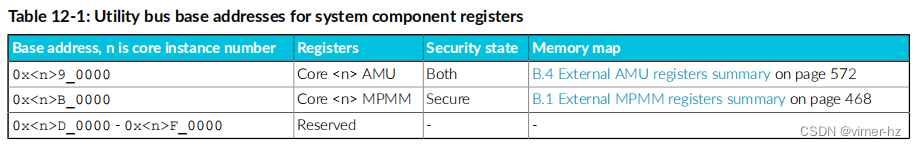

12. Utility bus

12.1 Base addresses for system components

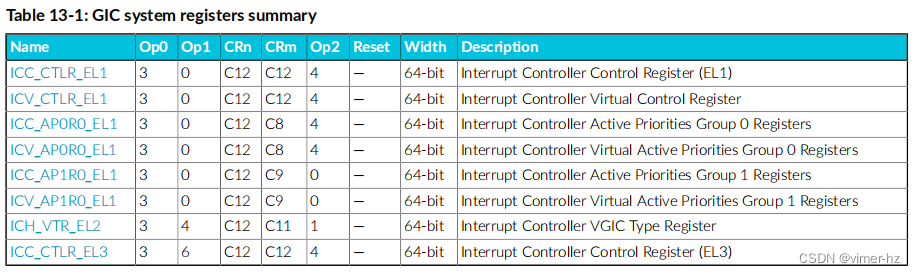

13. GIC CPU interface

13.1 Disable the GIC CPU interface

13.2 AArch64 GIC system registers

14. Advanced SIMD and floating-point support

15. Scalable Vector Extensions support

16. System control

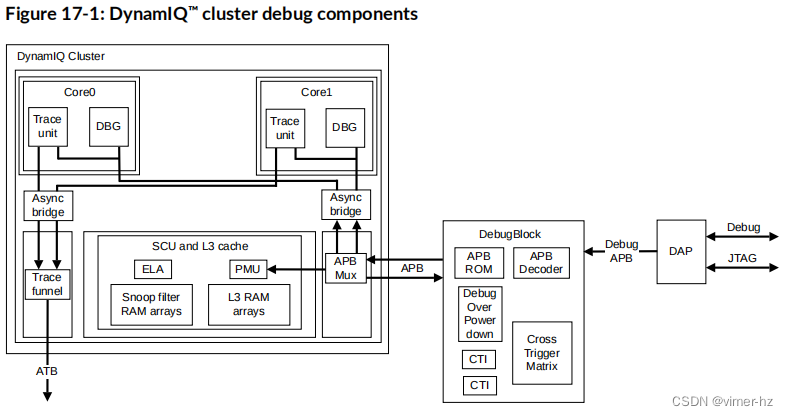

17. Debug

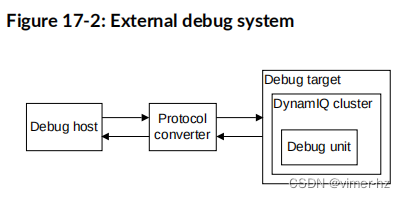

17.1 Supported debug methods

17.2 Debug register interfaces

17.3 Debug events

17.4 Debug memory map and debug signals

17.5 ROM table

17.6 CoreSight? component identifification

17.7 CTI register identifification values

17.8 External Debug registers

17.9 External ROM table registers

18. Performance Monitors Extension support

18.1 Performance monitors events

18.2 Performance monitors interrupts

18.3 External register access permissions

18.4 AArch64 Performance Monitors registers

18.5 External PMU registers

19. Embedded Trace Extension support

19.1 Trace unit resources

19.2 Trace unit generation options

19.3 Reset the trace unit

19.4 Program and read the trace unit registers

19.5 Trace unit register interfaces

19.6 Interaction with the Performance Monitoring Unit and Debug

19.7 ETE events

19.8 AArch64 Trace unit registers

19.9 External ETE registers

20. Trace Buffer Extension support

20.1 Program and read the trace buffer registers

20.2 Trace buffer register interface

21. Activity Monitors Extension support

21.1 Activity monitors access

21.2 Activity monitors counters

21.3 Activity monitors events

21.4 AArch64 Activity Monitors registers

21.5 External AMU registers

22. Statistical Profiling Extension Support

22.1 Statistical Profiling Extension events packet

22.2 Statistical Profiling Extension data source packet

2. The Cortex??A715 core

Cortex?-A715核心是一款平衡性能、低功耗和面積受限的產品,實現了Arm?v9.0-A架構。Arm?v9.0-A架構擴展了Arm?v8?A架構中定義的架構,延伸至Arm?v8.5-A。Cortex?-A715核心面向大屏幕計算應用和智能手機應用。

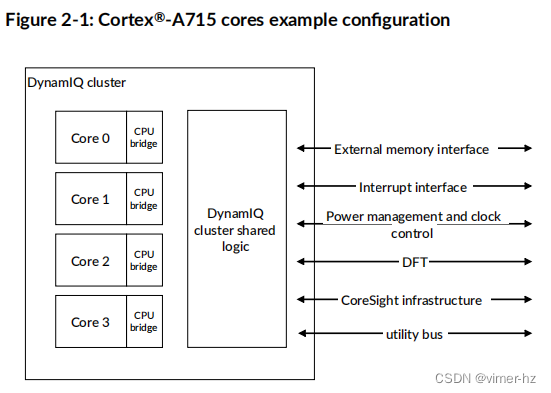

Cortex?-A715核心實現在DSU-110 DynamIQ?集群內部。它連接到DynamIQ?共享單元-110(DSU-110),作為具有L3緩存和嗅控功能的完整互連。這種連接配置也用于具有不同類型核心的系統中,其中Cortex?-A715核心是平衡性能核心。

下圖顯示了一個帶有四個Cortex?-A715核心的DynamIQ?集群的示例配置。

?這份手冊僅適用于Cortex?-A715核心。請將此手冊與Arm? DynamIQ? Shared Unit-110技術參考手冊一起閱讀,以獲取有關DSU-110的詳細信息。

這份手冊并未提供完整的寄存器列表。請將此手冊與Arm? A-profile架構參考手冊一起閱讀,以獲取更多信息。

2.1 Cortex??A715 core features

您可以在獨立的DynamIQ?配置中使用Cortex?-A715核心,也就是在Cortex?-A715核心的同質集群中使用。您還可以將Cortex?-A715核心用作異構集群中平衡性能的核心。

然而,無論是哪種集群配置,Cortex?-A715核心具有以下描述中列出的相同功能。

核心特性:

? 實現了Armv9.0-A A64指令集

? 所有異常級別(EL0至EL3)處于AArch64執行狀態

? 內存管理單元(MMU)

? 40位物理地址(PA)和48位虛擬地址(VA)

? 通用中斷控制器(GIC)CPU接口,用于連接外部中斷分發器

? 支持從外部系統計數器輸入64位計數的通用定時器接口

? 實現了可靠性、可用性和可維護性(RAS)擴展

? 實現了具有128位向量長度的可伸縮矢量擴展(SVE)和可伸縮矢量擴展2(SVE2)

? 集成的執行單元,具有高級單指令多數據(SIMD)和浮點支持

? 支持可選的密碼擴展功能

密碼擴展功能需要單獨許可。

? 活動監視單元(AMU)

Cache特性:

? 獨立的L1數據緩存和指令緩存

? 私有的、統一的L2數據和指令緩存

? 可選的錯誤保護,支持奇偶校驗或糾錯碼(ECC),允許在L1指令緩存、數據緩存、L2緩存和L2轉換查找緩沖區(TLB)上進行單錯誤修正和雙錯誤檢測(SECDED)

? 支持內存系統資源分區和監控(MPAM)

調試特性:

? Armv9.0-A調試邏輯

? 性能監視單元(PMU)

? 嵌入式跟蹤擴展(ETE)

? 跟蹤緩沖擴展(TRBE)

? 可選實現統計分析擴展(SPE)

? 可選嵌入式邏輯分析器(ELA),ELA-600

ELA-600需要單獨許可。

相關信息請參閱第31頁的技術概述。

2.2 Cortex??A715 core confifiguration options

在構建時配置中,您可以選擇滿足實現需求的選項。

可配置性是基于每個核心的,也就是說,在一個集群中,不同的Cortex?-A715核心可以具有不同的配置選項。

您可以使用以下選項來配置您的Cortex?-A715核心實現:

緩存保護

您可以選擇配置是否啟用緩存保護。

統計分析擴展(SPE)

您可以選擇配置是否啟用統計分析擴展(SPE)。

PMU計數器

您可以選擇配置PMU計數器的數量為6或20。

密碼擴展功能

您可以選擇配置是否啟用密碼擴展功能。密碼擴展功能需要單獨許可。

L1數據緩存大小

您可以選擇配置L1數據緩存大小為32KB或64KB。

L1指令緩存大小

您可以選擇配置L1指令緩存大小為32KB或64KB。

L2緩存大小

您可以選擇配置L2緩存大小為128KB、256KB或512KB。

CoreSight?嵌入式邏輯分析器(ELA)

您可以選擇包含支持集成ELA-600。ELA-600需要單獨許可。

時序閉合

您可以配置L2數據緩存RAM的時序行為。

有關詳細的配置選項和指南,請參閱Arm? Cortex?-A715 Core Configuration and Integration Manual中的RTL配置過程部分。

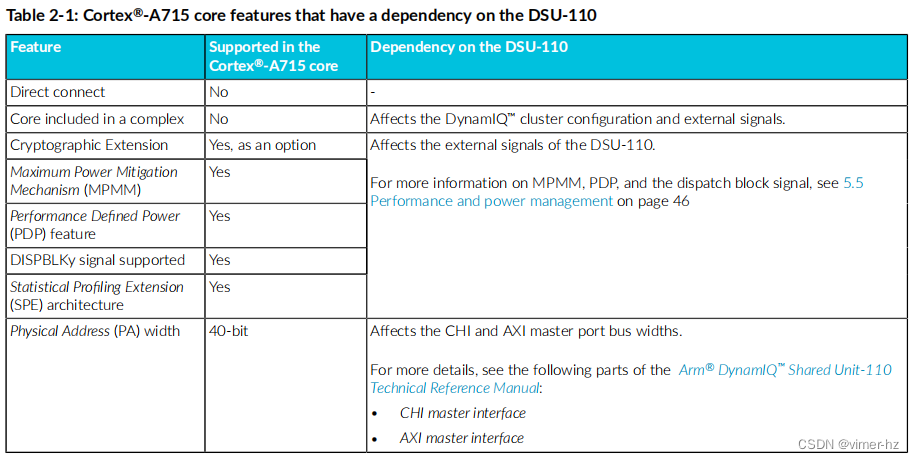

2.3 DSU-110 dependent features

某些DynamIQ?共享單元-110(DSU-110)特性和行為的支持取決于您所許可的核心是否支持特定功能。

以下表格描述了在您的Cortex?-A715核心中支持哪些基于DSU-110的特性。

Cryptographic Extension: 密碼擴展功能

Maximum Power Mitigation Mechanism (MPMM): 最大功率緩解機制(MPMM)

Performance Defined Power (PDP) feature: 性能定義功率(PDP)功能

DISPBLKy signal supported: 支持DISPBLKy信號

Statistical Profiling Extension (SPE) architecture: 統計分析擴展(SPE)體系結構

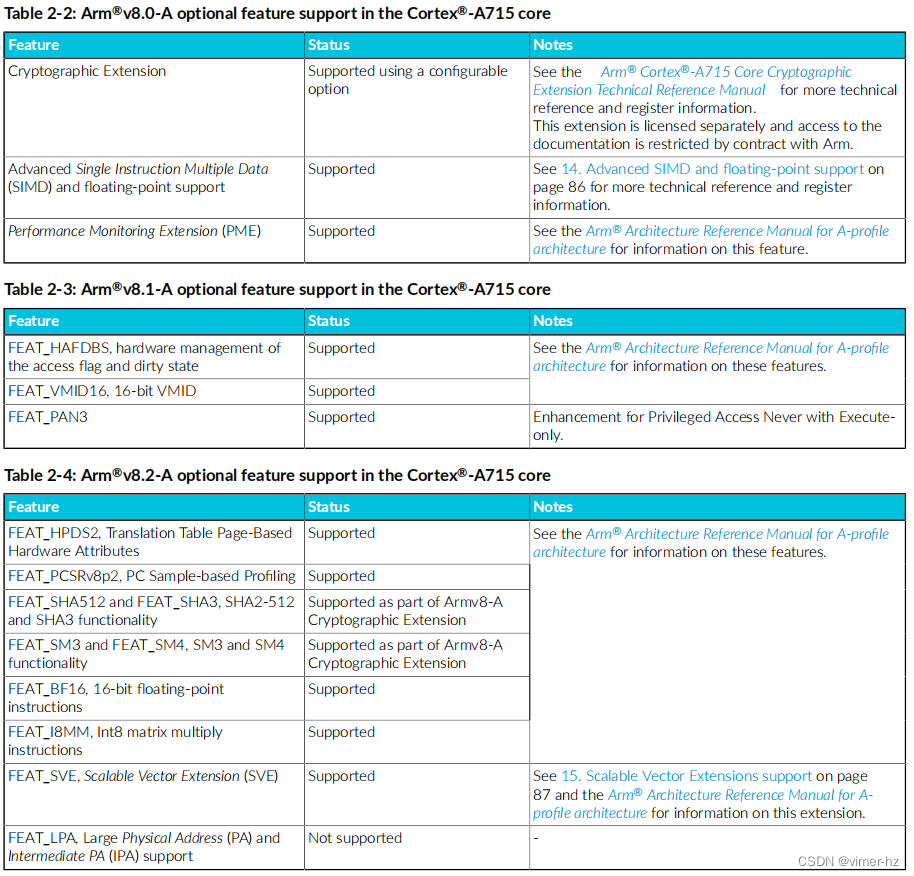

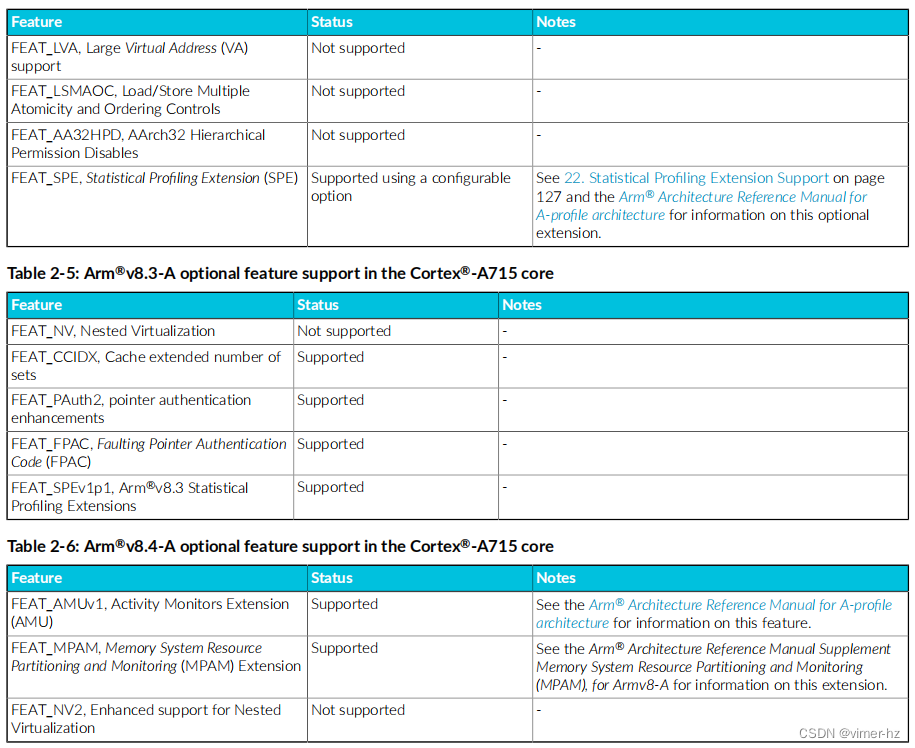

2.4 Supported standards and specifications

Cortex?-A715核心采用Arm?v9.0-A架構。Arm?v9.0-A架構擴展了在Arm?v8-A架構中定義的架構,直到Arm?v8.5-A。Cortex?-A715核心還實現了特定的Arm?v8-A架構擴展,并支持互連、中斷、計時器、調試和跟蹤體系結構。

Cortex?-A715核心僅支持AArch64架構的所有異常級別,從EL0到EL3,并支持每個架構版本的所有強制性功能。

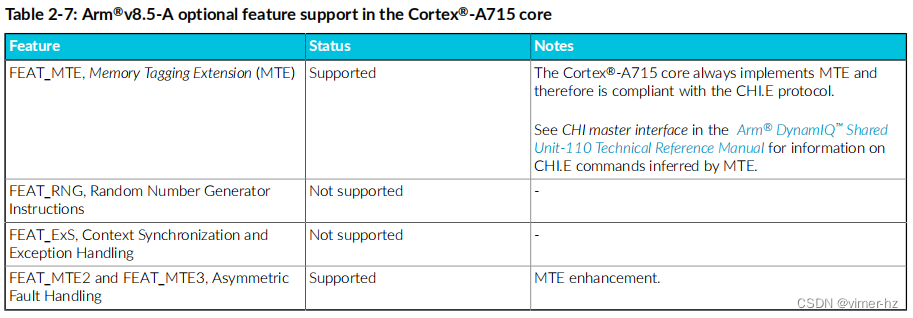

以下表格顯示了Cortex?-A715核心支持的每個Arm?v8-A架構版本的可選功能。

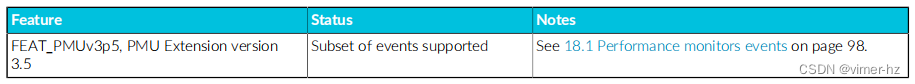

以下表格顯示了Cortex?-A715核心支持的Arm?v9.0-A功能。

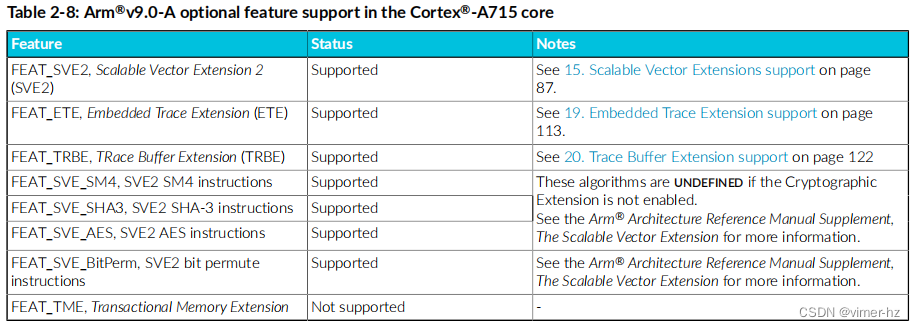

以下表格顯示了Cortex??A715核心支持的其他標準和規范。

相關信息:第31頁上的核心組件

2.6 Design tasks

Cortex??A715核心以SystemVerilog的可綜合RTL描述形式提供。在使用Cortex??A715核心之前,您需要進行實現、集成和編程。

以下是不同參與方可能執行的各項任務:

實現

實現者配置RTL,添加供應商單元/RAM,并將設計通過綜合和布局布線(P&R)步驟生成硬宏單元。

實現者選擇影響如何呈現RTL源文件的選項。這些選項可能會影響最終宏單元的面積、最大頻率、功耗和功能。

可以在實現流程中添加其他組件,例如DFT結構和必要時的電源開關。

集成

集成者將宏單元連接到SoC中。此任務包括將其連接到存儲系統和外設。

集成者通過將輸入引腳連接到特定值來配置核心的某些特性。這些配置設置會影響在進行任何軟件配置之前的啟動行為,并且還可以限制軟件可用的選項。

軟件編程

系統程序員開發軟件來配置和初始化核心,并測試應用軟件。

程序員通過向寄存器編程數值來配置核心。編程的數值會影響核心的行為。

最終設備的操作取決于構建配置、配置輸入和軟件配置。

請參閱Arm? Cortex??A715 Core Configuration and Integration Manual中的RTL配置過程,以及Arm? DynamIQ? Shared Unit-110 Configuration and Integration Manual中關于實現選項的內容。此外,還請參閱Arm? DynamIQ? Shared Unit-110 Configuration and Integration Manual中有關信號描述的內容。

3. Technical overview

Cortex??A715核心中的組件旨在使其成為一個平衡性能的核心。主要組件包括:

? L1指令和L1數據存儲系統

? L2存儲系統

? 寄存器重命名

? 指令解碼

? 指令發射

? 執行流水線

? 存儲管理單元(MMU)

? 追蹤單元和追蹤緩沖區

? 性能監控單元(PMU)

? 活動監控單元(AMU)

? 通用中斷控制器(GIC)CPU接口

? 分支預測

Cortex??A715核心通過CPU橋與DynamIQ? Shared Unit-110(DSU-110)進行接口連接。

Cortex??A715核心實現了Arm?v9.0-A架構。Arm?v9.0-A架構擴展了Arm?v8?A架構中定義的架構,一直延伸到Arm?v8.5-A。

程序員模型和實現的體系結構特性(例如通用計時器)符合第25頁上所述的2.4支持的標準和規范。

3.1 Core components

Cortex??A715核心包括一系列組件,旨在使其成為一個平衡性能、低功耗且面積受限的產品。Cortex??A715核心包括一個CPU橋,將核心連接到DynamIQ? Shared Unit-110(DSU-110)。DSU-110將核心連接到外部存儲系統和片上系統(SoC)的其他部分。

下圖顯示了Cortex??A715核心的組件。

L1 instruction memory system

L1指令存儲系統從指令緩存中獲取指令,并將指令流傳遞給指令解碼單元。

L1指令存儲系統包括:

? 32KB或64KB的4路組相聯式L1指令緩存,每個緩存行大小為64字節

? 完全關聯的L1指令轉換后置緩沖器(TLB),原生支持4KB、16KB、64KB和2MB頁面大小

? 動態分支預測器

Instruction decode

指令解碼單元將AArch64指令解碼為一個內部格式,并將其傳遞到執行流水線中。解碼單元負責解析指令的操作碼、操作數和操作順序,并將其轉換為可被執行的內部表示形式,以供后續階段執行。這樣,處理器可以正確地理解和執行指令的操作。解碼完成后,解碼單元將解碼后的指令傳遞給執行流水線的下一個階段,從而啟動指令的實際執行過程。

Register rename

寄存器重命名單元執行寄存器重命名,以便實現亂序執行,并將解碼的指令發送到各種發布隊列。

寄存器重命名是一種技術,通過為指令中的目標寄存器分配重命名寄存器,來解決由于指令間數據依賴關系而導致的數據沖突。這樣,不同的指令可以并發地使用相同的物理寄存器,從而允許指令亂序執行,提高了處理器的性能。

寄存器重命名單元負責分配重命名寄存器,并將解碼的指令發送到相應的發布隊列。發布隊列是用于保存將要執行的指令,并確保它們按照正確的順序進入執行階段。通過寄存器重命名和發布隊列的組合使用,處理器能夠更高效地利用指令級并行性,提升整體執行效率。

Instruction issue

指令分發單元控制解碼后的指令何時被分派到執行流水線。它包括用于存儲待分派到執行流水線的指令的發布隊列。

Integer execute

執行流水線包括整數執行單元,用于執行算術和邏輯數據處理操作。

Vector execute

矢量執行單元是執行流水線的一部分,用于執行高級SIMD和浮點運算。矢量執行單元執行可擴展矢量擴展(SVE)和可擴展矢量擴展2(SVE2)指令,并可選擇執行加密指令。

-高級SIMD和FP支持

高級SIMD是一種媒體和信號處理架構,主要添加了用于音頻、視頻、3D圖形、圖像和語音處理的指令。浮點數架構提供對單精度和雙精度浮點操作的支持。

-加密擴展

加密擴展在Cortex??A715核心中是可選的。加密擴展向高級SIMD和可擴展矢量擴展(SVE)指令集添加了新指令,加速以下功能:

- 高級加密標準(AES)加密和解密。

- 安全哈希算法(SHA)函數SHA-1、SHA-3、SHA-224、SHA-256、SHA-384和SHA-512。

- Armv8.2-SM SM3哈希函數和SM4加密和解密指令。

- 有限域算術,用于諸如Galois/Counter Mode和橢圓曲線密碼術等算法。

可選的加密擴展不包含在基本產品中。Arm僅在額外的Cortex??A715核心許可證下提供加密擴展。

-可擴展矢量擴展

可擴展矢量擴展(SVE)和可擴展矢量擴展2(SVE2)是Armv8-A架構的擴展。

它們是對AArch64高級SIMD和浮點功能的補充,而不是替代品。

L1 data memory system

L1數據內存系統執行加載和存儲指令,并處理內存一致性請求。

L1數據內存系統包括:

- 32KB或64KB的4路組關聯緩存,其中緩存行大小為64字節。

- 全關聯的L1數據TLB,原生支持4KB、16KB、64KB和2MB的頁面大小。

Memory Management Unit

內存管理單元(MMU)通過一組虛擬地址到物理地址映射和內存屬性,在轉換表中提供細粒度的內存系統控制。當地址被轉換時,這些映射關系會保存在TLB中。TLB條目包括全局標識符(ASID)和地址空間標識符(ASID),以防止上下文切換導致的TLB無效。它們還包括虛擬機標識符(VMID),以防止虛擬機切換時由虛擬機監視程序導致的TLB無效。

L2 memory system

L2內存系統包括L2緩存。L2緩存是私有的,每個核心具有8路組關聯性。您可以將其RAM大小配置為128KB、256KB或512KB。L2內存系統通過CPU橋連接到DSU-110。

Embedded Trace Extension and Trace Buffer Extension

Cortex??A715核心支持一系列的調試、測試和跟蹤選項,包括跟蹤單元和跟蹤緩沖區。

Cortex??A715核心還包括一個ROM表,其中包含系統中的組件列表。調試器可以使用ROM表確定實現了哪些CoreSight?組件。

Cortex??A715核心的所有調試和跟蹤組件都在本手冊中進行了描述。有關嵌入式邏輯分析儀(ELA)的更多信息,請參閱Arm? CoreSight? ELA-600嵌入式邏輯分析儀技術參考手冊。

Statistical Profiling Extension

在Cortex??A715核心中,統計分析擴展(SPE)是可選的。Cortex??A715核心實現了Arm?v8.2-A架構中的SPE。SPE提供了執行指令的性能特性的統計視圖,軟件開發者可以利用這些統計數據來優化代碼,以實現更好的性能。

Performance Monitoring Unit

性能監控單元(PMU)提供了6個或20個性能監視器,可以配置為收集每個核心和內存系統的操作統計數據。這些信息可用于調試和代碼性能分析。

Activity Monitoring Unit

Cortex??A715核心實現了Arm?v8.4-A架構中的活動監視器擴展。活動監視器在活動監視單元(AMU)中提供有用的信息,用于系統功耗管理和持續監控。

GIC CPU interface

通用中斷控制器(GIC)CPU接口,與外部分發器組件集成時,是支持和管理集群系統中斷的資源。

CPU bridge

在一個集群中,每個Cortex??A715核心和DSU-110之間有一個CPU橋。CPU橋控制核心和DSU-110之間的緩沖和同步。CPU橋是異步的,允許每個核心具有不同的頻率、功耗和面積實現點。您可以配置CPU橋以同步運行,而不影響其他始終同步的接口,如調試和跟蹤。

相關信息:

6. 內存管理(第51頁)

7. L1指令內存系統(第60頁)

8. L1數據內存系統(第63頁)

9. L2內存系統(第68頁)

13. GIC CPU接口(第84頁)

18. 性能監控擴展支持(第98頁)

19. 嵌入式跟蹤擴展支持(第113頁)

20. 跟蹤緩沖區擴展支持(第122頁)

21. 活動監視器擴展支持(第123頁)

22. 統計分析擴展支持(第127頁)

3.2 Interfaces

DynamIQ? Shared Unit-110 (DSU-110)是用于管理所有Cortex??A715核心與片上系統(SoC)之間的外部接口的模塊。

您可以參考Arm? DynamIQ? Shared Unit-110技術參考手冊中的技術概述,以獲取有關這些接口的詳細信息。

3.3 Programmers model

Cortex??A715核心實現了Arm?v9.0-A架構。Arm?v9.0-A架構擴展了Arm?v8?A架構,一直延伸到Arm?v8.5-A。Cortex??A715核心在所有異常級別(EL0到EL3)都支持AArch64執行狀態。

您可以參考Arm? Architecture Reference Manual for A-profile architecture,以獲取有關程序員模型的更多信息。

相關信息:

2.4 支持的標準和規范(第25頁)

4. Clocks and resets

為了實現動態的功耗節省,Cortex??A715核心支持分層時鐘門控(hierarchical clock gating)。它還支持熱重啟(Warm Reset)和冷重啟(Cold Reset)。

每個Cortex??A715核心只有一個時鐘域,并接收一個時鐘輸入信號。這個時鐘輸入信號由CPU橋中的一個架構級時鐘門控進行控制。

此外,Cortex??A715核心實施了廣泛的時鐘門控,包括:

? 針對各種模塊的區域時鐘門控,可以關閉部分時鐘樹

? 可以關閉單獨寄存器或寄存器組的本地時鐘門控

Cortex??A715核心從DynamIQ? Shared Unit-110(DSU-110)側的CPU橋接收以下復位信號:

? 熱重啟,用于對核心中除了以下部分之外的所有寄存器進行復位:

? ? 調試邏輯的一些部分

? ? 跟蹤單元邏輯的一些部分

? ? 可靠性、可用性和服務性(RAS)邏輯

? 冷重啟,用于對核心中的邏輯進行復位,包括調試邏輯、跟蹤邏輯和RAS邏輯。

有關核心時鐘門控和復位方案的完整描述,請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的以下章節:

? 時鐘和復位

? 使用功耗策略單元進行電源和復位控制

5. Power management

Cortex??A715核心提供了控制動態功耗和靜態功耗散發的機制。

動態功耗管理包括以下特性:

? 分層時鐘門控

? 每個核心的動態電壓頻率調節(DVFS)

靜態功耗管理包括以下特性:

? 關機(Powerdown)

? 動態保留(Dynamic retention),這是一種低功耗模式,保留寄存器和RAM狀態

5.1 Voltage and power domains

DynamIQ? Shared Unit-110(DSU-110)的功耗策略單元(PPU)用于控制Cortex??A715核心的功耗管理。該核心支持一個功耗域 PDCORE 和一個系統功耗域 PDCLUSTER。同樣,它支持一個核心電壓域 VCORE 和一個集群系統電壓域 VCLUSTER。功耗域和電壓域具有相同的邊界。

PDCORE 功耗域包含了所有的Cortex??A715核心邏輯以及屬于 VCORE 域的部分核心異步橋接邏輯。PDCLUSTER 功耗域包含了屬于 VCLUSTER 域的CPU橋接的部分邏輯。

下圖顯示了Cortex??A715核心的功耗域和電壓域。它還顯示了覆蓋CPU橋接系統側的集群功耗域和電壓域。

?如果滿足以下條件之一,您可以將VCORE和VCLUSTER電壓域連接到相同的電源上:

? 核心配置為與DSU-110同步運行,共享相同的時鐘。

? 核心不需要支持動態電壓頻率調節(DVFS)。

在具有多個Cortex??A715核心的集群中,每個核心都有一個 PDCORE<n>功耗域,其中n是核心的實例編號。如果不存在某個核心,則相應的功耗域也不存在。

下圖顯示了一個示例Cortex??A715配置的功耗域,其中包含一個四核心集群:

夾持(clamping)單元位于功耗域之間,通過功耗意圖文件(UPF)進行推斷,而不是在RTL中實例化。有關更多信息,請參閱Arm? Cortex??A715核心配置和集成手冊中的功耗管理部分。

Arm? Cortex??A715核心配置和集成手冊是一份機密文檔,只有在獲得相應產品許可證的情況下才可以獲得。

關于DSU-110集群功耗域和電壓域的詳細信息,請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的功耗管理部分。

5.2 Architectural clock gating modes ? ?//架構級的時鐘門控模式

WFI(Wait For Interrupt)和WFE(Wait For Event)指令將核心置于低功耗模式。這些指令會禁用時鐘樹頂部的時鐘信號。核心保持完全供電并保留其狀態。

5.2.1 Wait for Interrupt and Wait for Event

等待中斷(WFI)和等待事件(WFE)是一種功能,通過禁用大部分核心時鐘將核心置于低功耗狀態,同時保持核心供電。當核心處于WFI或WFE狀態時,輸入時鐘會在CPU橋接處對核心進行外部門控。

在WFI或WFE低功耗狀態下喚醒核心所需的邏輯會消耗少量的動態功耗。除此之外,繪制的功耗僅限于靜態漏電流。

當核心執行WFI或WFE指令時,它會等待核心中的所有指令(包括顯式的內存訪問指令)執行完畢,然后進入低功耗狀態。WFI和WFE指令還確保存儲指令已更新緩存或已提交給L3內存系統。

當事件寄存器被設置時執行WFE指令不會導致進入低功耗狀態,但會清除事件寄存器。

核心在以下事件發生時退出WFI或WFE狀態:

- 核心檢測到復位信號。

- 核心檢測到架構定義的WFI或WFE喚醒事件。

WFI和WFE喚醒事件可以包括物理中斷和虛擬中斷。

有關進入低功耗狀態和喚醒事件的更多信息,請參閱Arm?架構參考手冊A型架構部分。

5.2.2 Low-power state behavior considerations

要考慮到某些事件如何影響Cortex??A715核心的等待中斷(WFI)和等待事件(WFE)低功耗狀態行為。

在核心處于WFI或WFE狀態時,當檢測到以下任一事件時,核心內部的時鐘會臨時啟用:

- 必須由核心L1數據緩存或L2緩存處理的系統嗅探請求

- 必須由核心L1指令緩存、L1數據緩存、L2緩存或TLB處理的緩存或轉換查找緩沖器(TLB)維護操作

- 在效用總線接口上的訪問

- 通過高級外設總線(APB)接口進行的通用中斷控制器(GIC)CPU訪問或調試訪問

當時鐘被臨時啟用時,核心不會退出WFI或WFE狀態。

有關WFI和WFE的更多信息,請參閱Arm?架構參考手冊A型架構部分。

5.3 Power control

DynamIQ? Shared Unit-110(DSU-110)的功耗策略單元(PPU)控制著所有核心和集群的功耗模式轉換。

每個核心都有自己的PPU來控制其自身的核心功耗域。此外,還有一個用于控制整個集群的PPU。

PPU決定并請求任何功耗模式的變更。然后,Cortex??A715核心執行達到請求的功耗模式所需的任何操作。例如,在接受請求之前,核心可能會關閉時鐘、清除緩存或禁用一致性。

有關集群和核心的PPU的更多信息,請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的以下章節:

- 功耗管理

- 使用功耗策略單元進行功耗和復位控制

5.4 Core power modes

Cortex??A715核心的功耗域具有一組定義好的功耗模式,以及這些模式之間的合法轉換。每個核心的功耗模式可以獨立于集群中的其他核心。

核心的功耗策略單元(PPU)在集群級別管理該核心的功耗模式之間的轉換。有關更多信息,請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的功耗管理部分。

以下表格顯示了支持的Cortex??A715核心功耗模式。

未在下表中顯示的功耗模式不受支持,不能出現。違反合法的功耗模式可能會導致不可預測的結果。您必須遵守第48頁上描述的動態功耗管理、上電和下電序列。

以下圖示顯示了Cortex??A715核心功耗域支持的模式以及它們之間的合法轉換。

相關信息:

5.2 第40頁上的架構時鐘門控模式

5.4.4 第44頁上的全保持模式

5.2.1 第40頁上的等待中斷和等待事件模式

5.4.1 On mode

在On模式下,Cortex??A715核心處于開啟狀態并完全可操作。

可以將核心初始化為On模式。完成向On模式的轉換后,所有緩存都是可訪問和一致的。除了啟用緩存的正常架構步驟外,不需要額外的軟件配置。

5.4.2 Off mode

在關機模式下,核心完全斷電,不保留任何狀態。

在關機模式下,所有核心邏輯和RAM都處于關閉狀態。該域無法使用,所有核心狀態都會丟失。L1和L2緩存會被禁用、清除和失效,并且在進入關機模式時,核心會自動退出一致性。

在此模式下,冷重啟可以重置核心。

當核心域關閉時,嘗試對核心調試寄存器進行外部調試訪問或者對實用總線進行訪問會在內部調試接口返回錯誤響應。該錯誤表示核心不可用。

當核心處于關機模式時,可以訪問DebugBlock中與External Debug Over PowerDown (EDOPD)功能相關的特定于核心的調試寄存器。

5.4.3 Emulated off mode

在模擬關機模式下,所有核心域邏輯和RAM都保持開啟狀態。所有調試寄存器必須保留其狀態,并可以通過外部調試接口進行訪問。所有其他功能接口的行為與核心處于關機模式時相同。

5.4.4 Full retention mode ? ?//全保持模式

全保持模式是一種通過功耗策略單元(PPU)進行控制的動態保持模式。在喚醒時,可以恢復核心的全部功率,并繼續執行。

在全保持模式下,僅提供保持寄存器和RAM狀態所需的功率。核心處于保持狀態,無法操作。

當滿足以下所有條件時,核心進入全保持模式:

? 保持定時器已到期。有關設置保持定時器的更多信息,請參見A.1.17 IMP_CPUPWRCTLR_EL1,CPU電源控制寄存器。

? 核心處于等待中斷(WFI)或等待事件(WFE)的低功耗狀態。

? 核心時鐘沒有因以下任何原因而被臨時啟用:

? L1或L2快速緩存的snoop操作

? 緩存或轉換查找緩沖器(TLB)的維護操作

? 調試或通用中斷控制器(GIC)訪問

核心在檢測到以下任何事件時退出全保持模式:

? WFI或WFE的喚醒事件,根據Arm?架構參考手冊(A-profile architecture)的定義。

? 需要臨時啟用核心時鐘的事件,而不會退出WFI或WFE低功耗狀態。例如:

? L1或L2快速緩存的snoop操作

? 緩存或TLB的維護操作

? 來自DynamIQ? Shared Unit-110(DSU)的DebugBlock的調試訪問

? GIC訪問

5.4.5 Debug recovery mode ? ?//調試恢復模式

調試恢復模式支持對外部看門狗觸發的復位事件(例如看門狗超時)進行調試。

默認情況下,當核心從關機模式切換到開機模式時,會使其緩存失效。使用調試恢復模式可以在復位后觀察到復位前存在的L1緩存和L2緩存內容。緩存的內容會被保留,在切換回開機模式時不會被修改。

除了保留緩存內容,調試恢復還支持保留可靠性、可用性和可維護性(RAS)狀態。在調試恢復模式下,必須從外部應用 DSU-110 DynamIQ? 集群范圍的 Warm 復位。當將核心切換到開機模式時,RAS和緩存狀態會被保留。

調試恢復僅用于調試目的。不得將其用于功能目的,因為在進入此模式時無法保證緩存的正確操作。

調試恢復模式可以在任何時候發生,而核心的狀態沒有保證。此類請求會立即被接受,因此對核心、DynamIQ?集群或更廣泛的系統的影響是不可預測的,并且可能需要進行更廣泛的系統復位。特別地,在復位時,可能會完成復位時的任何未完成的內存系統事務。

核心不期望在復位后完成這些事務,可能會導致系統死鎖。

如果系統在調試恢復模式下向DynamIQ?集群發送散列請求,則取決于集群狀態:

? 散列請求可能會獲得響應并干擾緩存的內容。

? 散列請求可能無法獲得響應并導致系統死鎖。

5.4.6 Warm reset mode ? ?//熱復位模式

熱復位(Warm reset)會重置除追蹤邏輯、調試寄存器和可靠性、可用性和可維護性(RAS)寄存器之外的所有狀態。

當Cortex??A715核心從CPU橋的DynamIQ?共享單元-110(DSU-110)一側接收到熱復位信號時,將會應用熱復位來重置該核心的狀態。

Cortex??A715核心實現了Arm?v8?A Reset Management Register,即RMR_EL3。當核心在EL3模式下運行時,如果將RMR_EL3.RR位設置為1,則會請求進行熱復位。

有關RMR_EL3的更多信息,請參閱Arm? A-profile體系結構參考手冊。

5.5 Performance and power management

Cortex??A715核心實現了性能和功耗管理(PPM)功能,可用于限制核心內部的高活動事件或在效率和峰值性能之間進行權衡。

PPM功能包括:?

? 最大功耗緩解機制(MPMM)?

? 性能優化功耗(PDP)

5.5.1 Maximum Power Mitigation Mechanism ? ?//最大功耗緩解機制

最大功率緩解機制(MPMM)是一種功耗管理功能,用于檢測和限制高活動事件,特別是高功率的加載-存儲事件和向量單元指令。在評估期間,如果高活動事件的計數超過預定義的閾值,MPMM會臨時限制指令執行速率和內存系統事務。MPMM提供了三個檔位,使其能夠限制特定類別的工作負載。每個MPMM檔位以不同的適應性水平來限制工作負載,其中檔位0產生最激進的節流效果,而檔位2最不激進。活動監控單元(AMU)為每個檔位提供度量數據。外部功耗控制器可以利用這些度量數據來進行SoC功耗的預算管理,方式包括:

? 限制能夠執行高活動負載的核心數量

? 切換到不同的動態電壓和頻率調整(DVFS)工作點

MPMM并不旨在限制接近典型功率水平的工作負載。MPMM的事件檢測和限制目標是限制那些比典型整數工作負載具有顯著更高功耗的工作負載。

MPMM不能作為唯一的電氣安全機制。它本質上是一種在核心級別操作的局部輔助機制。MPMM并不替代粗粒度緊急功耗降低方案,但它確實最大程度減少了出現這類方案的可能性。它是第一道防線而不是完整的解決方案。

相關信息:

A.2.1 IMP_CPUPPMCR_EL3,在第253頁的全局PPM配置寄存器

A.4.27 IMP_CPUMPMMCR_EL3,在第320頁的全局MPMM配置寄存器

B.1.1 CPUPPMCR,在第468頁的全局PPM配置寄存器

B.1.2 CPUMPMMCR,在第470頁的全局MPMM配置寄存器

5.5.2 Performance Defined Power ? ?//性能優化功耗

性能優化功耗(PDP)是一種功耗管理功能,通過在常規工作負載上降低功耗范圍來換取峰值性能。

PDP的配置可在三個可能值中選擇不同的適應性水平。當適應性水平增加時,平均工作負載功耗減少,但會導致不同工作負載的性能損失增加。

//性能損失->功耗減少

PDP對以下方面產生影響:

? 核心功耗降低。核心功耗減少,效率提高。

? 外部內存系統功耗降低。調節內存請求帶寬以降低內存系統的功耗。

5.5.3 Dispatch block ? ?//調度阻塞

在極端核心溫度或功耗條件下,您可以臨時停止處理器的前進進程,而不停止時鐘。

DSU-110邊界上提供了一個引腳,可以直接用于強制處理器停頓,持續時間為引腳被激活的期間。當處理器停頓時,新指令的調度將停止。然而,已經調度的指令將繼續按照正常方式執行和完成。

5.6 Cortex??A715 core powerup and powerdown sequence

對于 Cortex?-A715 核心,沒有特定的順序來啟動。要關閉核心,您必須按照特定的順序進行操作。在復位后,不需要進行軟件步驟來確保核心在一致性上。

以下是關閉 Cortex?-A715 核心的步驟:

1. 如果需要,將核心狀態保存到系統內存中,以便在核心上電時可以恢復核心狀態。

2. 禁用核心的中斷:

? ?a. 在 ICC_IGRPEN0_EL1 和 ICC_IGRPEN1_EL1 寄存器中禁用中斷使能位。

? ?b. 使用 GICR_WAKER 寄存器設置 GIC 分發器的喚醒請求。

? ?c. 讀取 GICR_WAKER 寄存器,確認 ChildrenAsleep 位指示接口處于靜止狀態。

3. 禁用 RAS 寄存器的中斷輸出,或者將核心的 RAS 故障和錯誤中斷輸出重定向到系統錯誤管理器。有關更多信息,請參閱第49頁的“在核心關機期間管理 RAS 故障和錯誤中斷”的5.6.1節。

4. 將 IMP_CPUPWRCTLR_EL1.CORE_PWRDN_EN 位設置為1,表示請求關機。

5. 執行 ISB 指令。

6. 執行 WFI 指令。一旦執行了 WFI 指令,關機序列就不可中斷。

在執行 WFI 指令后,如果從電源控制器收到關機請求,硬件將執行以下操作:

- 禁用和清理核心緩存

- 從系統一致性中移除核心

當設置了 IMP_CPUPWRCTLR_EL1.CORE_PWRDN_EN 位時,執行 WFI 指令會自動屏蔽核心中的所有中斷和喚醒事件。因此,應用復位是唯一喚醒核心從等待中斷(WFI)狀態的方法。

5.6.1 Managing RAS fault and error interrupts during the core powerdown

//在核心關機期間管理 RAS(Reliability, Availability, and Serviceability)故障和錯誤中斷。

在執行 WFI 指令后,電源管理架構不允許中斷核心軟件的執行。

因此,在以下情況下,無法通過中斷來管理任何 RAS 故障或錯誤:

- 在核心關機程序執行 WFI 指令之前檢測到 RAS 故障或錯誤,并且錯誤尚未清除。

- 在核心關機程序執行 WFI 指令后檢測到 RAS 故障或錯誤。

您必須管理 RAS 故障和錯誤中斷的狀態,以完成核心關機序列。如果核心中存在活動的 RAS 故障或錯誤中斷,則阻止核心關機,因此:

- 核心保持通電狀態,但軟件處于非活動狀態。

- 核心處理器功率管理單元(PPU)發出的所有關機請求將被拒絕。

- 重新啟動核心軟件的唯一機制是進行完整的集群復位。

如果在核心關機過程之前禁用了 RAS 故障和錯誤中斷輸出,并且啟用了錯誤檢測和糾正響應,那么以下情況成立:

- 可糾正的錯誤將會被糾正。

- 可延遲處理的錯誤將會作為自動緩存清理和失效過程的一部分進行延遲處理。

- 當核心關閉電源時,可糾正和可延遲處理的錯誤記錄將會丟失。

- 如果在核心關閉電源時存在不可糾正的錯誤,則不會向系統發出錯誤信號,并且可能會破壞系統行為。

如果方便的話,您可以禁用對可糾正和可延遲處理錯誤的 RAS 故障和錯誤中斷生成,同時啟用對不可糾正錯誤的中斷。然而,在執行核心關機程序中的 WFI 指令之前,必須重新路由核心的錯誤中斷輸出到系統錯誤管理器。為此,可以按照以下方式配置 ERxCTLR_EL1 寄存器:

- ERxCTLR_EL1.CFI = 0

- ERxCTLR_EL1.FI = 0

- ERxCTLR_EL1.UI = 1

如果在關機過程中發生不可糾正的錯誤,核心將保持通電狀態,軟件將處于非活動狀態。此時,系統錯誤管理器負責重置整個集群以及與核心和集群交互的更廣泛系統。要使用這種方法,系統必須設計成允許核心的 RAS 錯誤中斷重新路由到系統錯誤管理器。由于核心的 RAS 寄存器僅對在核心上運行的軟件可訪問,系統錯誤管理器無法確定不可糾正的錯誤發生在核心的哪個位置。

5.7 Debug over powerdown

Cortex?-A715核心支持調試關機功能,允許調試器在核心關機時保持與核心的連接。這種行為使得調試可以在關機情況下繼續進行,而不需要每次重新建立連接。

調試關機邏輯是DynamIQ? Shared Unit-110(DSU-110)中的DebugBlock的一部分。DebugBlock位于DSU-110 DynamIQ?集群之外,并且在調試關機過程中必須保持通電狀態。

詳細信息請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的調試章節。

6. Memory management

內存管理單元(MMU)將輸入地址轉換為輸出地址。這種轉換基于在Cortex?-A715核心內部寄存器和轉換表中可用的地址映射和內存屬性信息。MMU還控制每個內存區域的內存訪問權限、內存屬性和緩存策略。

從輸入地址到輸出地址的地址轉換被描述為地址轉換的一個階段。Cortex?-A715核心可以執行以下操作:

- 第1階段轉換,將輸入虛擬地址(VA)轉換為輸出物理地址(PA)或中間物理地址(IPA)。

- 第2階段轉換,將輸入IPA轉換為輸出PA。

- 組合的第1階段和第2階段轉換,將輸入VA轉換為IPA,然后將該IPA轉換為輸出PA。Cortex?-A715核心對每個轉換階段執行轉換表遍歷。

除了將輸入地址轉換為輸出地址,地址轉換的一個階段還定義了輸出地址的內存屬性。對于兩個階段的轉換,第2階段的轉換可以修改第1階段轉換定義的屬性。地址轉換的一階段可以被禁用或繞過,并且核心可以為禁用和繞過的轉換階段定義內存屬性。

每個地址轉換階段使用存儲在內存映射轉換表中的地址轉換和相關內存屬性。轉換表項可以緩存在TLB(Translation Lookaside Buffer)中。轉換表項使得MMU能夠提供細粒度的內存系統控制,并控制表遍歷硬件。

有關虛擬內存系統體系結構(VMSA)的更多信息,請參閱Arm? Architecture Reference Manual for A-profile architecture。

6.1 Memory Management Unit components

Cortex??A715核心的內存管理單元(MMU)包括多個Translation Lookaside Buffers (TLBs)、一個L2 TLB和一個轉換表預取器。 TLB是MMU內部存儲最近執行的頁轉換的緩存。Cortex??A715核心采用了兩級TLB結構。L2 TLB存儲所有頁面大小,并在L1數據TLB或L1指令TLB需要時將這些頁面分割成較小的頁面。 下表描述了MMU的組件。

TLB條目包含以下內容:

? 全局指示器和地址空間標識符(ASID),允許在上下文切換時無需使TLB失效

? 虛擬機標識符(VMID),允許虛擬化管理程序(hypervisor)進行虛擬機切換,而無需使TLB失效

L1指令TLB的命中可以在一個時鐘周期內訪問轉換,并將物理地址(PA)返回給指令緩存進行比較。它還檢查訪問權限,以發出指令異常信號。

L1數據TLB的命中可以在一個時鐘周期內訪問轉換,并將物理地址(PA)返回給數據緩存進行比較。它也檢查訪問權限,以發出數據異常信號。

在L1數據TLB中未命中但在L2 TLB中命中的情況下,與L1數據TLB中的命中相比,會有5個時鐘周期的延遲。根據待處理請求的仲裁,這個延遲可能會增加。

6.2 TLB entry content ? ?//TLB條目的內容

轉換查找緩沖區(TLB)條目存儲所需的上下文信息,以便進行匹配并避免在上下文或虛擬機切換時需要進行TLB清理。

每個TLB條目包含以下內容:

? 虛擬地址(VA)

? 物理地址(PA)

? 一組內存屬性,包括類型和訪問權限

每個TLB條目與以下之一相關聯:

? 特定的地址空間標識符(ASID)

? 全局指示器

每個TLB條目還包含一個字段,用于存儲適用于從EL0和EL1進行訪問的虛擬機標識符(VMID)。VMID允許hypervisor進行虛擬機切換,而無需使TLB失效。

相關信息

第54頁的6.4節“轉換表遍歷”

6.3 TLB match process ? ?//TLB匹配過程

Armv8-A架構支持多個以不同方式進行轉換的虛擬地址(VA)空間。

每個轉譯查找緩沖區(TLB)條目與特定的轉換方案相關聯:

? 安全EL3

? 安全EL2

? 安全EL2和EL0

? 非安全EL2

? 非安全EL2和EL0

? 安全EL1和EL0

? 非安全EL1和EL0

當滿足以下條件時,將發生TLB匹配條目:

? 其VA[48:N],其中N是存儲在TLB條目中的該轉換的塊大小的log2,與請求的地址匹配。

? 條目的轉換方案與當前的轉換方案匹配。

? 地址空間標識符(ASID)與與目標轉換方案相關聯的TTBR0_ELx或TTBR1_ELx寄存器中保存的當前ASID匹配,或者該條目被標記為全局。

? 虛擬機標識符(VMID)與VTTBR_EL2寄存器中保存的當前VMID匹配。

ASID信息用于以下條目的TLB匹配:

? 使用安全EL1&0和非安全EL1&0的轉換方案

? 使用安全EL2&0和非安全EL2&0的轉換方案

VMID信息用于以下條目的TLB匹配:

? 當啟用EL2時,使用安全EL1&0和非安全EL1&0的轉換方案。

6.4 Translation table walks ? ?//轉換表遍歷

當Cortex?-A715核心生成內存訪問時,內存管理單元(MMU)會在轉譯查找緩沖區(TLB)中搜索所請求的虛擬地址(VA)。如果不存在,則會發生缺失,此時MMU會繼續在轉譯表遍歷過程中查找。

當Cortex?-A715核心生成內存訪問時,MMU會執行以下操作:

1. 在相關的指令或數據L1 TLB中對請求的VA、當前地址空間標識符(ASID)、當前虛擬機標識符(VMID)和當前轉換方案進行查找。

2. 如果相關的L1 TLB中沒有命中,那么MMU會在L2 TLB中對請求的VA、當前ASID、當前VMID和轉換方案進行查找。

3. 如果L2 TLB中也沒有命中,那么MMU會進行硬件轉換表遍歷。

只有在啟用MMU時才執行地址轉換。可以針對特定的轉換基址寄存器禁用MMU,這種情況下MMU會返回一個轉換錯誤。

您可以編程設置MMU使轉換表遍歷生成的訪問可緩存。這意味著轉換表條目可以緩存在L2緩存、L3緩存和外部緩存中。

在查找或轉換表行走過程中,匹配的轉換表條目中的訪問權限位確定訪問是否被允許。如果權限檢查違反了規定,那么MMU會返回一個權限錯誤。有關更多信息,請參閱Arm?架構參考手冊Armv8-A架構配置文件。

下圖顯示了TLB查找過程。

在轉換表遍歷過程中,描述符從L2緩存或外部存儲系統中獲取。

6.5 Hardware management of the Access flag and dirty state ? ?//訪問標志(Access Flag)和臟位(Dirty State)的硬件管理

該核心包括執行對轉換表進行硬件更新的選項。

這個功能在TCR_ELx(其中x為1-3)和VTCR_EL2中啟用。為了支持臟位的硬件管理,轉換表描述符中包含了Dirty Bit Modifier (DBM)字段。

Cortex?-A715核心僅在轉換表存儲在Inner Write-Back和Outer Write-Back Normal內存區域時支持對訪問標志和臟位的硬件更新。

如果軟件在非Inner Write-Back或Outer Write-Back Normal內存區域請求進行硬件更新,則Cortex?-A715核心返回以下編碼的中止信息:

? 對于數據中止,ESR_ELx.DFSC = 0b110001

? 對于指令中止,ESR_ELx.IFSC = 0b110001

6.6 Responses

在某些故障和中止情況下,由于內存訪問,可能會觸發異常。

MMU響應

當完成以下操作之一時,內存管理單元(MMU)會向請求方生成一個轉換響應:

? L1指令或數據轉譯查找緩沖器(TLB)命中

? L2 TLB命中

? 轉換表遍歷

從MMU返回的響應包含以下信息:

? 對應于轉換的物理地址(PA)

? 一組權限

? 安全狀態或非安全狀態信息

? 報告中止所需的所有信息

MMU中止

MMU可以檢測與地址轉換相關的故障,并可能導致異常傳遞到核心。這些故障可能包括地址大小故障、翻譯故障、訪問標志故障和權限故障。

外部中止

外部中止發生在內存系統中,與MMU檢測到的中止不同。

通常情況下,外部內存中止很少發生。外部中止由外部內存接口標記的錯誤或L1數據緩存或L2緩存數組中未糾正的糾錯碼(ECC)錯誤引起。

當發生以下情況時,同步地報告外部中止:

? 用于指令獲取、加載和存儲的轉換表行走

? 將操作加載到內部寫回、外部寫回正常可緩存內存

在Fault Address Register(FAR)中捕獲的地址是生成同步外部中止的指令的目標地址。

異步地報告外部中止發生在以下情況下:

? 在不是由轉換表行走引起的情況下,將加載操作應用于除內部寫回、外部寫回正常內存之外的所有內存位置

? 對任何內存類型進行存儲操作

? 緩存維護、TLB使失效和指令緩存使失效操作

? 包括AtomicLd、AtomicSt、AtomicCAS和AtomicSwap在內的原子操作

錯誤編程的連續提示

在出現錯誤編程的連續提示情況下,當存在一個包含置位CH位的描述符時,輸入的虛擬地址(VA)地址空間必須包括此塊中的所有連續VA。

VA地址空間由以下因素定義:

? 階段1翻譯:TCR_ELx.TxSZ

? 階段2翻譯:VTCR_EL2.T0SX

Cortex??A715核心將此類塊視為不會引起翻譯錯誤,并忽略連續位的值。

沖突中止

Cortex??A715核心不會生成沖突中止異常。

當在L1 TLB或L2 TLB中檢測到TLB沖突時,硬件會自動處理沖突,通過使沖突條目無效來解決沖突。

6.7 Memory behavior and supported memory types

Cortex??A715核心支持Armv8-A架構中定義的內存類型。 設備內存類型具有以下屬性:

G – Gathering(聚合)?

將多個請求聚合并合并為單個事務的能力?

R – Reordering(重排序)?

對事務進行重排序的能力?

E – Early Write Acknowledgement(提前寫入確認)?

接受來自互聯的寫入事務的提前確認的能力?

在下表中,前綴n表示不允許該能力。?

以下表格顯示了Cortex??A715核心中支持的內存類型。

下表顯示了對于特定的Normal內存,如何處理共享性(shareability)。

6.8 Page-based hardware attributes

Page-Based Hardware Attributes (PBHA)是一個可選的、實現定義的特性。它允許軟件在轉換表中設置最多四個位,然后通過內存系統傳播這些位,并可用于控制系統組件。這些位的含義特定于系統設計。

要了解如何在轉換表中設置和啟用PBHA位,請參閱Arm? A型架構參考手冊。當禁用時,總線上傳播的PBHA值為0。

對于由轉換表遍歷引起的內存訪問,ATCR和AVTCR寄存器控制PBHA值。

在內存訪問中,stage 1和stage 2之間的PBHA組合

PBHA應始終被視為物理地址的屬性。

當同時啟用stage 1和stage 2時:

- 如果stage 1 PBHA和stage 2 PBHA都啟用,則最終的PBHA是stage 2 PBHA。

- 如果stage 1 PBHA啟用且stage 2 PBHA禁用,則最終的PBHA是stage 1 PBHA。

- 如果stage 1 PBHA禁用且stage 2 PBHA啟用,則最終的PBHA是stage 2 PBHA。

- 如果stage 1 PBHA和stage 2 PBHA都禁用,則最終的PBHA被定義為0。

啟用PBHA的粒度是一位,因此該屬性獨立地應用于每個PBHA位。

不匹配的別名

如果通過多個虛擬地址映射訪問相同的物理地址,并且這些映射中的PBHA位不同,則結果是不可預測的。總線上傳播的PBHA值可以是任一映射的值。

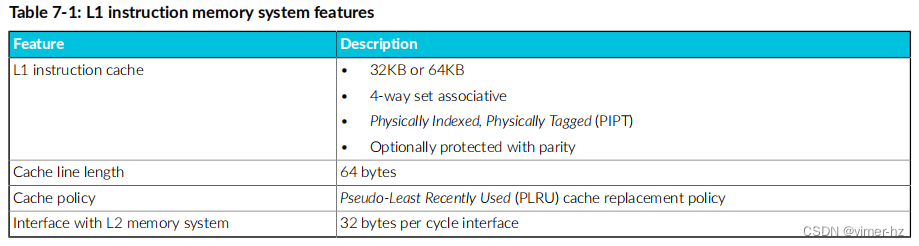

7. L1 instruction memory system

The Cortex?-A715核心的L1指令存儲器系統用于獲取指令并預測分支。它包括L1指令緩存、L1指令轉換查找緩沖器(TLB)和分支預測單元。

L1指令存儲器系統為解碼器提供指令流。為了提高整體性能并降低功耗,L1指令存儲器系統使用動態分支預測和指令緩存。

以下表格顯示了L1指令存儲器系統的特性:

L1指令TLB也位于L1指令存儲器系統中。然而,它是內存管理單元(MMU)的一部分,并在第51頁的“內存管理”部分進行了描述。

7.1 L1 instruction cache behavior

L1指令緩存在復位時會自動失效,除非將核心功耗模式初始化為“調試恢復”模式。

在調試恢復模式下,L1指令緩存無法正常工作。

禁用L1指令緩存

不會對L1指令緩存的操作產生影響。即使在禁用狀態下,指令仍然可以被緩存到L1指令緩存中,并從中獲取。軟件必須考慮到非緩存訪問,以確保正確的行為。更多詳情請參閱Arm? A-profile架構參考手冊。

如果禁用了L1指令緩存,則由于指令獲取引起的所有內存訪問都將使用非緩存內存屬性進行。這意味著指令獲取可能與同一核心或其他核心中的緩存不一致。軟件必須通過執行適當的緩存維護操作來考慮這一點。

L1指令緩存的維護

操作可以在任何時間發生,不受L1I$(禁用或啟用)的狀態限制。

相關信息

請參考第45頁的"5.4.5 調試恢復模式"。

7.2 L1 instruction cache Speculative memory accesses ? ?//L1指令緩存的推測性內存訪問

指令獲取是有推測性質的,流水線中可能存在多個未解決的分支。代碼流中的分支指令或異常可能導致流水線刷新,丟棄當前已獲取的指令。在指令獲取中,具有設備內存類型屬性的頁面被視為非緩存正常內存。

設備內存頁面必須使用翻譯表描述符屬性位eXecute Never (XN)進行標記。設備和代碼地址空間必須在物理內存映射中分離。這種分離可以防止在地址轉換被禁用時進行推測性獲取敏感設備的操作。

如果啟用了L1指令緩存,并且指令獲取在L1指令緩存中未命中,它們仍然可以在L1數據緩存中查找。然而,無論數據緩存是否啟用,該查找都不會導致L1數據緩存重新填充。只有在啟用L1指令緩存的情況下,才會在L2緩存中分配該行。

7.3 Program flow prediction

Cortex?-A715核心包含程序流預測硬件,也稱為分支預測。分支預測可以提高整體性能并增強功耗效率。除非當前異常級別下的內存管理單元(MMU)被禁用,否則程序流預測始終處于啟用狀態。如果禁用了程序流預測,則所有taken(被執行)的分支都會產生與清理流水線相關的懲罰。如果啟用了程序流預測,則會預測條件分支或無條件分支是否被執行,具體如下:

- 對于條件分支,它會預測該分支是否被執行以及分支轉到的地址,即分支目標地址。

- 對于無條件分支,它只會預測分支的目標地址。

程序流預測硬件包含以下功能:

- 分支目標緩沖區(BTB),保存先前執行的分支的目標地址。

- 分支預測器(BP),使用先前的分支歷史進行預測。

- 返回棧,包括嵌套子程序的返回地址。

- 靜態分支預測器。

- 間接分支預測器。

預測和非預測指令

程序流預測硬件會預測所有的分支指令,包括:

- 條件分支

- 無條件分支

- 與過程調用和返回指令相關的間接分支

異常返回分支指令不會進行預測。

返回棧

返回棧(return stack)存儲地址和指令集狀態。這個地址等于AArch64中X30寄存器(鏈接寄存器)的值。

下列指令會導致返回棧的壓棧操作:

- BL

- BLR

- BLRAA

- BLRAAX

- BLRAB

- BLRABZ

下列指令會導致返回棧的出棧操作:

- RET

- RETAA

- RETAB

以下指令不會進行預測,因為它們可以改變核心的特權模式和安全狀態:

- ERET

- ERETAA

- ERETAB

8. L1 data memory system

Cortex?-A715核心的L1數據存儲系統執行加載和存儲指令。它處理內存一致性請求以及特定的指令,例如原子操作、緩存維護操作和內存標記指令。L1數據存儲系統包括L1數據緩存和L1數據轉換后備緩沖器(TLB)。

以下表格展示了L1數據存儲系統的特性。

L1數據TLB也駐留在L1數據存儲系統中。然而,它是內存管理單元(MMU)的一部分,并在第51頁的「6. 內存管理」中描述。

8.1 L1 data cache behavior

L1數據緩存在復位時會自動失效,除非將核心電源模式初始化為調試恢復模式。

在調試恢復模式下,L1數據緩存不可用。

沒有針對整個數據緩存進行失效的操作。如果軟件需要此功能,那么必須通過迭代緩存幾何結構并執行一系列單獨的按集/路指令來構建它。DC CISW操作同時對目標集/路進行清除和失效。HCR_EL2.SWIO的值不起作用。有關DC CISW和HCR_EL2的更多信息,請參閱Arm? A-profile架構參考手冊。

當L1數據緩存禁用時的行為:

? 加載指令不會在L2或L3緩存中分配新的行。

? 對可緩存內存的所有加載和存儲指令均視為非可緩存。

? 數據緩存維護操作繼續正常執行。

L1數據緩存和L2緩存不能獨立禁用。當一個核心禁用了L1數據緩存后,由該核心發出的可緩存內存訪問不再緩存到L1或L2緩存中。但是,共享L2緩存的另一個核心仍然可以將數據緩存在其L1緩存和共享的L2緩存中。

為了保持多個核心之間的數據一致性,Cortex?-A715核心使用修改、排他、共享、失效(MESI)協議。

緩存索引的確定方式意味著物理地址(PA)和組號之間沒有直接關系。您不能使用假定PA和組號之間存在關系的目標化操作。

要刷新整個緩存,必須按照CCSIDR_EL1中描述的緩存的組數和路數執行集和路維護操作。該操作符合Armv8-A架構。

相關信息:

5.4.5 調試恢復模式 (第45頁)

8.2 Write streaming mode

Cortex?-A715核心支持寫流模式,有時也稱為讀分配模式,適用于L1和L2緩存。

在讀缺失或寫缺失時,緩存行會分配給L1或L2緩存。然而,寫入大塊數據可能會使緩存中充滿不必要的數據。當執行的線填充只是為了丟棄線填充數據時,這會浪費功耗和性能,因為整個緩存行會被后續的寫操作覆蓋(例如使用memset()或memcpy())。在某些情況下,寫操作不需要分配緩存行,比如執行C標準庫的memset()函數來將大塊內存清零。

為了防止不必要的緩存行分配,合并寫緩沖器(MWB)會檢測核心在線填充完成之前是否已經寫入了完整的緩存行。如果在可配置數量的連續線填充中檢測到這種情況,則MWB切換到寫流模式。進入寫流模式后,加載操作的行為正常,仍可能導致線填充。在寫流模式下,寫操作仍會查找緩存,但如果未命中,則會寫入L2或L3緩存,而不是開始線填充。

在MWB切換到寫流模式之前,可能會觀察到超過指定數量的線填充。

寫流模式將保持啟用,直到以下情況發生之一:

? 檢測到一個不完整的緩存行可緩存寫入突發。

? 有一個后續的加載操作與尚未完成的寫流目標相同。

當Cortex?-A715核心切換到寫流模式時,MWB會繼續監視總線流量。當它觀察到進一步數量的完整緩存行寫入時,它會向L2或L3緩存發出信號進入寫流模式。

寫流閾值定義了在存儲操作停止引起緩存分配之前,連續多少個緩存行將被完全寫入而沒有被讀取。您可以通過寫入寄存器A.1.15 IMP_CPUECTLR_EL1,即CPU擴展控制寄存器,來配置每個緩存(L1、L2和L3)的寫流閾值。

8.3 Instruction implementation in the L1 data memory system

Cortex?-A715核心支持Arm?v8.1-A架構中添加的原子指令。

對可緩存內存的原子指令可以作為近原子操作或遠原子操作執行,默認情況下,Cortex?-A715核心將這些指令作為近原子操作執行。

另外,可以對CPUECTLR進行編程,以根據系統行為,某些原子指令嘗試作為遠原子操作執行。

當作為遠原子操作執行時,原子操作傳遞給互連模塊執行。如果操作在集群內任何位置命中,或者互連模塊不支持原子操作,則L3內存系統執行原子操作。如果緩存行不存在,則將其分配到L3緩存中。

當啟用了精確檢查的內存標記擴展(MTE)時,所有經過檢查的原子操作都會在近處執行。

Cortex?-A715核心支持對設備或非緩存內存的原子操作,但這也取決于互連模塊是否支持原子操作。如果在互連模塊不支持原子操作的情況下執行此類原子指令,則會導致異常中止。

8.4 Internal exclusive monitor ? ?//內部獨占監視器

Cortex?-A715核心包含一個內部獨占監視器,具有2狀態(開放狀態和獨占狀態)的狀態機,用于管理Load-Exclusive和Store-Exclusive訪問以及Clear-Exclusive (CLREX)指令。

您可以使用這些指令構建信號量,確保在核心上運行的不同進程之間以及使用相同一致性內存位置的不同核心之間的同步。Load-Exclusive指令會為一小塊內存標記獨占訪問權。CTR_EL0將標記塊的大小定義為16個字,即一個緩存行。

Load-Exclusive或Store-Exclusive指令是以LDX、LDAX、STX或STLX開頭的指令助記符。

有關這些指令的更多信息,請參閱A-Profile架構的Arm? Architecture Reference Manual。

有關更多技術參考和寄存器信息,請參閱第312頁的A.4.23 CTR_EL0,緩存類型寄存器。

8.5 Data prefetching

數據預取在執行性能提升之前獲取數據。對于無法有效處理的情況,Cortex?-A715核心支持AArch64預取存儲器指令PRFM。

這些指令向內存系統發出信號,指示指定地址的內存訪問可能很快發生。內存系統采取措施以減少內存訪問的延遲。

PRFM指令在緩存中進行查找。如果緩存未命中且是可緩存地址,則開始進行線填充(linefill)。然而,當線填充開始時,PRFM指令已經完成,并且不會等待線填充完成。

有關預取內存和預加載緩存的更多信息,請參閱A-Profile架構的Arm? Architecture Reference Manual。

硬件數據預取器

加載/存儲單元包括負責生成針對L1、L2和L3緩存的預取的硬件預取引擎。具體而言,L1內存子系統中的預取引擎針對L1和L2緩存。L2內存子系統中的預取引擎針對L2和L3緩存。加載端的預取器使用虛擬地址(VA)和程序計數器(PC)。存儲端的預取器僅使用虛擬地址(VA)。

CPUECTLR寄存器允許對預取器行為的某些方面進行控制。有關更多信息,請參閱以下內容:

? 第159頁的A.1.15 IMP_CPUECTLR_EL1,CPU擴展控制寄存器

? 第167頁的A.1.16 IMP_CPUECTLR2_EL1,CPU擴展控制寄存器

數據緩存清零

在Cortex?-A715核心中,通過虛擬地址執行數據緩存清零(DC ZVA)指令可將內存中的一塊64字節區域(對齊到64字節)設置為零。

有關更多信息,請參閱A-Profile架構的Arm? Architecture Reference Manual。

9. L2 memory system

Cortex??A715核心的L2內存系統通過CPU橋將核心與DynamIQ?共享單元-110(DSU-110)連接在一起。它包括私有的L2緩存。

L2緩存是統一的,并且對于集群中的每個Cortex??A715核心都是私有的。 ? ?//L2是core私有的!!!

L2內存系統包括使用虛擬地址(VA)和程序計數器(PC)的數據預取引擎。不同的引擎能夠預取L2緩存和L3緩存中的數據。

以下表格顯示了L2內存系統的特性。

9.1 L2 cache

集成的L2緩存處理來自指令和數據方面的指令和數據請求,以及轉換表遍歷請求。

L1指令緩存和L2緩存是弱包容性(weakly inclusive)的。在L1指令緩存和L2緩存中未命中的指令獲取會分配兩個緩存,但是L2緩存的失效不會導致L1指令緩存的回寫無效(back-invalidate)。

L1數據緩存和L2緩存是嚴格排他的(strictly exclusive)。L1數據緩存中的任何數據都不會存在于L2緩存中。

除非核心電源模式初始化為調試恢復模式(Debug recovery mode),否則L2緩存會在復位時自動失效。

緩存索引的確定方式意味著物理地址(PA)與組號之間沒有直接關系。您不能使用假設PA和組號之間存在關系的目標操作。

要刷新整個緩存,您必須根據該緩存的CCSIDR_EL1描述執行組和路維護操作,操作數量等于集合數和路數。此操作符合Armv8-A架構規范。

相關信息

5.4.5 第45頁的調試恢復模式(Debug recovery mode)

9.2 Support for memory types

Cortex?-A715核心通過降級某些內存類型簡化一致性邏輯。

被標記為內部寫回高速緩存和外部寫回高速緩存的內存將被緩存在L1數據緩存和L2緩存中。

被標記為內部寫透模式的內存會被降級為不可緩存。

被標記為外部寫透模式或外部非緩存模式的內存會被降級為不可緩存,即使內部屬性為寫回高速緩存。

額外的屬性提示如下使用:

分配提示(Allocation hint)

分配提示有助于確定系統中新獲取行的分配規則。

瞬態提示(Transient hint)

所有設置了瞬態位的可緩存讀取和寫入會在L2緩存中進行分配。

對L1數據緩存進行的具有瞬態位設置的讀取會在L1緩存中進行分配。從L1緩存逐出的瞬態行不會在下游緩存中進行分配。

9.3 Transaction capabilities ? ?//事務能力

The CHI Issue E接口連接了Cortex?-A715核心的L2內存系統和DynamIQ?共享單元-110 (DSU-110),為核心提供了事務能力。

以下表格顯示了Cortex?-A715核心L2緩存的讀取、寫入、分布式虛擬內存(DVM)發出和嗅探能力的最大可能值。

請參考Arm?架構參考手冊中的A-profile架構部分,了解不同內存類型的信息。

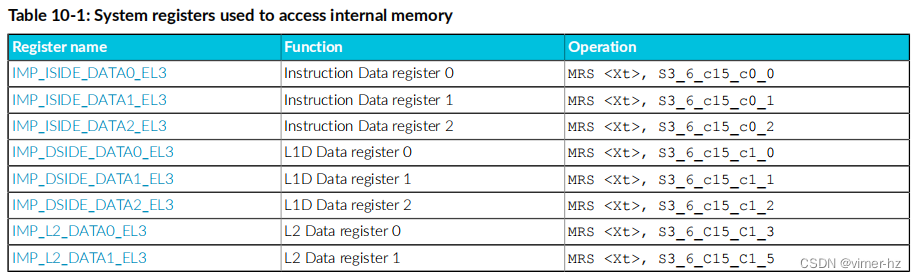

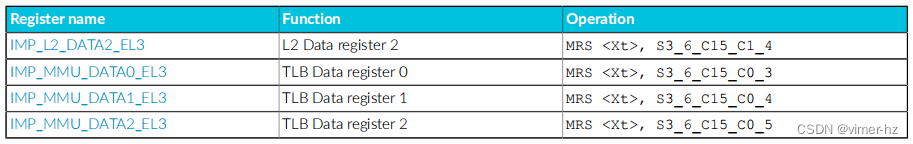

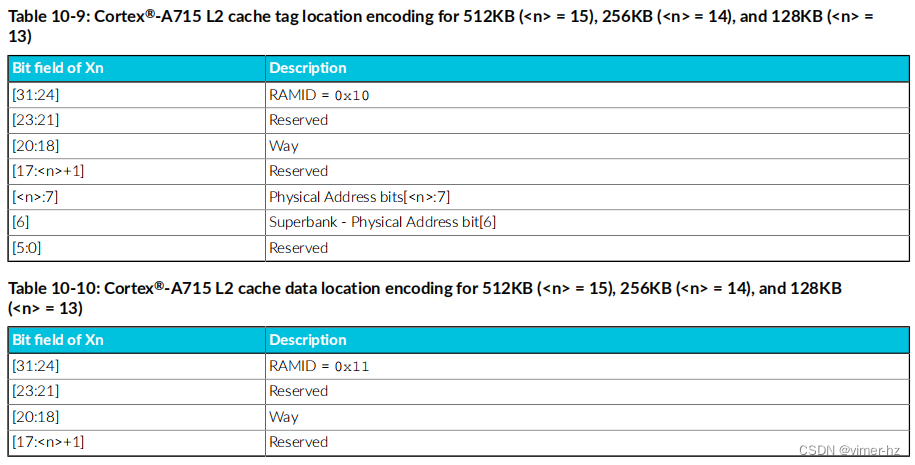

10. Direct access to internal memory

?Cortex?-A715核心通過IMPLEMENTATION DEFINED系統寄存器提供了一種讀取L1緩存、L2緩存和TLB結構所使用的內部內存的機制。當緩存數據與系統內存數據之間的一致性被破壞時,您可以使用這種機制來調查任何問題。

無法更新緩存或TLB結構的內容。

只有在EL3中才能直接訪問內部內存。在其他所有異常級別中,執行這些指令會導致未定義指令異常。

您可以使用表10-1中的十二個只讀(RO)系統寄存器來訪問內部內存的內容。通過使用以下SYS指令將內部內存選定為IMPLEMENTATION DEFINED RAMINDEX寄存器進行編程:

SYS #6, C15, C0, #0, <Xt>

有關RAMINDEX寄存器的更多信息,請參見第255頁的附錄A.3.1 RAMINDEX, RAMINDEX system instruction。數據從只讀系統寄存器中讀取,如下表所示。

- 所有系統寄存器均為只讀(RO)且寬度為64位。

- 有關寄存器復位值,請參閱各個位復位。

- 對數據寄存器的任何訪問都會返回數據。

- 單擊寄存器名稱以獲取返回數據格式的詳細信息。

10.1 L1 cache encodings

L1數據緩存和指令緩存都是4路組相聯的。

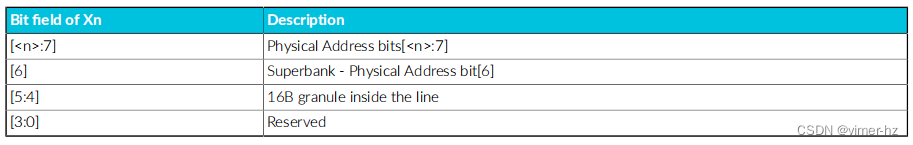

配置的緩存大小確定了每個組相聯方式中的組數。用于定位標簽和數據內存的緩存數據條目的編碼在適當的SYS指令中的Xn中設置。對于標簽和數據RAM訪問,它們的編碼是相似的。

//L1數據緩存和指令緩存都是4路組相聯的。具體解釋下:

L1數據緩存和指令緩存是處理器中的兩個關鍵組件,用于提高數據和指令的訪問速度。它們都采用了4路組相聯的設計。

"組相聯"指的是緩存中數據和指令條目的存儲方式。每個緩存被劃分為多個組,而每個組中又有多個條目。在4路組相聯的設計中,每個組內有4個條目。

當需要訪問緩存中的數據或指令時,處理器會使用特定的算法根據內存地址來確定數據所在的組。然后,它會在該組的4個條目中查找匹配的數據。

使用4路組相聯的設計可以提高緩存的命中率。當處理器需要讀取或寫入數據時,它首先會檢查該數據是否已經存在于緩存中。如果數據在緩存中被找到(即命中),處理器就可以更快地訪問數據,從而提高了系統性能。如果數據未命中,則需要從主存儲器中讀取或寫入數據,這需要更多的時間。

總之,L1數據緩存和指令緩存都采用了4路組相聯的設計,以提高數據和指令的訪問速度和系統性能。

以下表格顯示了定位和選擇給定緩存行所需的編碼:

10.1.1 L1 RAM returned data

對于每個寄存器,對L1 RAM的任何訪問都會返回數據。

點擊下表中的寄存器名稱以獲取返回數據格式的詳細信息。

10.2 L2 cache encodings

L2緩存是8路組相聯的。

配置的緩存大小確定了每個組相聯方式中的組數。用于定位標簽和數據內存的緩存數據條目的編碼在適當的SYS指令中的Xn中設置。對于標簽和數據RAM訪問,它們的編碼是相似的。

以下表格顯示了定位和選擇給定緩存行所需的編碼:

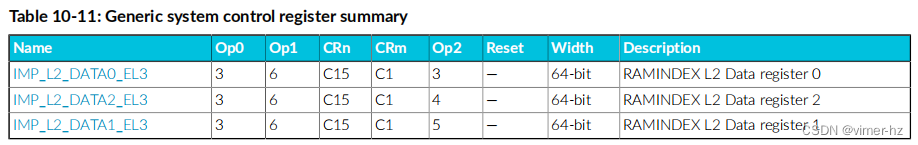

10.2.1 L2 RAM returned data

對于每個寄存器,對L2 RAM的任何訪問都會返回數據。

點擊下表中的寄存器名稱以獲取返回數據格式的詳細信息。

10.3 L2 TLB encodings

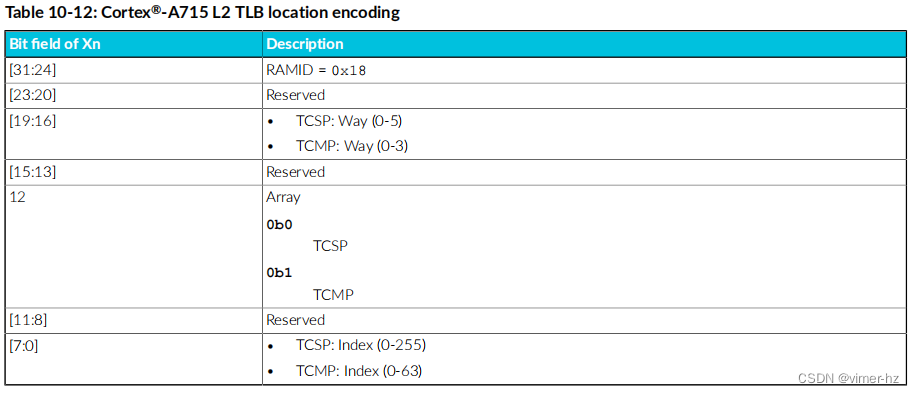

L2 TLB RAM中的小頁面(TCSP)采用6路組相聯方式,中等頁面(TCMP)采用4路組相聯方式。

以下表格顯示了定位和選擇給定緩存行所需的編碼:

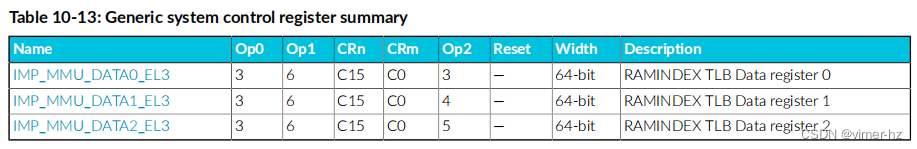

10.3.1 L2 TLB RAM returned data

對于每個寄存器,對L2 TLB RAM的任何訪問都會返回數據。

點擊下表中的寄存器名稱以獲取返回數據格式的詳細信息。

11. RAS Extension support

Cortex??A715核心支持可靠性、可用性和可服務性(RAS)v1.1擴展,但不支持可選的RAS時間戳擴展。

具體而言,Cortex??A715核心支持以下RAS擴展功能:

? 對包含臟數據的功能性RAM進行單錯誤糾正、雙錯誤檢測(SECDED)和錯誤糾正碼(ECC)的緩存保護。包括L1數據標簽和數據、L2標簽和數據以及L2事務隊列(TQ)RAM。

? 對只包含干凈數據的功能性RAM進行單錯誤檢測(SED)奇偶校驗的緩存保護。包括L1指令標簽和數據緩存以及內存管理單元(MMU)RAM。

? 錯誤同步屏障(ESB)指令。當執行ESB指令時,核心確保在ESB之前生成的所有SError中斷要么由核心接收,要么掛起在DISR_EL1中。

? 總線傳輸中的毒屬性。

? 錯誤數據記錄寄存器。

? 錯誤處理中斷(FHI)。

? 錯誤恢復中斷(ERI)。

? 錯誤注入。

Cortex??A715核心具有以下節點:

? 節點0,包括DynamIQ? Shared Unit-110(DSU-110)中的共享L3內存系統。

? 節點1,包括核心中的私有L1和L2內存系統。

有關架構RAS擴展和節點定義的更多信息,請參閱Arm? Reliability, Availability, and Serviceability (RAS) Specification Armv8,針對Armv8-A架構配置文件。

有關包含共享L3內存系統的節點的信息,請參閱Arm? DynamIQ? Shared Unit-110 Technical Reference Manual中的RAS擴展支持部分。

11.1 Cache protection behavior

在Cortex??A715核心中,可靠性、可用性和可服務性(RAS)擴展的配置包括緩存保護。在這種情況下,Cortex??A715核心可以防止RAM位單元保存錯誤值而導致的錯誤。

Cortex??A715核心中的RAM具有以下功能:

SED奇偶校驗

單錯誤檢測(SED)。一個奇偶校驗位適用于整個字。字的大小對于每個RAM都是特定的,并且取決于保護顆粒。

SECDED糾錯碼

單錯誤糾正、雙錯誤檢測(SECDED),錯誤糾正碼(ECC)。字的大小對于每個RAM都是特定的,并且取決于保護顆粒。

以下表格顯示了每個RAM應用的保護類型。當任何RAM中有單個位錯誤時,核心可以繼續進行并保持功能上的正確性。

如果不同的RAM或同一RAM內的不同保護顆粒存在多個單位錯誤,核心也可以保持功能上的正確性。

如果在同一保護顆粒內的單個RAM中存在雙位錯誤,則行為取決于RAM:

? 對于具有SECDED功能的RAM,核心會檢測并報告或推遲錯誤。如果錯誤出現在包含臟數據的緩存行中,則可能丟失該數據。

? 對于僅具有SED的RAM,核心無法檢測到雙位錯誤。這可能導致數據損壞。

如果在同一保護顆粒內有三個或更多位錯誤,核心可能會或可能不會檢測到這些錯誤。它是否檢測到錯誤取決于RAM和錯誤在RAM內的位置。當沒有錯誤時,核心的緩存保護功能對性能的影響很小。

11.2 Error containment ? ?//錯誤隔離

Cortex?-A715核心支持數據錯誤的錯誤隔離。這意味著檢測到的數據錯誤不會靜默傳播。使用數據污染來延遲數據錯誤,確保使用者知道錯誤的存在。無法糾正的L1數據緩存標簽錯誤和L2緩存標簽錯誤無法被隔離。

錯誤隔離還意味著在替換時,如果存在雙重錯誤,支持對所關聯數據進行污染,以確保在使用時報告相關數據的錯誤。

該核心還支持錯誤同步屏障(Error Synchronization Barrier,ESB)指令,進一步隔離在使用污染數據時報告的不精確異常。

11.3 Fault detection and reporting

當Cortex?-A715核心檢測到故障時,通過故障或錯誤信號引發Fault Handling Interrupt (FHI)異常或Error Recovery Interrupt (ERI)異常。FHIs和ERIs會在可靠性、可用性和可維護性(RAS)寄存器中反映,這些寄存器會在檢測到錯誤的節點中更新。核心節點錯誤使用nCOREFAULTIRQ進行報告。

未糾正的故障

當ERR1CTLR.FI被設置時,所有由核心n檢測到的延遲錯誤和未糾正錯誤都會通過nFAULTIRQ[n+1]信號生成一個FHI。

當ERR1CTLR.CFI或任何其他CE計數器溢出位被設置時,所有檢測到的已糾正錯誤也會導致生成一個FHI。

未糾正的中斷

當ERR1CTLR.UI被設置時,核心n檢測到的所有未推遲的未糾正錯誤都會在nCOREERRIQ信號上生成一個錯誤恢復中斷。

清除報告的故障

nFAULTIRQ [n+1]和nERRIRQ [n+1]信號必須保持激活狀態,直到軟件通過寫入ERR1STATUS寄存器來清除它們。

11.4 Error detection and reporting

當Cortex?-A715核心發生錯誤時,根據錯誤類型會引發不同的異常。

Cortex?-A715核心可能引發以下異常:

- 同步外部中止(Synchronous External Abort,SEA)

- 異步外部中止(Asynchronous External Abort,AEA)

- 錯誤恢復中斷(Error Recovery Interrupt,ERI)

錯誤檢測和報告寄存器:

以下寄存器用于錯誤處理和報告:

- 錯誤記錄特征寄存器(Error Record Feature Registers,ERR1FR)。這些只讀寄存器指定各種錯誤記錄設置。

- 錯誤記錄控制寄存器(Error Record Control Registers,ERR1CTLR)。這些寄存器用于啟用錯誤報告,并啟用與錯誤和故障相關的各種中斷。

- 錯誤記錄雜項寄存器(Error Record Miscellaneous Registers,ERR1MISC0-3)。這些寄存器記錄錯誤位置和計數的詳細信息。

- 偽故障生成特征寄存器(Pseudo-fault Generation Feature register,ERR1PFGF)。這個只讀寄存器指定各種錯誤設置。

11.4.1 Error reporting and performance monitoring

所有檢測到的內存錯誤,包括糾錯碼(ECC)錯誤或奇偶校驗錯誤,都會觸發"MEMORY_ERROR"事件。

如果選擇了"MEMORY_ERROR"事件并且計數器已啟用,則性能監視單元(Performance Monitoring Unit,PMU)計數該事件。

在安全狀態下,只有當MDCR_EL3.SPME被斷言時,才會計數該事件。關于MDCR_EL3的詳細信息,請參閱Arm? A-profile架構參考手冊。

相關信息

可以在《Arm? Architecture Reference Manual for A-profile architecture》的第98頁中找到,其中描述了性能監視器事件。

11.5 Error injection ? ?//錯誤注入

錯誤注入(Error injection)是指在錯誤檢測邏輯中插入錯誤,以驗證錯誤處理軟件的功能。

錯誤注入使用錯誤檢測和報告寄存器來插入錯誤。Cortex?-A715核心可以注入以下類型的錯誤:

修正的錯誤

單個糾錯碼(ECC)錯誤在L1數據緩存訪問時會生成一個修正錯誤(CE)。

延遲的錯誤

當從L1緩存驅逐一個緩存行到L2緩存時發生雙重ECC錯誤,或者在對L1緩存進行探測時產生延遲錯誤(DE)。

無法控制的錯誤

當L1標簽RAM或隨后發生驅逐的L2標簽RAM出現雙重ECC錯誤時,會生成無法控制的錯誤(UC)。

錯誤可以立即注入,也可以在一個32位計數器達到零時注入。您可以通過錯誤偽故障生成倒計時寄存器(ERR1PFGCDN)控制計數器的值。計數器的值按每個時鐘周期遞減。有關ERR1PFGCDN的更多信息,請參閱《Arm?可靠性、可用性和可維護性(RAS)規范Armv8》,了解Armv8-A架構配置文件的更多信息。

錯誤注入是系統中的一個獨立的錯誤源,不會創建硬件故障。

11.6 AArch64 RAS registers

摘要表提供了核心中實現定義的RAS寄存器的概覽。要了解有關寄存器的更多信息,請在表格中單擊寄存器名稱。

對于沒有列出復位值的寄存器,請參考注冊表描述頁面或Arm ARM中記錄的各個字段復位信息。

12. Utility bus

?實用總線(utility bus)提供對DynamIQ? 共享單元-110(DSU-110)中各個系統組件的控制寄存器的訪問,以及DSU-110 DynamIQ? 集群內核心的控制寄存器。實用總線被實現為一個64位的AMBA AXI5從設備端口,并且控制寄存器被內存映射到實用總線上。

在Cortex?-A715核心中,實用總線提供對以下系統功能的訪問:

? 核心中的活動監視器單元(AMU)寄存器

? 核心中的最大功率緩解機制(MPMM)寄存器

有關集群中核心的PPU寄存器的信息,請參閱Arm? DynamIQ? 共享單元-110 技術參考手冊。對于實用總線訪問的所有其他寄存器,請參閱Arm? DynamIQ? 共享單元-110 技術參考手冊中的實用總線章節。

12.1 Base addresses for system components

系統寄存器的每組都在單獨的64KB頁面邊界上進行分組,以便通過內存管理單元(MMU)強制執行訪問。

以下表格顯示了每組系統組件寄存器的基地址及其應該從何種安全狀態進行訪問:

? 核心AMU和MPMM寄存器的每組寄存器的基地址取決于核心實例編號 <n>,從 0 到總核心數減一。

? 在下表中,任何未記錄的地址空間視為RAZ/WI(保留為零/寫入無效)。

? 下表中的基地址是通過實用總線接口訪問的地址。系統互連通常將這些地址映射到特定的地址范圍上,根據系統地址映射來確定。因此,軟件必須將此處列出的基地址加上系統地址范圍基址,以獲得寄存器的絕對物理地址。

13. GIC CPU interface

通用中斷控制器(GIC)支持和控制中斷。GIC Distributor 通過 GIC CPU 接口與 Cortex?-A715 核心連接。GIC CPU 接口包括用于屏蔽、識別和控制轉發到核心的中斷狀態的寄存器。

DSU-110 DynamIQ? 集群中的每個核心都有一個 GIC CPU 接口,它連接到一個共同的外部分發器組件。

在 Cortex?-A715 核心中實現的 GICv4.1 架構支持:

? 兩個安全狀態

? 安全虛擬化

? 軟件生成的中斷(SGI)

? 基于消息的中斷

? CPU 接口的系統寄存器訪問

? 中斷屏蔽和優先級設置

? 集群環境,包括包含超過八個核心的系統

? 電源管理環境中的喚醒事件

GIC 包括中斷分組功能,支持:

? 將每個中斷配置為屬于 Group 0 或 Group 1,其中 Group 0 中斷始終為安全中斷

? 使用 IRQ 或 FIQ 異常請求將 Group 1 中斷傳遞給目標核心。Group 1 中斷可以是安全或非安全中斷

? 只使用 FIQ 異常請求將 Group 0 中斷傳遞給目標核心

? 統一的方案處理 Group 0 和 Group 1 中斷的優先級

有關中斷組的更多信息,請參閱 Arm? Generic Interrupt Controller Architecture Specification,GIC 架構版本 3 和版本 4。

13.1 Disable the GIC CPU interface

Cortex?-A715 核心始終包含通用中斷控制器(GIC)CPU接口。但是,您可以禁用它以滿足您的需求。

要禁用 GIC CPU 接口,在復位時將 GICCDISABLE 信號置為高電平。如果以這種方式禁用它,則可以使用外部的 GIC IP 驅動中斷信號(nFIQ、nIRQ)。如果在系統中未將 Cortex?-A715 核心集成到外部 GIC 中斷分發器組件(最小 GICv3 架構),則必須禁用 GIC CPU 接口。

如果禁用了 GIC CPU 接口,則:

? 虛擬輸入信號 nVIRQ 和 nVFIQ 以及輸入信號 nIRQ 和 nFIQ 可以由 SoC 中的外部 GIC 驅動。

? GIC 系統寄存器訪問會生成 UNDEFINED 指令異常。

如果啟用了 GIC CPU 接口,則必須將 nVIRQ 和 nVFIQ 綁定為高電平。這是因為 GIC CPU 接口會向核心生成虛擬中斷信號。而 nIRQ 和 nFIQ 信號由軟件控制,因此不需要將它們綁定為高電平。

有關這些信號的更多信息,請參閱 Arm? DynamIQ? Shared Unit-110 Configuration and Integration Manual 中的功能集成部分。

13.2 AArch64 GIC system registers

總結表格提供了核心中實現定義的 GIC 系統寄存器的概述。要獲取有關寄存器的更多信息,請在表格中單擊寄存器名稱。對于未列出復位值的寄存器,請參考寄存器描述頁面或 Arm ARM(架構參考手冊)中記錄的各個字段復位。

14. Advanced SIMD and floating-point support

Cortex?-A715核心支持A64指令集中的高級SIMD和標量浮點指令,而無需進行浮點異常捕獲。

Cortex?-A715核心浮點實現包括Arm?v8.5-A的功能。BFloat16浮點和Int8矩陣乘法是這些支持的功能之一。

Cortex?-A715核心在硬件中實現了所有操作,支持以下各種組合:

? 舍入模式

? 清零模式

? 默認非數字(NaN)模式

15. Scalable Vector Extensions support

Cortex?-A715核心支持可擴展向量擴展(SVE)和可擴展向量擴展2(SVE2)。SVE和SVE2是對AArch64高級SIMD和浮點功能的補充,而不是替代品。

SVE是由Armv8.2架構引入的可選擴展。SVE提供的向量指令主要支持比Arm Advanced SIMD指令集更寬的向量。Cortex?-A715核心實現了128位的可擴展向量長度。

SVE引入的所有功能和附加內容都在《Arm?體系結構參考手冊增補》中進行了描述,即《可擴展向量擴展》一書中。

16. System control

系統寄存器控制和提供核心實現的功能的狀態信息。

系統寄存器的主要功能包括:

? 系統性能監控

? 緩存配置和管理

? 整體系統控制和配置

? 內存管理單元(MMU)的配置和管理

? 通用中斷控制器(GIC)的配置和管理

系統寄存器可以在AArch64執行狀態的EL0到EL3中訪問。其中一些系統寄存器可以通過外部調試接口或實用總線接口進行訪問。

17. Debug

DSU-110 DynamIQ?集群提供了一種支持自托管和外部調試的調試系統。它具有一個外部的DebugBlock組件,并集成了各種CoreSight調試相關組件。

CoreSight調試相關組件分為兩組,其中一些組件位于DynamIQ?集群中,另一些組件位于單獨的DebugBlock中。

DebugBlock是DSU-110中的專用調試組件,與集群分離。DebugBlock在單獨的電源域內運行,可以在核心和DynamIQ?集群同時關閉電源時保持與調試器的連接。

集群和DebugBlock之間的連接由一對高級外設總線APB接口組成,各自向一個方向進行數據傳輸。除了認證接口外,所有調試流量都通過該接口進行讀取或寫入APB事務。這些調試流量包括寄存器讀取、寄存器寫入和交叉觸發接口(CTI)觸發。

調試系統實現了以下CoreSight調試組件:

? 集成到CoreSight子系統中的每個核心跟蹤單元。

? 包含在DebugBlock中的每個核心CTI。

? 交叉觸發矩陣(CTM)

? 由AMBA? APB接口提供的DebugBlock的調試控制

下圖展示了如何在DynamIQ?集群中實現調試系統。

DebugBlock上的主要調試APB接口控制調試組件。在將請求發送到DebugBlock或DynamIQ?集群中的適當組件之前,APB解碼器會對該總線上的請求進行解碼。每個核心的CTI都連接到CTM。

每個核心都包含一個調試組件,調試APB總線可以訪問這些組件。這些核心支持通過DebugBlock中的模塊進行斷電調試,這些模塊反映了關鍵核心信息。這些模塊允許在核心斷電時訪問斷電調試的CoreSight?寄存器。

每個核心中的跟蹤單元輸出跟蹤數據,這些數據在DynamIQ?集群中匯聚到一個單獨的AMBA? 4 ATBv1.1接口。

關于DynamIQ?集群調試組件的更多信息,請參閱《Arm? DynamIQ? Shared Unit-110 Technical Reference Manual》中的“調試(Debug)”部分。

Cortex?-A715核心還支持對內部存儲器的直接訪問,即緩存調試。直接訪問內部存儲器允許軟件讀取L1和L2緩存以及轉譯查找緩沖器(TLB)結構使用的內部存儲器。有關更多信息,請參閱第71頁上的"10. Direct access to internal memory"。

17.1 Supported debug methods

DSU-110 DynamIQ?集群及其相關核心是支持自托管和外部調試的調試系統的一部分。

下圖展示了一個典型的外部調試系統。

調試主機

一臺計算機,例如個人電腦,上運行著諸如Arm?調試器之類的軟件調試器。您可以使用調試主機發出高級命令。例如,您可以在特定位置設置斷點或檢查內存地址的內容。

協議轉換器

調試主機使用諸如以太網之類的接口向調試目標發送消息。然而,調試目標通常實現了不同的接口協議。需要一個設備(例如DSTREAM)來在兩個協議之間進行轉換。

調試目標

系統的最底層實現了協議轉換器通過調試單元訪問的系統支持。對于基于DSU-110的設備,用于訪問調試單元的機制是基于CoreSight架構實現的。通過APB接口訪問DSU-110 DebugBlock,然后將調試訪問定向到DynamIQ?集群內的選定A715核心。調試目標的一個示例是具有測試芯片或帶有A715核心的硅芯片的開發系統。

調試單元

用于幫助調試運行在核心上的軟件:

? 基于核心的DSU-110和外部硬件。

? 操作系統。

? 應用軟件。

使用調試單元,您可以:

? 停止程序執行。

? 檢查和更改進程和協處理器狀態。

? 檢查和更改內存以及輸入或輸出外設的狀態。

? 重新啟動處理單元(PE)。

對于自托管調試,調試目標運行在DynamIQ?集群中的核心上運行的調試監視器軟件。這樣,它不需要昂貴的接口硬件來連接第二個主機計算機。

17.2 Debug register interfaces

Cortex?-A715核心實現了Arm?v9.0-A調試架構。它還支持Arm?v8.4-A調試架構和Arm?v8.3-A的斷電調試。

調試架構定義了一組調試寄存器。調試寄存器接口可以從在核心上運行的軟件或外部調試器中訪問這些寄存器。有關詳細信息,請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的調試章節。

相關信息

第50頁的5.7節中的斷電調試(Debug over powerdown)

17.2.1 Core interfaces

系統寄存器訪問允許Cortex?-A715核心直接訪問特定的調試寄存器。調試寄存器接口可以從在核心上運行的軟件或外部調試器中訪問這些寄存器。

對調試寄存器的訪問按如下方式進行劃分:

調試

此功能既基于系統寄存器又基于內存映射。您可以使用連接到DynamIQ?共享單元-110(DSU-110)的APB從屬端口訪問調試寄存器映射。

性能監測

此功能基于系統寄存器并進行內存映射。您可以使用連接到DSU的DebugBlock的APB從屬端口訪問性能監測寄存器。

跟蹤

此功能基于系統寄存器并進行內存映射。您可以使用連接到DSU的DebugBlock的APB從屬端口訪問跟蹤單元寄存器。

統計分析

此功能基于系統寄存器。

ELA寄存器

此功能進行內存映射。您可以使用連接到DSU的DebugBlock的APB從屬端口訪問嵌入式邏輯分析器(ELA)寄存器。

有關APB從屬端口接口的信息,請參閱Arm? DynamIQ? Shared Unit-110技術參考手冊中的接口部分。

17.2.2 Effects of resets on debug registers

core的complexporeset_n信號和complexreset_n信號會影響調試寄存器。

complexporeset_n信號對應一個冷復位,涵蓋了核心邏輯和集成調試功能的復位。這個信號會初始化核心邏輯,包括跟蹤單元、斷點、監視點邏輯、性能監測器和調試邏輯。

complexreset_n信號對應一個熱復位,涵蓋了核心邏輯的復位。這個信號會復位部分調試和性能監測器邏輯。

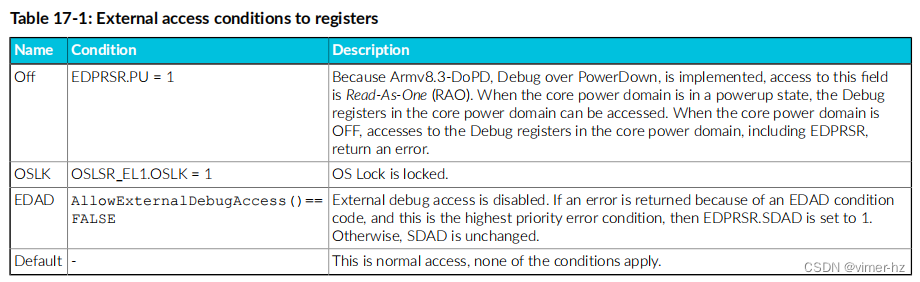

17.2.3 External access permissions to Debug registers

對Debug寄存器的外部訪問權限取決于訪問時的條件。

下表顯示了通過外部調試接口進行訪問時核心的響應:

17.2.4 Breakpoints and watchpoints

Cortex?-A715核心支持六個斷點(breakpoint)、四個監視點(watchpoint)和一個標準的調試通信通道(Debug Communications Channel,DCC)。

一個斷點由一個斷點控制寄存器和一個斷點值寄存器組成。這兩個寄存器被稱為斷點寄存器對(Breakpoint Register Pair,BRP)。其中四個斷點(BRP 0-3)僅匹配虛擬地址(Virtual Address,VA),另外兩個斷點(BRP 4和5)可以匹配虛擬地址(VA)、上下文ID(context ID)或虛擬機ID(Virtual Machine ID,VMID)。

你可以使用監視點來在程序訪問特定內存地址時停止目標執行。所有的監視點都可以連接到兩個斷點(BRP 4和5),以便在給定的進程上下文中捕獲內存請求。

17.3 Debug events

調試事件可以是軟件調試事件或停機調試事件。

Cortex?-A715核心對調試事件的響應有以下幾種方式:

- 忽略調試事件

- 拋出調試異常

- 進入調試狀態

在Cortex?-A715核心中,監視點調試事件始終是同步的。內存提示指令和緩存清除操作(除了DC ZVA和DC IVAC)不會生成監視點調試事件。存儲互斥指令即使在對互斥監視器控制檢查失敗時也會生成監視點調試事件。原子比較交換(CAS)指令即使在比較操作失敗時也會生成監視點調試事件。

冷復位(Cold reset)將設置調試操作系統鎖(Debug OS Lock)。為了使調試事件和調試寄存器訪問正常運行,必須清除調試操作系統鎖。

17.4 Debug memory map and debug signals

調試內存映射和調試信號在DSU-110 DynamIQ?集群級別進行處理。你可以參考《Arm? DynamIQ? Shared Unit-110 Technical Reference Manual》中的調試表和ROM表來了解更多信息。該手冊將提供關于如何處理調試內存映射和調試信號的詳細技術參考。

17.5 ROM table

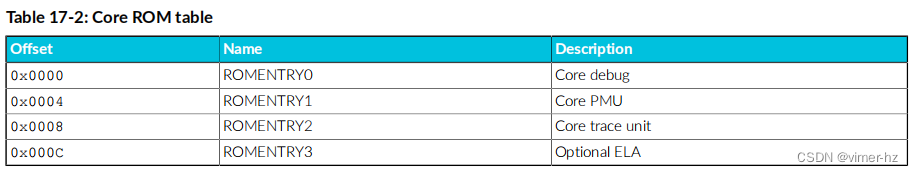

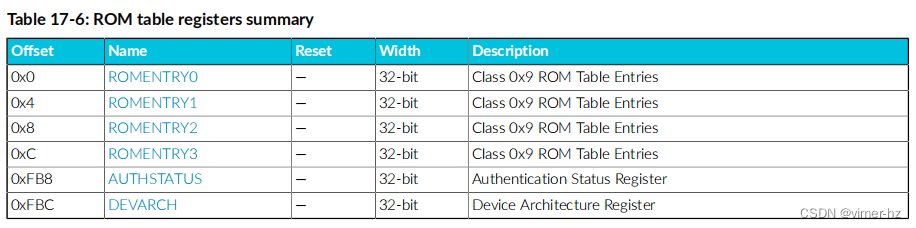

在Cortex??A715核心中,包含一個ROM表,其中列出了系統中的組件列表。調試器必須使用ROM表來確定實現了哪些CoreSight組件。ROM表是與CoreSight SoC一起用于系統調試的CoreSight調試相關組件,專為Cortex??A715核心設計。每個核心都有一個ROM表,并且ROM表符合Arm? CoreSight? Architecture Specification v3.0。

DynamIQ? Shared Unit-110 (DSU-110)具有自己的ROM表,一個用于集群(cluster),一個用于DebugBlock,并在集群ROM表中具有屬于每個核心的ROM表的入口點。詳細信息請參閱《Arm? DynamIQ? Shared Unit-110 Technical Reference Manual》中的ROM表部分。

Cortex??A715核心的ROM表包括以下條目:

Related information?

17.9 External ROM table registers on page 96

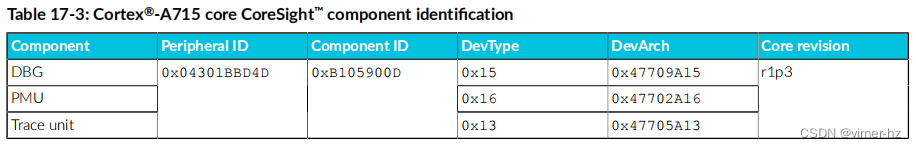

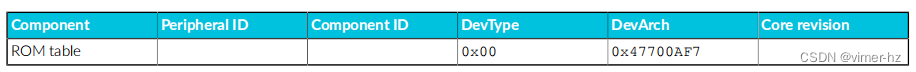

17.6 CoreSight? component identifification

與Cortex??A715核心相關的每個組件都有一組唯一的CoreSight? ID值。下表顯示了這些值。

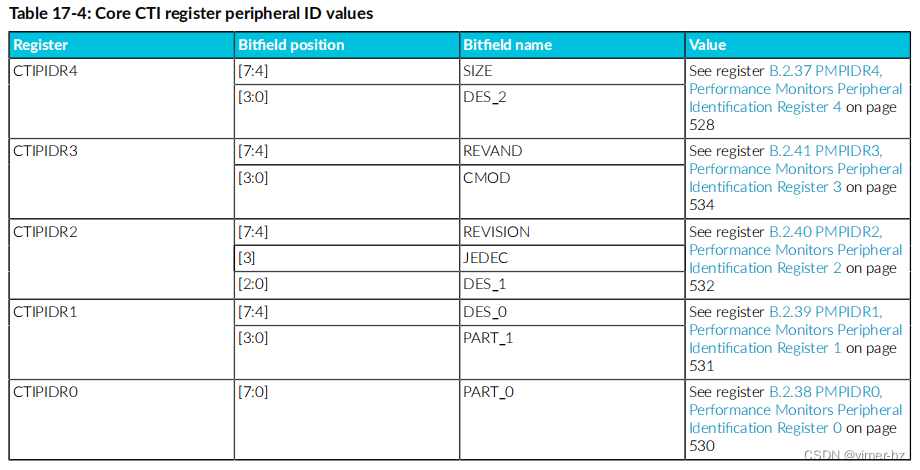

17.7 CTI register identifification values

Cortex??A715核心的Cross Trigger Interface (CTI)寄存器位于DSU-110的DebugBlock中。 有關集群和核心CTI寄存器的名稱和描述,請參閱《Arm? DynamIQ? Shared Unit-110 Configuration and Integration Manual》中的External CTI register summary。僅核心CTI寄存器的外設ID值與集群CTI寄存器的外設ID值不同。 下表顯示了核心CTI寄存器的外設ID值。

17.8 External Debug registers

該摘要表提供了核心中實現定義的內存映射調試寄存器的概述。要獲取有關寄存器的更多信息,請單擊表中的寄存器名稱。對于沒有列出復位值的寄存器,請參考寄存器描述頁中或Arm ARM中記錄的各個字段復位。

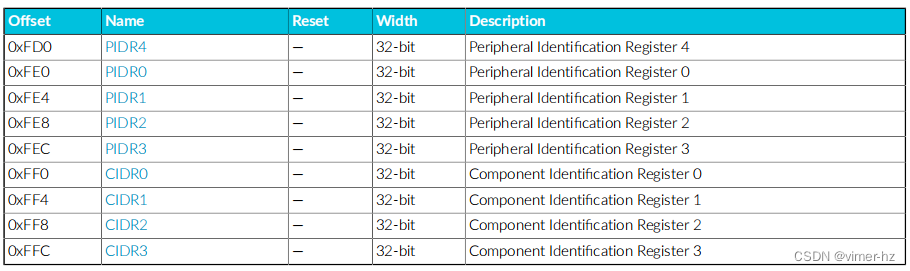

17.9 External ROM table registers

該摘要表提供了核心中實現定義的內存映射ROM表寄存器的概述。要獲取有關寄存器的更多信息,請單擊表中的寄存器名稱。對于沒有列出復位值的寄存器,請參考寄存器描述頁中或Arm ARM中記錄的各個字段復位。

18. Performance Monitors Extension support

Cortex??A715核心實現了性能監視擴展,包括Arm?v8.4-A和Arm?v8.5-A的性能監測特性。

Cortex??A715核心的性能監視單元(PMU)具有以下功能:

- 通過事件接口從設計中的其他單元收集事件。這些事件被用作事件計數器的觸發器。

- 通過性能監視控制寄存器支持周期計數器。

- 實現了PMU快照以進行上下文采樣。

- 提供六個或20個64位PMU計數器,可以計算核心中提供的任何事件。記錄的絕對計數可能因流水線效應而有所不同。除非計數器在很短的時間內啟用,否則這種變化對性能影響微乎其微。

您可以使用系統寄存器或外部調試APB接口來對PMU進行編程。

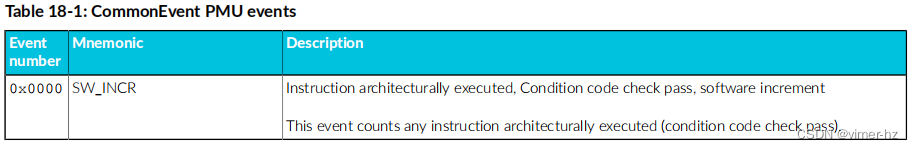

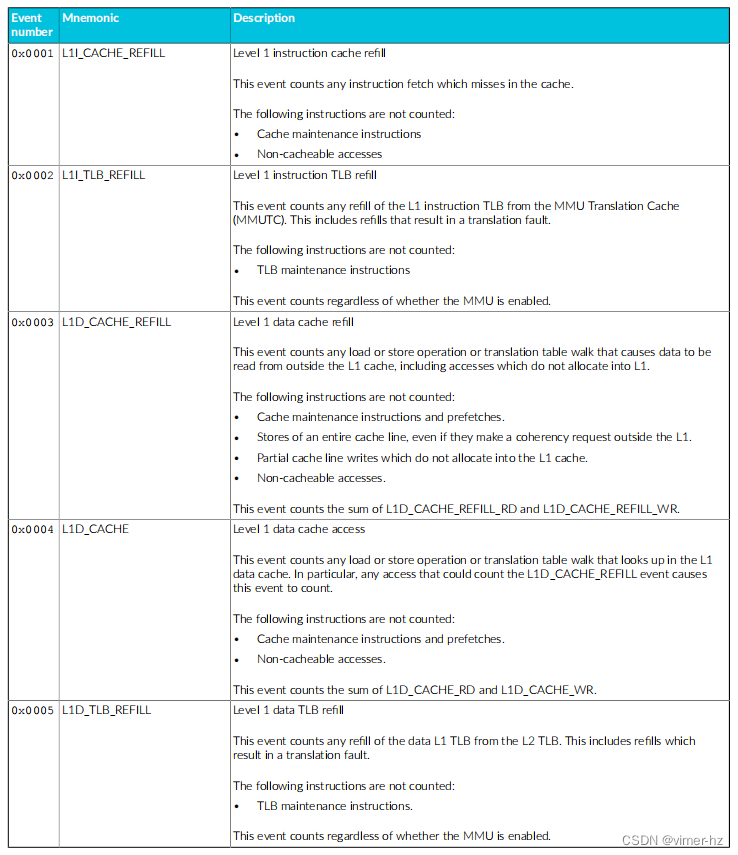

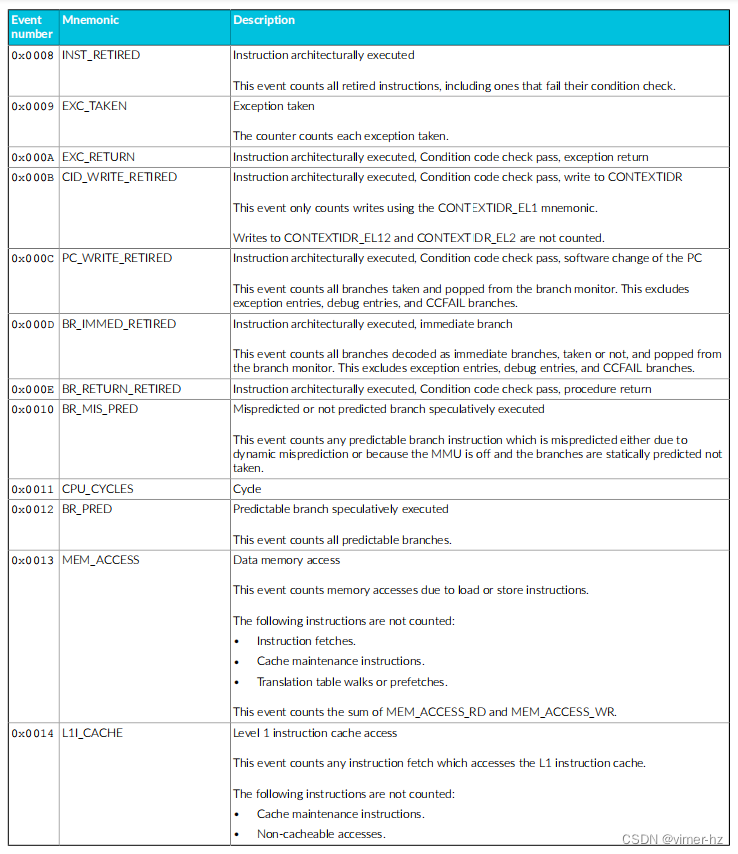

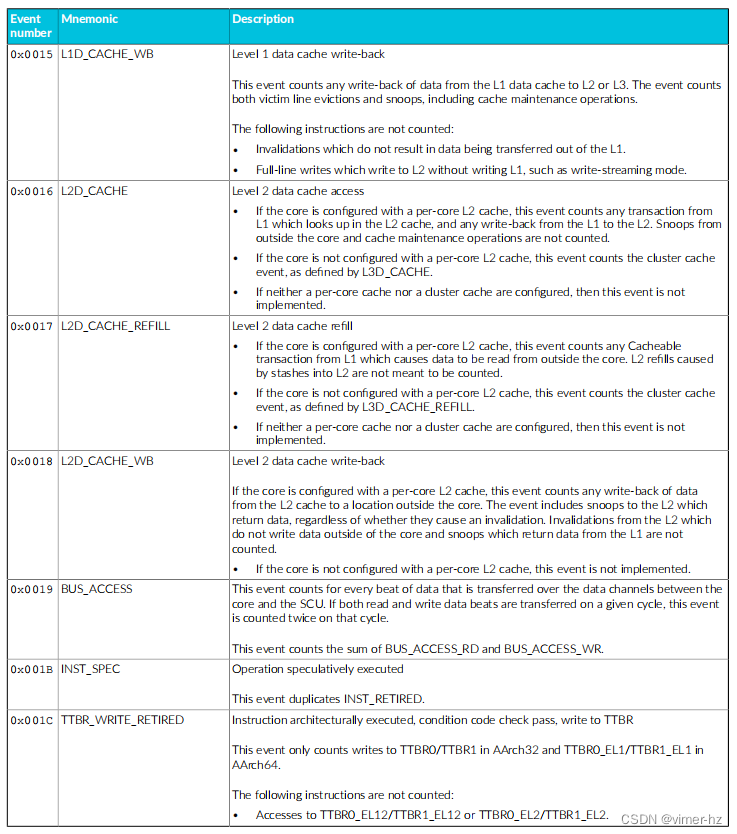

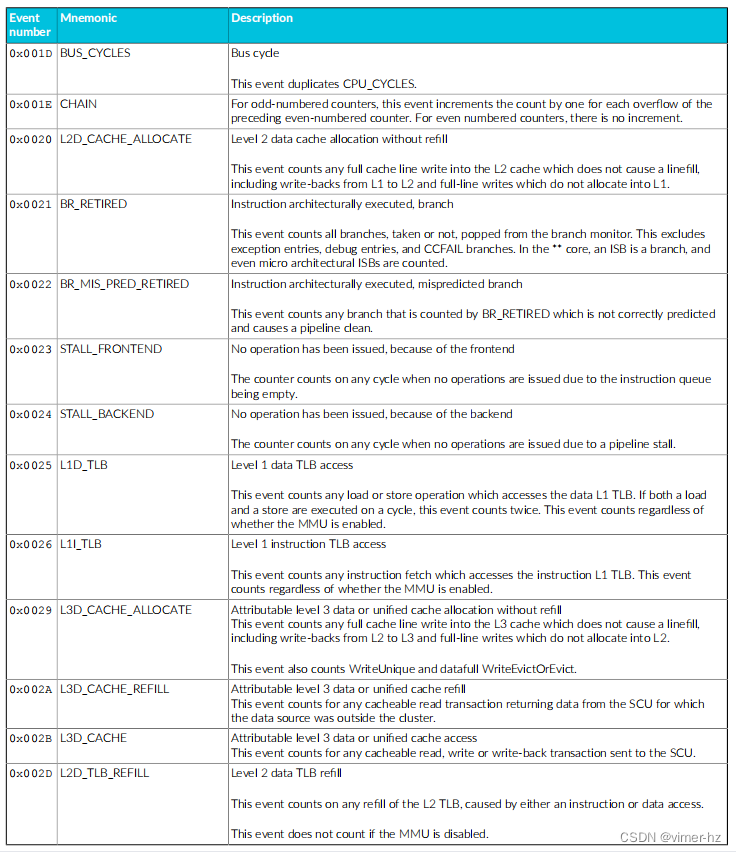

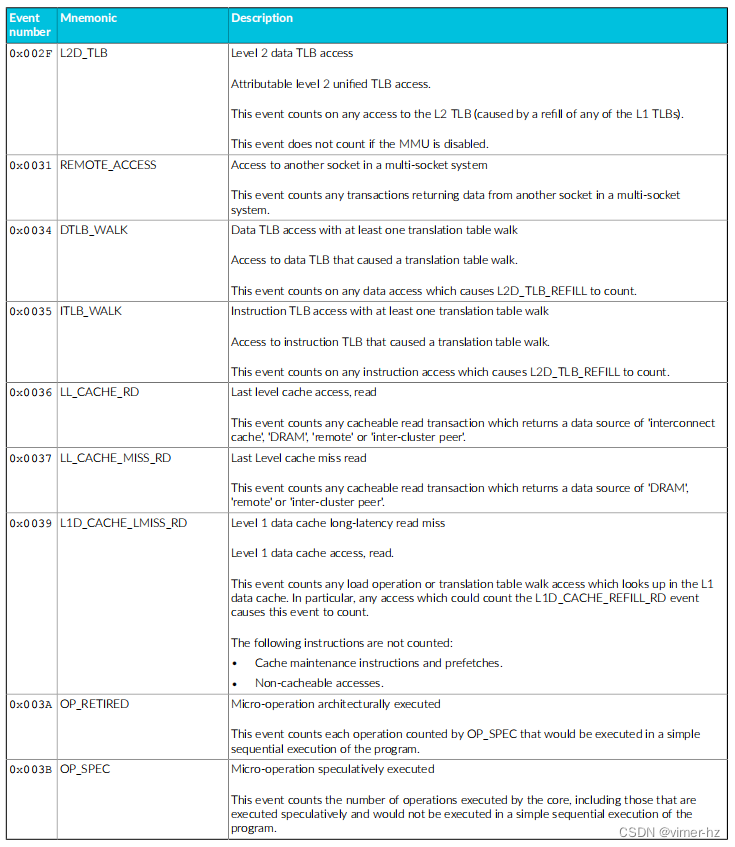

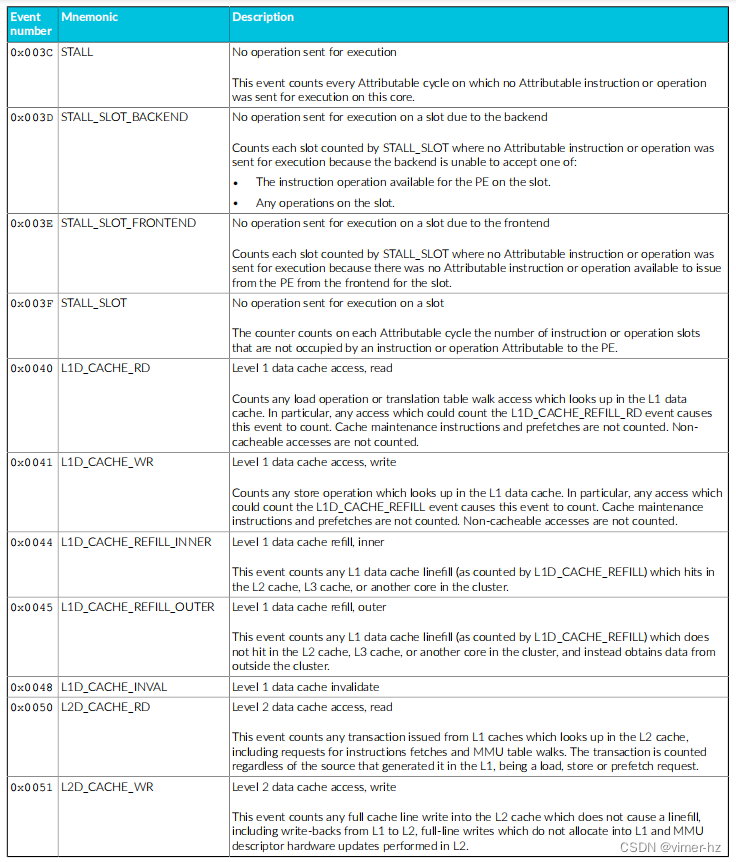

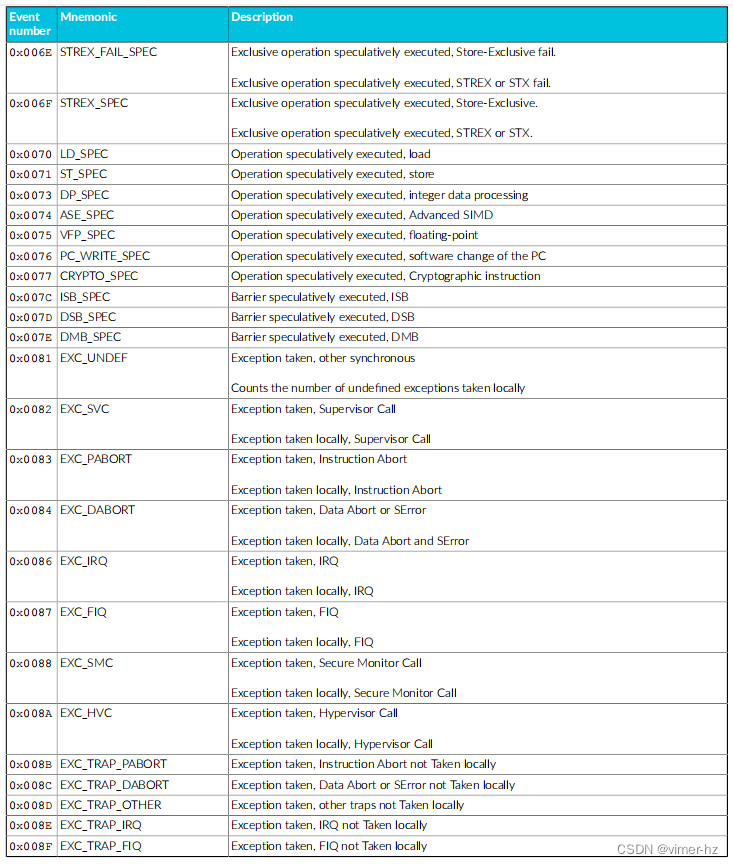

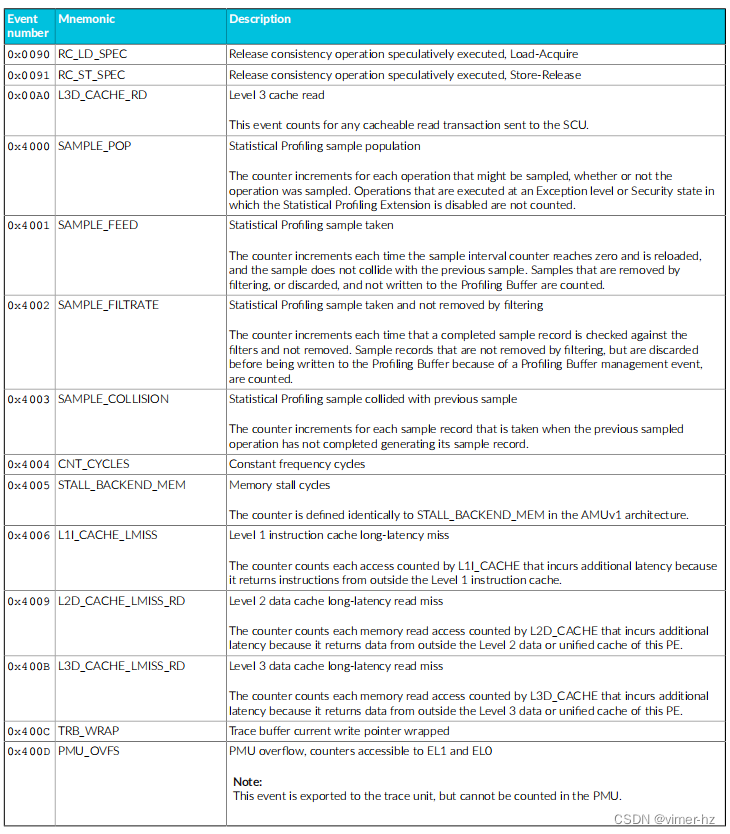

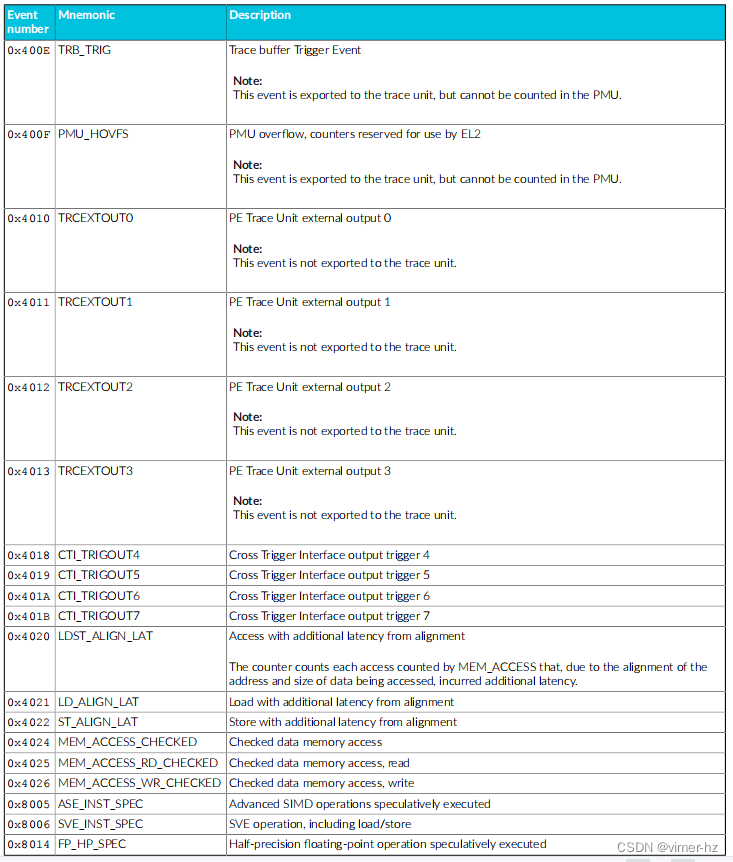

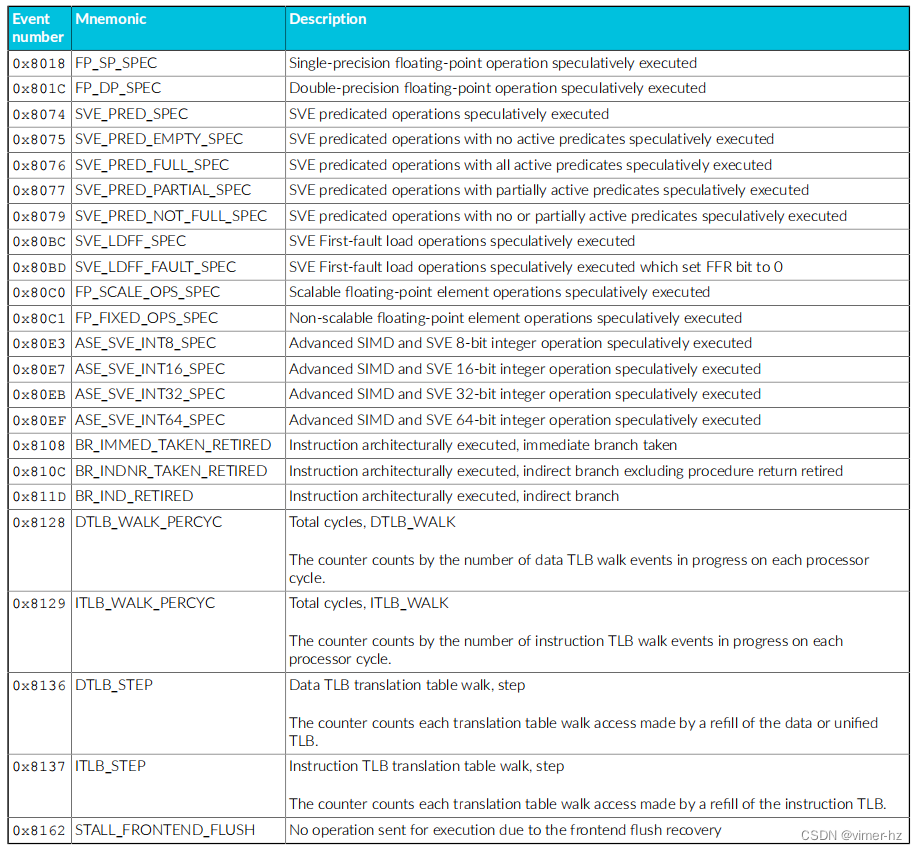

18.1 Performance monitors events

Cortex??A715核心的性能監視單元(PMU)從設計中的其他單元收集事件,并使用數字引用這些事件。

常見事件PMU事件 下表顯示了Cortex??A715核心生成的性能監視器事件以及PMU用于引用這些事件的數字。表中還顯示了每個事件在事件總線上的位位置。未列出的事件編號保留。 除非另有說明,否則這些事件中的每一個都可以導出到跟蹤單元,并根據Arm?嵌入式跟蹤擴展進行選擇。

18.2 Performance monitors interrupts

性能監視單元(PMU)可以配置為在一個或多個計數器溢出時生成中斷。

當PMU生成中斷時,nPMUIRQ[n]輸出將被拉低。

18.3 External register access permissions

Cortex??A715核心支持通過系統寄存器接口和內存映射接口訪問性能監視單元(PMU)寄存器。

對寄存器的訪問取決于:

- 核心是否已上電

- OS Lock的狀態

- 外部性能監視器訪問禁用的狀態

對于每個寄存器,其行為是特定的,并且不在本手冊中描述。有關這些特性及其對寄存器的影響的詳細說明,請參閱Arm? A-profile架構的《Arm?體系結構參考手冊》。本手冊提供的寄存器描述中說明了每個寄存器是讀/寫還是只讀。

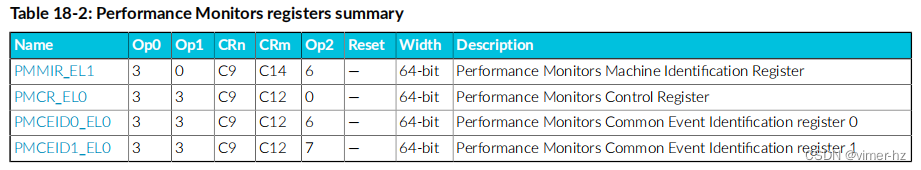

18.4 AArch64 Performance Monitors registers

總結表提供了核心中IMPLEMENTATION DEFINED性能監視器寄存器的概述。有關寄存器的更多信息,請單擊表中的寄存器名稱。

對于沒有列出重置值的寄存器,請參考寄存器描述頁或《Arm ARM》中記錄的各個字段重置值。

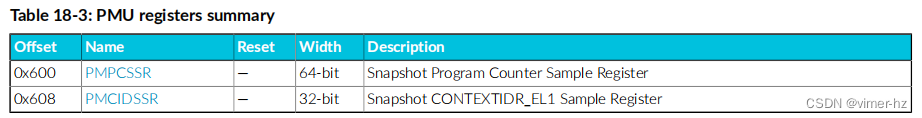

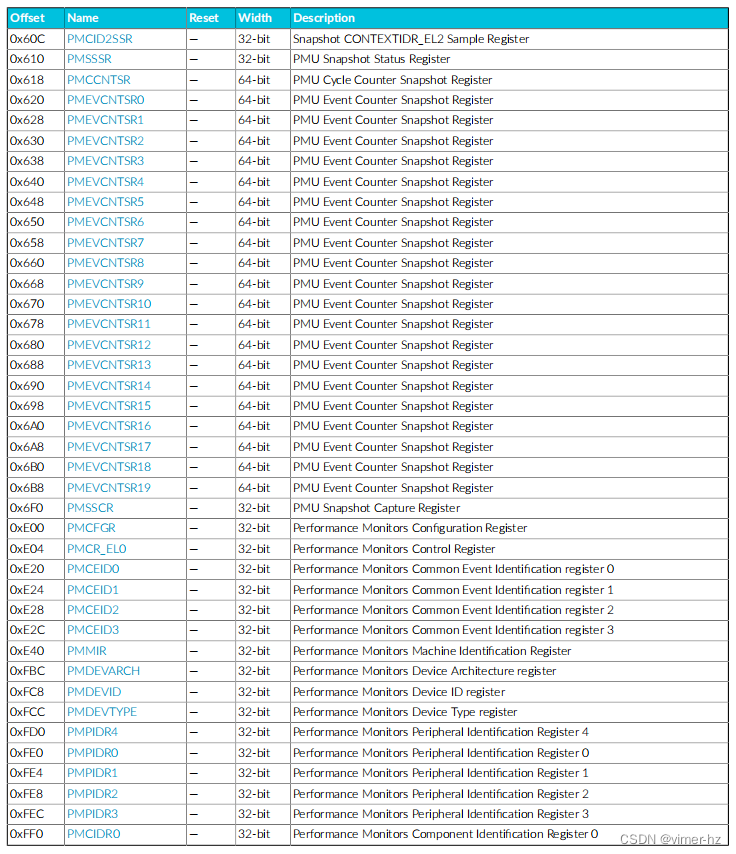

18.5 External PMU registers

總結表提供了核心中IMPLEMENTATION DEFINED的內存映射PMU寄存器的概述。有關寄存器的更多信息,請單擊表中的寄存器名稱。

對于沒有列出重置值的寄存器,請參考寄存器描述頁面或《Arm ARM》中記錄的各個字段重置。

19. Embedded Trace Extension support

Cortex??A715核心實現了嵌入式跟蹤擴展(ETE)。跟蹤單元基于ETE執行實時指令流跟蹤。跟蹤單元是CoreSight組件的一部分,是Arm實時調試解決方案的重要組成部分。

下圖顯示了跟蹤單元的主要組件:

核心接口

核心接口監視并生成P0元素,這些元素實質上是按程序順序執行的分支和異常跟蹤。

跟蹤生成

跟蹤生成邏輯根據P0元素生成各種跟蹤數據包。

過濾和觸發資源

您可以通過過濾來限制跟蹤單元生成的跟蹤數據量。例如,您可以將跟蹤生成限制在某個地址范圍內。跟蹤單元支持其他邏輯分析器風格的過濾選項。跟蹤單元還可以生成觸發信號,用于指示跟蹤捕獲設備停止捕獲跟蹤數據。

FIFO(先進先出緩沖區)

跟蹤單元以高度壓縮的形式生成跟蹤數據。先進先出(FIFO)緩沖區使得跟蹤數據可以被平滑輸出。當FIFO緩沖區已滿時,會發出溢出信號。在FIFO緩沖區被清空之前,跟蹤生成邏輯不會生成任何新的跟蹤數據。這種行為在調試器中查看時會導致跟蹤數據中的間斷。

跟蹤輸出

跟蹤數據從FIFO緩沖區輸出到AMBA ATB接口或跟蹤緩沖區。

有關更多信息,請參閱Arm? Architecture Reference Manual Supplement Armv9,適用于Armv9-A架構配置文件。

19.1 Trace unit resources

跟蹤資源包括計數器、外部輸入和輸出信號以及比較器。

下表顯示了跟蹤單元的資源,并指示A715核心跟蹤單元實現了哪些資源。

19.2 Trace unit generation options

Cortex?-A715核心跟蹤單元實現了一組生成選項。

下表顯示了跟蹤生成選項,并指示Cortex?-A715核心跟蹤單元實現了哪些選項。

19.3 Reset the trace unit

對于跟蹤緩沖區的復位與核心的冷復位是相同的。當使用跟蹤緩沖區擴展(TRBE)時,熱復位會禁用跟蹤緩沖區,因此無法使用跟蹤緩沖區來捕獲熱復位的跟蹤信息。

如果跟蹤單元被復位,那么跟蹤將停止直到重新編程和重新使能跟蹤單元。

然而,如果使用熱復位對核心進行復位,那么在復位之前由核心提供的最后幾條指令可能無法被跟蹤。

19.4 Program and read the trace unit registers

您可以使用Debug APB接口或系統寄存器接口來編程和讀取跟蹤單元寄存器。

在編程跟蹤單元寄存器時,核心不必處于調試狀態。當您編程跟蹤單元寄存器時,必須同時啟用所有更改。否則,如果您編程計數器,在正確設置觸發條件之前,它可能開始基于不正確的事件計數。要禁用跟蹤單元,請使用TRCPRGCTLR.EN位。有關以下寄存器的更多信息,請參閱Arm? Architecture Reference Manual Supplement Armv9,針對Armv9-A體系結構配置文件:

- Programming Control Register,TRCPRGCTLR

- Trace Status Register,TRCSTATR

以下圖表顯示了使用DebugBlock APB接口編程跟蹤單元寄存器的流程:

以下圖表顯示了使用系統寄存器接口編程跟蹤單元寄存器的流程:

19.5 Trace unit register interfaces

Cortex??A715核心支持一種APB內存映射接口和一種系統寄存器接口來訪問跟蹤單元寄存器。

根據跟蹤單元的狀態,寄存器訪問方式有所不同。請參閱Arm? Architecture Reference Manual Supplement Armv9,關于Armv9-A體系結構配置文件中的行為和訪問機制獲取更多信息。

19.6 Interaction with the Performance Monitoring Unit and Debug

跟蹤單元與性能監視單元(PMU)進行交互,并且可以訪問PMU事件。

與PMU的交互:

Cortex?-A715核心包括一個PMU,可以在一段時間內計數緩存失效和執行指令等事件。

PMU和跟蹤單元一起工作。

跟蹤單元使用PMU事件:

通過擴展輸入功能,PMU體系結構事件可供跟蹤單元使用。

跟蹤單元使用四個擴展外部輸入選擇器來訪問PMU事件。每個選擇器可以獨立選擇一個PMU事件,然后在相關事件發生的周期內激活。這些選定的事件可以由跟蹤單元內的任何事件寄存器訪問。

相關信息:

18. 第98頁的性能監視器擴展支持

18.1. 第98頁的性能監視器事件

19.7 ETE events

Cortex??A715核心的跟蹤單元從設計中的其他單元收集事件,并使用數字來引用這些事件。

除了第98頁上提到的性能監視器事件外,以下表格中列出的事件也被導出。由于我無法查看具體的表格內容,請您提供需要了解的事件列表,我將盡力提供相關信息。

19.8 AArch64 Trace unit registers

這個摘要表格提供了核心中的IMPLEMENTATION DEFINED跟蹤寄存器的概述。

要獲取有關寄存器的更多信息,請在表格中點擊寄存器名稱。

對于沒有列出復位值的寄存器,請參考寄存器描述頁面或Arm ARM中記錄的各個字段復位值。

19.9 External ETE registers

這個摘要表格提供了核心中的IMPLEMENTATION DEFINED內存映射ETE寄存器的概述。

要獲取有關寄存器的更多信息,請在表格中點擊寄存器名稱。

對于沒有列出復位值的寄存器,請參考寄存器描述頁面或Arm ARM中記錄的各個字段復位值。

20. Trace Buffer Extension support

Cortex??A715核心實現了Trace Buffer Extension (TRBE)。TRBE將跟蹤單元生成的程序流跟蹤直接寫入內存。TRBE通過系統寄存器進行編程。

當啟用TRBE時,它可以:

? 接收跟蹤單元的跟蹤數據并將其寫入L2內存。

? 丟棄來自跟蹤單元的跟蹤數據。在這種情況下,數據將會丟失。

? 拒絕來自跟蹤單元的跟蹤數據。在這種情況下,跟蹤單元會保留數據,直到TRBE接受為止。

當禁用TRBE時,TRBE將忽略跟蹤數據,跟蹤單元將跟蹤數據發送到AMBA? Trace Bus (ATB)接口。

20.1 Program and read the trace buffer registers

您可以使用系統寄存器接口來編程和讀取Trace Buffer Extension (TRBE)寄存器。

在編程TRBE寄存器時,核心無需處于調試狀態。當您編程TRBE寄存器時,必須同時啟用所有更改。否則,如果您僅編程計數器,在正確設置觸發條件之前,它可能根據錯誤的事件開始計數。要禁用TRBE,請使用TRBLIMITR_EL1.E位。

請參閱《Arm?架構參考手冊補充Armv9,適用于Armv9-A架構配置文件》以獲取有關TRBE寄存器行為和訪問機制的信息。

20.2 Trace buffer register interface

Cortex??A715核心支持通過系統寄存器接口訪問Trace Buffer Extension (TRBE)寄存器。

寄存器訪問方式取決于TRBE的狀態。請參閱《Arm?架構參考手冊補充Armv9,適用于Armv9-A架構配置文件》以獲取有關行為和訪問機制的信息。

21. Activity Monitors Extension support

?Cortex??A715核心在Arm?v8.4-A架構中實現了Activity Monitors擴展。活動監控具有類似于性能監控的功能,但用于系統管理,而性能監控則面向用戶和調試應用程序。

活動監控提供了對系統功耗管理和持續監控的有用信息。活動監控在操作中為只讀,并且其配置受限于已實現的最高異常級別。

Cortex??A715核心在兩個組中實現了七個計數器,每個計數器都是一個64位計數器,用于計算固定事件。組0有四個計數器,編號為0-3,組1有三個計數器,編號為10-12。

21.1 Activity monitors access

Cortex??A715核心支持通過系統寄存器接口訪問活動監控,并支持使用實用總線接口進行只讀的內存映射訪問。

要了解這些寄存器的內存映射信息,請參閱Arm? A-profile架構的《Arm?架構參考手冊》。

訪問使能位

訪問使能位AMUSERENR_EL0.EN控制EL0對活動監控系統寄存器的訪問。

CPTR_EL2.TAM位控制EL0和EL1對活動監控系統寄存器的訪問。

CPTR_EL3.TAM位控制EL0、EL1和EL2對活動監控擴展系統寄存器的訪問。AMUSERENR_EL0.EN位在EL1、EL2和EL3可配置。所有其他控制和計數器的值僅在最高實現的異常級別可配置。

有關寄存器訪問控制的詳細說明,請參閱Arm? A-profile架構的《Arm?架構參考手冊》。

系統寄存器訪問

可以使用MRS和MSR指令訪問這些活動監控寄存器。

外部內存映射訪問

可以從實用總線接口對活動監控進行內存映射訪問。在這種情況下,活動監控寄存器僅對活動監控事件計數器寄存器提供讀訪問。

在DSU-110 DynamIQ?集群中,活動監控單元(AMU)寄存器在實用總線接口上的基地址為0x<n>90000,其中n是Cortex??A715核心實例號。

如果滿足以下條件之一,則將這些寄存器視為RAZ/WI:

? 該寄存器標記為保留。

? 以錯誤的安全狀態對寄存器進行訪問。

21.2 Activity monitors counters

Cortex??A715核心實現了四個活動監控計數器,編號為0-3,以及三個輔助計數器,編號為10-12。

每個計數器具有以下特點:

? 所有事件都在64位的循環計數器中進行計數,在溢出時會重新計數。不支持溢出狀態指示或中斷。

? 任何時鐘頻率的變化,包括WFI和WFE指令停止時鐘,都可能影響任何一個計數器。

? 事件0-3和輔助事件10-12是固定的,AMEVTYPER0<n>_EL0和AMEVTYPER1<n>_EL0的evtCount位是只讀的。

? 在對核心的電源域進行冷復位時,活動監控計數器會被重置為零。當核心處于非復位狀態時,可以進行活動監控。

21.3 Activity monitors events

Cortex??A715核心中的活動監控事件可以是固定的或可編程的,并且它們映射到活動監控計數器。 下表顯示了計數器與固定事件的映射。

21.4 AArch64 Activity Monitors registers

摘要表格提供了核心中IMPLEMENTATION DEFINED的活動監控寄存器的概述。要獲取有關寄存器的更多信息,請單擊表格中的寄存器名稱。

對于未列出復位值的寄存器,請參考寄存器描述頁面或Arm ARM中記錄的各個字段復位值的文檔。

請注意,具體實現中的活動監控寄存器及其詳細信息可能會有所不同。建議參考Arm提供的官方文檔,以獲取關于Cortex?-A715核心中活動監控寄存器的準確和最新信息。

21.5 External AMU registers

摘要表格提供了核心中IMPLEMENTATION DEFINED的內存映射AMU寄存器的概述。要獲取有關寄存器的更多信息,請單擊表格中的寄存器名稱。

對于沒有列出復位值的寄存器,請參考寄存器描述頁面或Arm ARM中記錄的各個字段復位值的文檔。

請注意,具體實現中的內存映射AMU寄存器及其詳細信息可能會有所不同。建議參考Arm提供的官方文檔,以獲取關于核心中內存映射AMU寄存器的準確和最新信息。

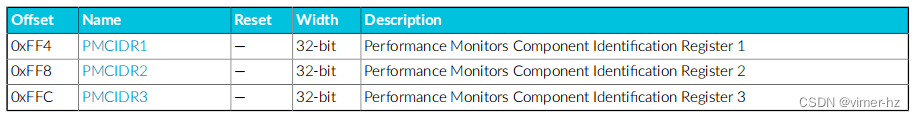

22. Statistical Profiling Extension Support

Cortex?-A715核心在Arm?v8.2-A架構中實現了可選的統計分析擴展(SPE)。SPE提供了對執行指令性能特征的統計視圖,軟件開發者可以利用這些信息來優化代碼以獲得更好的性能。

Cortex?-A715核心通過對微操作進行分析來最小化支持SPE所需的邏輯量。

下圖展示了Cortex?-A715核心中SPE的行為特點。

SPE收集性能分析數據是周期性進行的,一個倒計數器驅動著選擇要進行分析的微操作。該倒計數器記錄了派發的推測微操作的數量,并在每個微操作執行后遞減一次。當倒計數器達到零時,就會將一個微操作標識為樣本,并在其在核心中的整個生命周期中進行分析。

SPE的分析數據使用虛擬地址(VA)寫入內存,這意味著進行分析數據的寫入必須具備內存管理單元(MMU)來將虛擬地址轉換為物理地址(PA),并且必須有一種方式來將數據寫入內存。

預計進行性能分析對核心性能的影響較小。在進行性能分析時,核心的性能不會受到實質性的干擾。

發生頻率取決于采樣率。您可以指定一個對核心性能有實質性干擾的采樣率。Arm建議最小采樣間隔為每1024個微操作一次。這個值通過PMSIDR_EL1.Interval的位[11:8]向軟件進行傳遞。

更多信息,請參考《Arm? Architecture Reference Manual for A-profile architecture》。

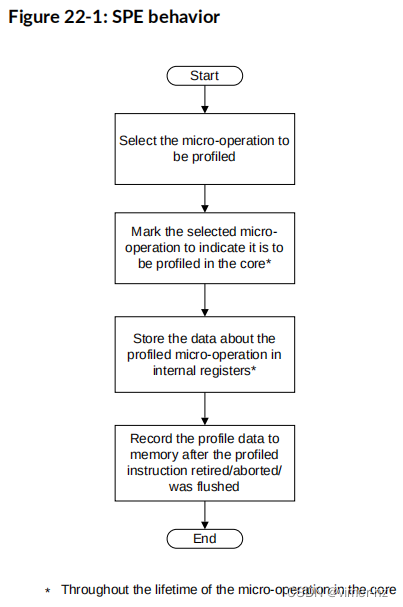

22.1 Statistical Profiling Extension events packet

事件數據包指示采樣操作生成的實現定義事件。 下表顯示了在Cortex?-A715核心中實現的32位事件數據包中定義的事件。

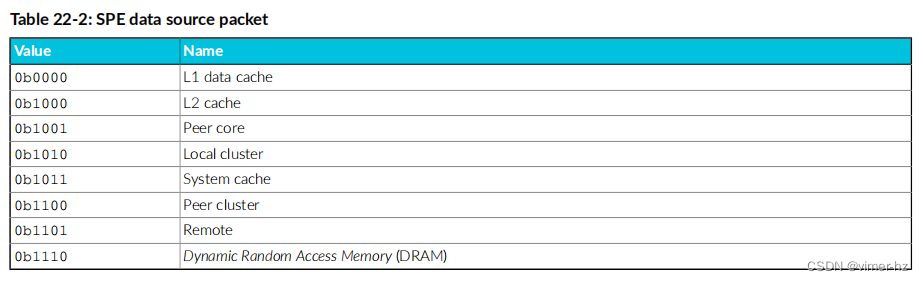

22.2 Statistical Profiling Extension data source packet

數據源數據包指示加載或存儲操作返回的數據來自哪里。 下表顯示了在Cortex?-A715核心中實現的8位數據源數據包中定義的數據源。

)