目錄

一、前言

二、Logic?Level distribution

2.1?logic level配置

2.2?Logic Level Distribution報告

2.3?Logic Level?報告詳情查看

2.4?Route Distributions?報告詳情查看

2.5 示例代碼

一、前言

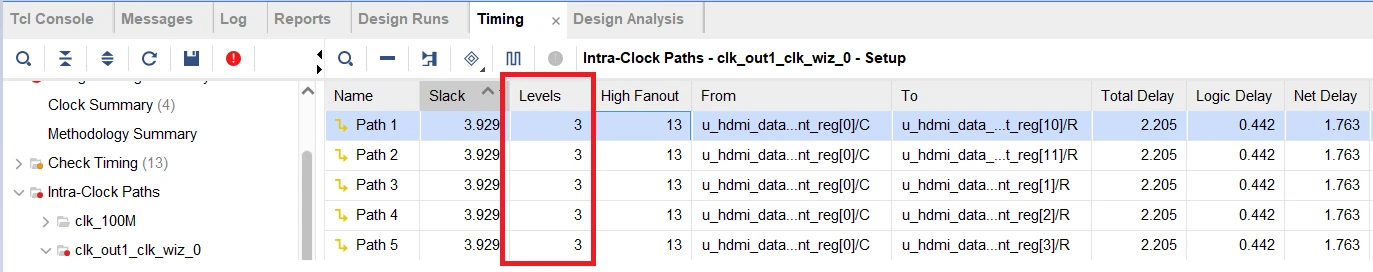

?????在工程設計中,如果需要了解路徑的邏輯級數,可以在report timing summary中找到對應的時序路徑,查看時序路徑的詳情報告中有邏輯級數的信息,如下圖

?????這種方法查看有一個缺點,就是無法知道工程設計中邏輯級數的總體情況,這個時候就可以使用Report design analysis中的Include logic level distribution來查看

二、Logic?Level distribution

2.1?logic level配置

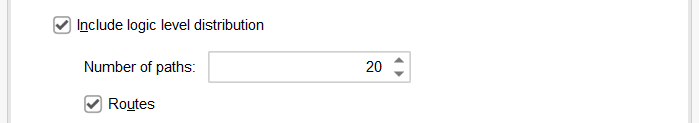

?????工程運行完Synthesize或implement時,進入菜單欄的“Reports”中,在“Reports->Report Design Analysis->Options”中,存在“Include logic?level distribution”,默認不勾選,勾選后同時可以設置展示總的顯示邏輯級數數量Number of paths,默認是1000條,表示最多只顯示1000條,這1000條是所有路徑中最差slack的1000條,不足1000條時按實際顯示路徑數顯示。

2.2?Logic Level Distribution報告

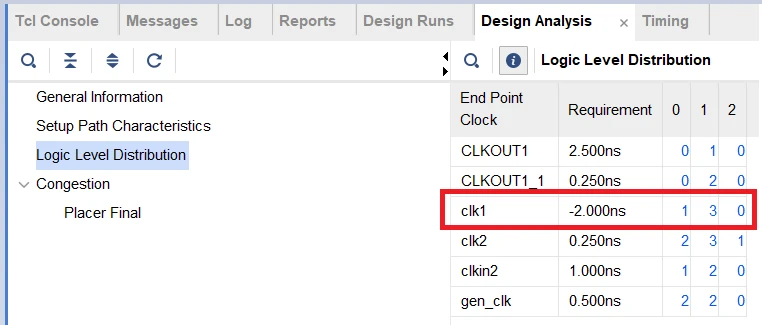

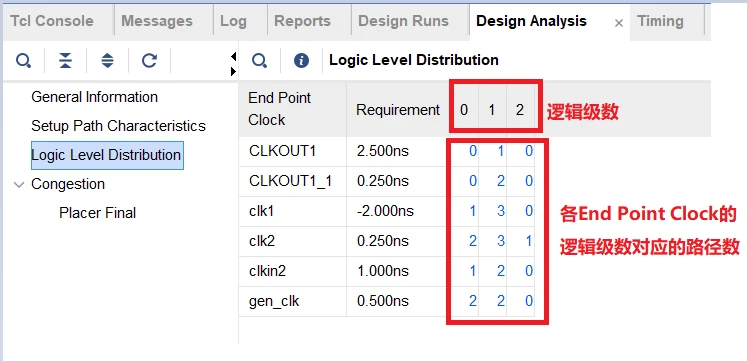

?????以Number of paths設置20為例,在Logic Level Distribution中將顯示所有時序路徑中最差的20條路徑。注:logic level distribution只考慮setup路徑。

左側報告包含3類內容:

End Point Clock:根據所有時序路徑中End Point Clock來劃分

Requirement:展示的End point clock對應路徑中最差的Requirement,以End point clock為clk1,邏輯級數為0的1條,邏輯級數為1的3條,邏輯級數為2的沒有

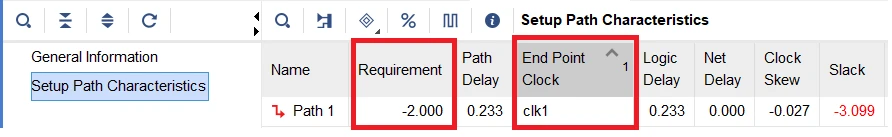

查看邏輯級數為0路徑的requirement

查看邏輯級數為1路徑的requirement,在Logic level distribution中clk1選取的requirement為-2,即為所有路徑requirement中的最小值

工程中各邏輯級數:此處時序路徑數邏輯級數只有0級,1級和2級,下面對應的展示了各邏輯級數的路徑數量,所有路徑數量加起來即為設置的Number of paths值20

2.3?Logic Level?報告詳情查看

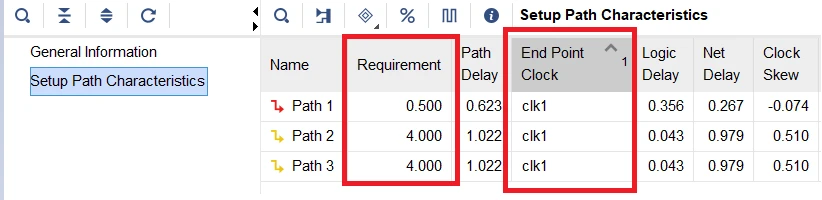

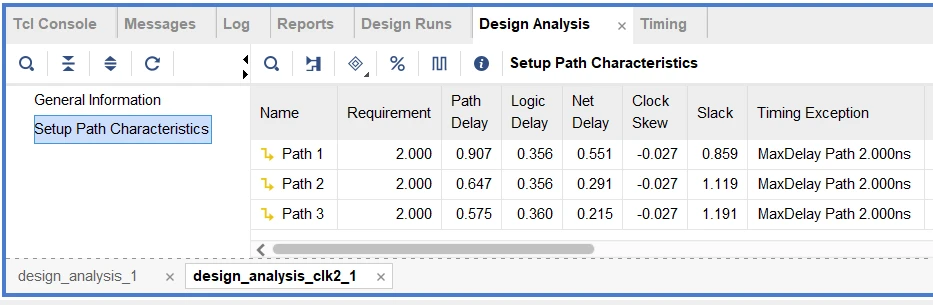

在logic level distribution報告中,選中需要查看的路徑,以下圖clk2的邏輯級數為1的3條路徑為例,見紅框內,點擊鼠標左鍵,彈出彈框

選擇“Report Design Analysis on Timing Paths”,在原有的Design analysis窗口中打開報告,報告為setup path characteristics

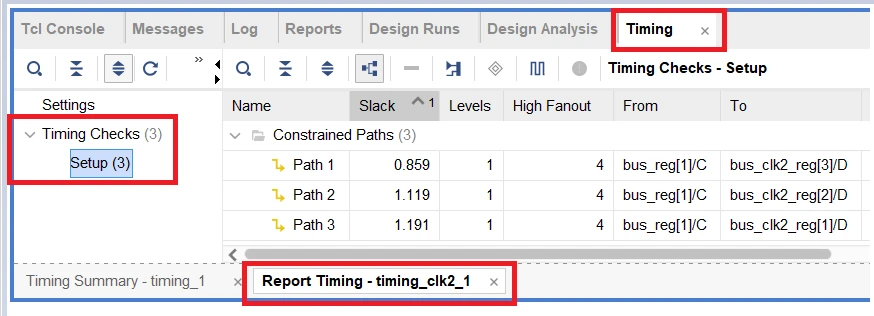

選擇“Report Timing on Timing Paths”,在新打開的Timing窗口中以時序報告路徑的形式展現

在完成Implement后,選擇“Select?Timing?Paths”,將會在Netlist窗口和device中顯示該路徑中的包含的cells和路徑(白色高亮)

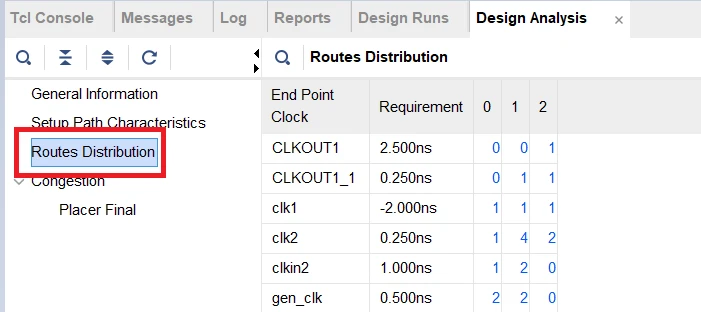

2.4?Route Distributions?報告詳情查看

生成Report?Design Analysis時如果勾選Routes,則可以生成Route?Distributions報告,主要提供時序路徑中完全布線的net數量

Routes數量表示時序路徑上data path中屬于fully routed的net數量,通常是和邏輯級數一致,如果時序路徑屬于起點或終點為port的,如recovery路徑或設置了setup_output_delay的路徑,則logic level值和routes會不一致

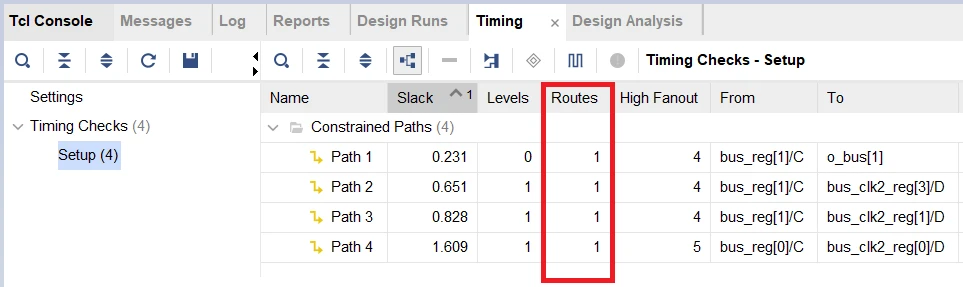

以上圖的end point clock為clk2,數量為1的4為例,執行report timing on timing paths,時序報告中有一列Routes,顯示了對應路徑 routes的數量,圖中都為1

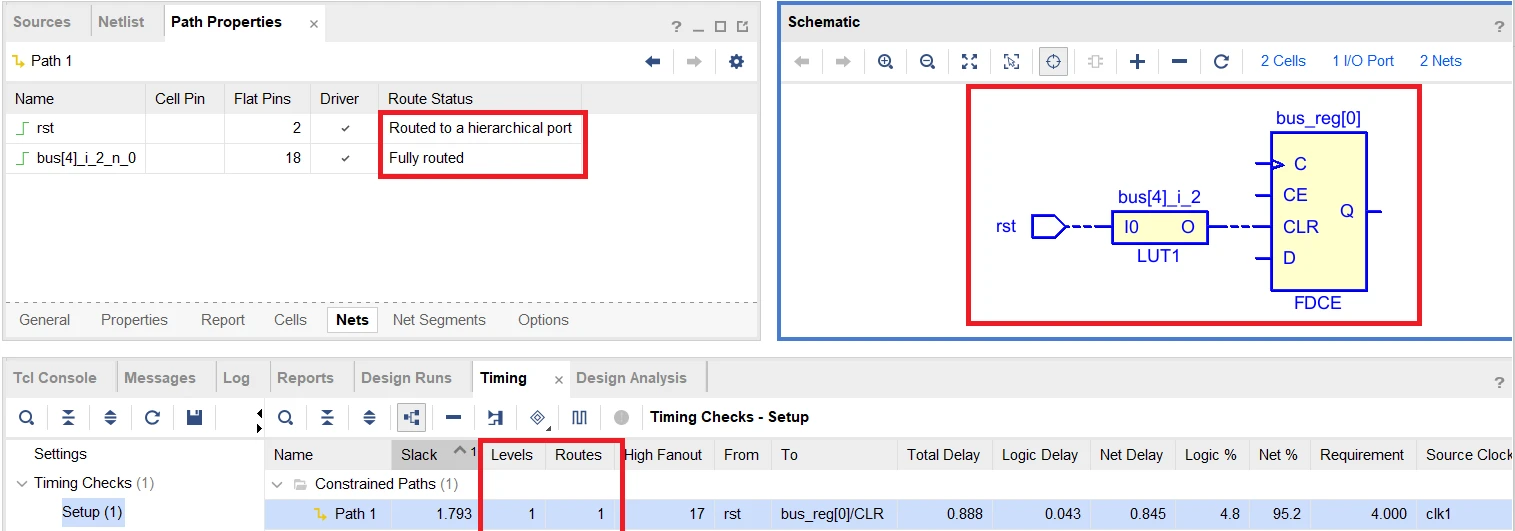

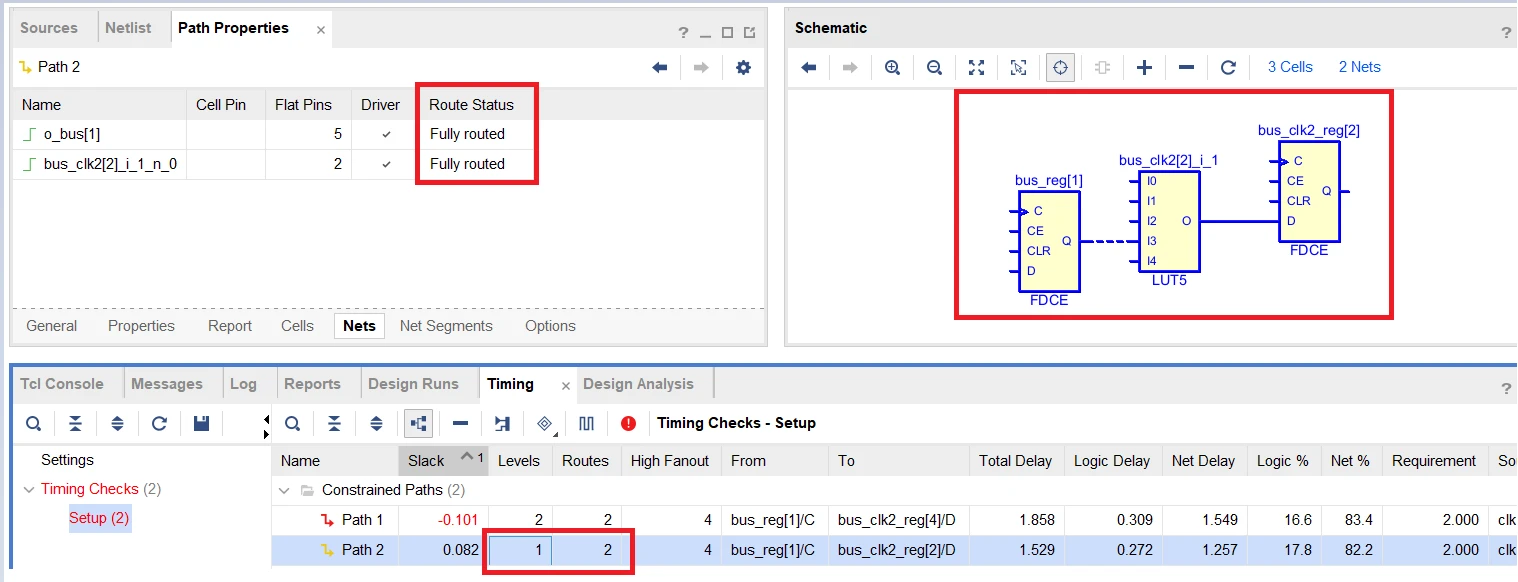

執行select timing paths,在Net窗口會顯示對應的routes名稱,Route Status為Fully routed的才被考慮,如下圖第1條net rst屬于routed to a hierarchical port,則不會考慮進Routes Distribution中,因此路徑的routes數量為1,level也為1。

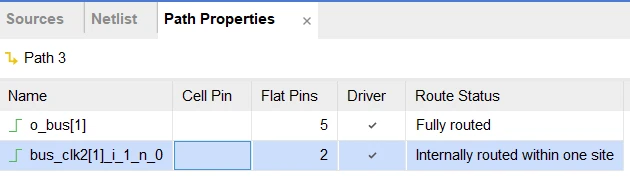

Route Status為internally routed within one site也不會被統計到routes中

?下面的路徑中logic level為1,route數量為2

2.5 示例代碼

module logic_level(CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,CLKFBOUT,clk1,clk2,rst,d1,d2,S,i_bus,o_bus,bus_clk2,out_syn,out_asyn,and_out,o_case);

input CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,clk1,clk2,rst,d1,d2,S;

input [4:0] i_bus;

output reg [4:0] o_bus,bus_clk2;

output out_syn,out_asyn,and_out,CLKFBOUT;

reg ff1,ff2,ff_asyn,ff_syn,ff_and;

reg ff_case;

output reg o_case;

reg [4:0] bus;

wire sum12,and_c,CLKOUT0,CLKOUT1;

wire [4:0] bus_c;

wire o_bufgmux,ffcase_n;PLLE2_ADV #(.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64).CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN1_PERIOD(0.0),.CLKIN2_PERIOD(0.0),// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128).CLKOUT0_DIVIDE(1),.CLKOUT1_DIVIDE(2),.CLKOUT2_DIVIDE(4),.CLKOUT3_DIVIDE(5),.CLKOUT4_DIVIDE(1),.CLKOUT5_DIVIDE(1),// CLKOUT0_DUTY_CYCLE - CLKOUT5_DUTY_CYCLE: Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT0_DUTY_CYCLE(0.4),.CLKOUT1_DUTY_CYCLE(0.5),.CLKOUT2_DUTY_CYCLE(0.5),.CLKOUT3_DUTY_CYCLE(0.5),.CLKOUT4_DUTY_CYCLE(0.5),.CLKOUT5_DUTY_CYCLE(0.5),// CLKOUT0_PHASE - CLKOUT5_PHASE: Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT0_PHASE(0.0),.CLKOUT1_PHASE(0.0),.CLKOUT2_PHASE(0.0),.CLKOUT3_PHASE(0.0),.CLKOUT4_PHASE(0.0),.CLKOUT5_PHASE(0.0),.COMPENSATION("EXTERNAL"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL.DIVCLK_DIVIDE(1), // Master division value (1-56)// REF_JITTER: Reference input jitter in UI (0.000-0.999)..REF_JITTER1(0.0),.REF_JITTER2(0.0),.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE"))PLLE2_ADV_inst (// Clock Outputs: 1-bit (each) output: User configurable clock outputs.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2// Feedback Clocks: 1-bit (each) output: Clock feedback ports.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock// Clock Inputs: 1-bit (each) input: Clock inputs.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock// Control Ports: 1-bit (each) input: PLL control ports.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.RST(rst), // 1-bit input: Reset// Feedback Clocks: 1-bit (each) input: Clock feedback ports.CLKFBIN(CLKFBIN) // 1-bit input: Feedback clock);// End of PLLE2_ADV_inst instantiationalways@(posedge CLKOUT0,negedge rst)if(!rst)beginff1<=1'b0;ff2<=1'b0;endelse beginff1<=d1;ff2<=d2;endassign sum12=ff1+ff2;

always@(posedge CLKOUT1,negedge rst)if(!rst)ff_syn<=1'b0;else beginff_syn<=sum12;end

assign out_syn=ff_syn;always@(posedge clk1,negedge rst)if(!rst)ff_asyn<=1'b0;else beginff_asyn<=sum12;end

assign out_asyn=ff_asyn;

assign and_c=ff_asyn&d1;always@(posedge clk1,negedge rst)if(!rst)ff_and<=1'b0;else beginff_and<=and_c;end

assign and_out=ff_and;always@(posedge clk1,negedge rst)if(!rst)bus<=5'b0;else beginbus<=i_bus+1'b1;end

assign bus_c=bus+d2;

always@(*)begino_bus=bus;end

always@(posedge clk2,negedge rst)if(!rst)bus_clk2<=5'b0;else beginbus_clk2<=bus_c+d1;end//set_case_analysisBUFGMUX #()BUFGMUX_inst (.O(o_bufgmux), // 1-bit output: Clock output.I0(CLKIN1), // 1-bit input: Clock input (S=0).I1(CLKIN2), // 1-bit input: Clock input (S=1).S(S) // 1-bit input: Clock select);always@(posedge o_bufgmux,negedge rst)if(!rst)ff_case<=1'b0;else beginff_case<=d1;end

assign ffcase_n=!ff_case;always@(posedge o_bufgmux,negedge rst)if(!rst)o_case<=1'b0;else begino_case<=ffcase_n;endendmodule 約束

//創建主時鐘和生成時鐘

create_clock -period 10.000 -name clkin1 -waveform {0.000 5.000} -add [get_ports CLKIN1]

create_clock -period 5.000 -name clkin2 -waveform {0.000 2.500} -add [get_nets CLKIN2]

create_clock -period 4.000 -name clk2 -waveform {0.000 2.000} -add [get_ports clk2]

create_clock -period 4.000 -name clk1 -waveform {0.000 2.000} -add [get_ports clk1]

create_generated_clock -name gen_clk -source [get_pins PLLE2_ADV_inst/CLKOUT1] -multiply_by 2 -add -master_clock clkin2 [get_pins PLLE2_ADV_inst/CLKOUT0]

set_input_jitter [get_clocks clk2] 0.500

set_clock_latency -clock [get_clocks clk2] 0.333 [get_pins {bus_reg[1]/D}]

set_system_jitter 0.009

set_clock_uncertainty 0.500 [get_clocks clk1]//設置時鐘組和總線偏斜

set_clock_groups -name clkin1_group -asynchronous -group [get_clocks clkin1]

set_bus_skew -from [get_cells {{bus_reg[0]} {bus_reg[1]} {bus_reg[2]} {bus_reg[3]} {bus_reg[4]}}] -to [get_cells {{bus_clk2_reg[0]} {bus_clk2_reg[1]} {bus_clk2_reg[2]} {bus_clk2_reg[3]} {bus_clk2_reg[4]}}] 0.550

set_input_delay -clock [get_clocks clk1] 1.111 [get_ports {d1 d2 {i_bus[0]} {i_bus[1]} {i_bus[2]} {i_bus[3]} {i_bus[4]} rst}]

set_output_delay -clock [get_clocks clk2] 0.222 [get_ports {and_out {o_bus[0]} {o_bus[1]} {o_bus[2]} {o_bus[3]} {o_bus[4]} out_asyn out_syn}]//設置時序例外分析

set_false_path -setup -from [get_pins {bus_reg[2]/C}] -to [get_pins {bus_clk2_reg[4]/D}]

set_max_delay -from [get_pins {bus_reg[1]/C}] 2.000

set_min_delay -from [get_pins {bus_reg[0]/C}] 0.500

set_external_delay -from [get_ports CLKFBOUT] -to [get_ports CLKFBIN] 0.444

set_multicycle_path -from [get_pins {bus_reg[0]/C}] -to [get_pins {bus_clk2_reg[2]/D}] 2

set_disable_timing [get_cells {bus_reg[3]}]//設置時序斷言

set_case_analysis 1 [get_ports S]

set_data_check -from [get_pins {bus_reg[2]/C}] -to [get_pins {bus_reg[2]/Q}] 0.333 -clock [get_clocks clk2]

set_clock_sense -positive -clocks [get_clocks clk1] [get_pins ff_asyn_reg/C]

group_path -name {group_path} -weight 1.000 -from [get_ports {d1 d2}]

代碼實踐 -循環神經網絡- 56門控循環單元(`GRU`))

)

)