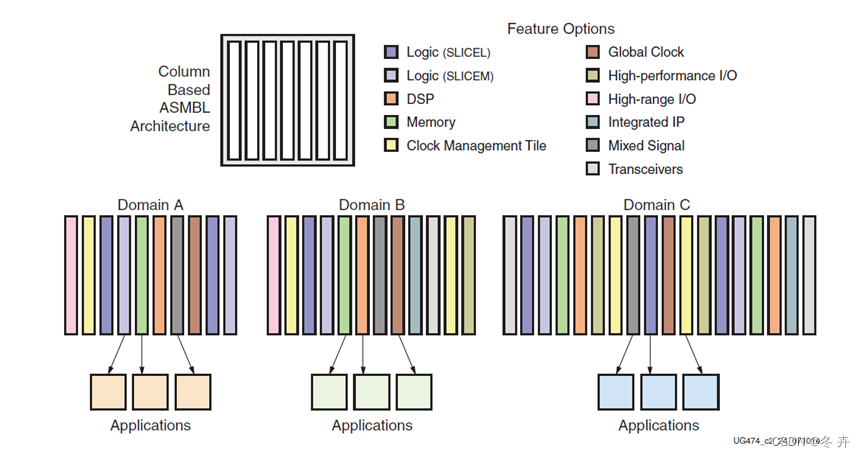

Xilinx FPGA創建了先進的硅模塊(ASMBL)架構,以實現FPGA具有針對不同應用程序領域優化的各種功能組合的平臺。通過這一創新,Xilinx提供了更多的設備選擇,使客戶能夠為其特定設計選擇具有正確的功能和功能組合的FPGA。ASMBL體系結構通過以下方式突破了傳統的設計障礙:消除幾何布局約束,如I/O數量和陣列大小之間的依賴關系;允許將電源和接地放置在芯片上的任何位置,增強芯片上的電源和接地點分布;允許獨立于彼此和周圍資源對不同的集成IP塊進行擴展。芯片主要由6部分完成,分別為:基本可編程邏輯單元(configurable logic block,CLB)、嵌入塊式RAM、完整的時鐘管理、可編程輸入輸出單元(IOB)、內嵌的底層功能單元和內嵌專用硬件模塊以及豐富的布線資源。賽靈思7系列器件是之前使用較廣的器件,工藝制程為28nm,包含四類:Spartan,Artix,Kintex,Virtex,都支持低功耗。本文內容主要是參考官網7系列的用戶手冊,并增加了自己的理解和項目經驗。

CLB

CLB(Configurable Logic

)

控件實現網頁爬蟲的代碼片段)

FreeRTOS實時操作系統詳解及實戰含源碼視頻)

![[SwiftUI 開發] 嵌套的ObservedObject中的更改不會更新UI](http://pic.xiahunao.cn/[SwiftUI 開發] 嵌套的ObservedObject中的更改不會更新UI)

6千字好文)

)