AXI接口,全稱為Advanced eXtensible Interface,是ARM公司推出的一種高性能、低成本、可擴展的高速總線接口。AXI接口是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)高級微控制器總線架構的一部分。2003年發布了AXI的第一版即AXI3.0(稱為AXI3),2010年發布了AXI的第二版即AXI4.0(稱為AXI4)。

主要特點:

高性能、高帶寬、低延遲:AXI接口被設計用于需要高性能、高帶寬和低延遲的應用場景。

靈活性和可擴展性:AXI接口具有高度的靈活性和可擴展性,可以適應不同的應用場景和系統需求。

支持多種傳輸類型:包括讀取、寫入、緩存、鎖定和原子性操作。

支持多個主設備和從設備,支持不對齊的數據傳輸:可以方便地構建高度集成的系統。

總線的地址/控制和數據通道是分離的,具有分離的讀/寫數據通道;

支持突發傳輸,突發傳輸過程中只需要首地址;

支持顯著傳輸訪問和亂序訪問,更加容易進行時序收斂

類型與版本:

AXI接口有三種主要類型:AXI4、AXI4-Lite和AXI4-Stream。

AXI4:最完整、最全面的版本,支持大量的高級特性,如數據一致性、QoS(Quality of Service)、多周期傳輸、多個地址通道等。

AXI4-Lite:簡化版,只支持簡單的讀寫操作,適用于對帶寬要求不高的設備。主要用于訪問一些低速外設中的寄存器

AXI4-Stream:面向流數據的版本,適用于數據流傳輸,如音視頻數據,高速 AD、PCIe、DMA 接口等需要高速數據傳輸的場合

技術細節:

地址/控制和數據通道分離:使得AXI接口在數據傳輸時具有更高的靈活性和效率。

支持不對齊的數據傳輸:增加了數據傳輸的靈活性。

支持突發傳輸:在突發傳輸過程中只需要首地址,提高了數據傳輸的效率。

分離的讀/寫數據通道:進一步提高了數據傳輸的并行性和效率。

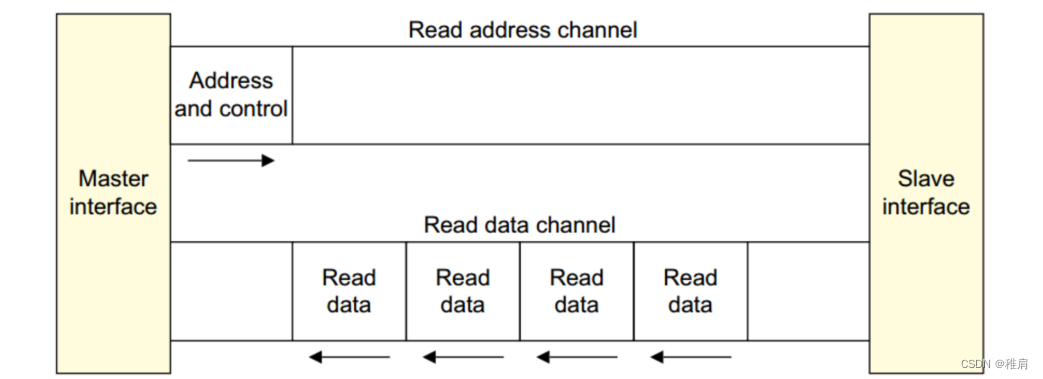

讀傳輸過程,主機首先在讀地址通道給出讀地址和控制信號,然后從機由讀數據通道返回讀出的數據,主機從該地址連續突發讀出四個數據。

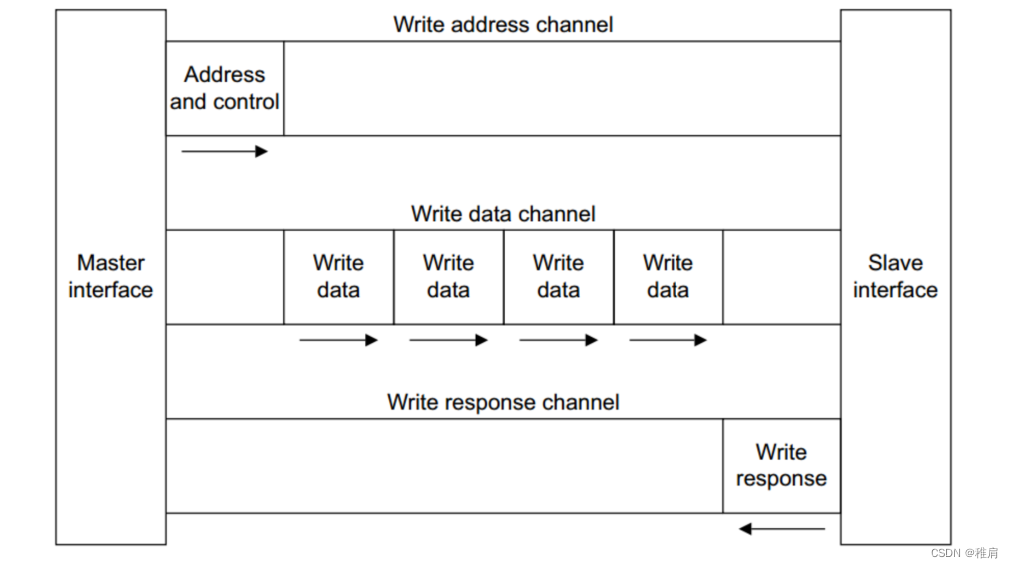

寫傳輸過程中,用到了寫地址、寫數據和寫響應三個通道。突發寫四個數據。

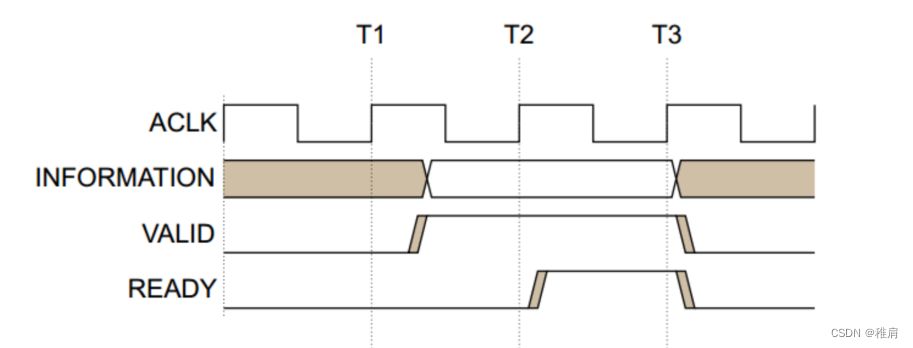

AXI 總線中的每個通道都包含了一組信息信號,還有一個 VALID 和一個 READY 信號。所有的輸入信號都在是 ACLK 的上升沿采樣,輸出信號在上升沿后改變。T1時刻后,源端VALID信號拉高,說明 INFORMATION信號線上傳輸的是有效的地址、數據或者控制信息。T2時刻,目的端READY信號拉高,說明準備好接受數據。T3時刻開始進行數據傳輸。

應用場景:

AXI接口廣泛應用于數字系統中,特別是嵌入式系統、FPGA和ASIC設計中。

用于連接處理器、內存、外設以及其他硬件模塊之間,提供了一種靈活、可擴展的通信方式。

是什么?中英雙語介紹)

UVC驅動分析)

“云計算應用”賽項賽卷9(公有云))