原文鏈接(相關文章合集):OFDM 802.11a的xilinx FPGA實現

1.前言

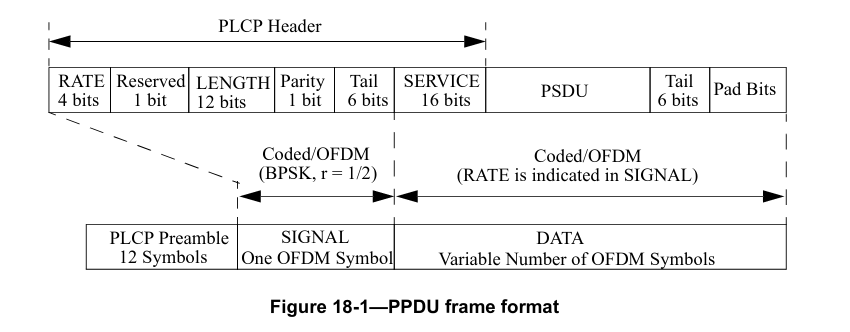

??在之前已經完成了data域數據的處理,在構建整個802.11a OFDM數據幀的時候,還剩下前導碼和signal域的數據幀,這兩部分的內容。 PLCP的前導部分由一組重復10次的短訓練序列和一組加了一個長型保護間隔與重復2次的有效OFDM符號組成的長訓練序列組成。今天先來實現短訓練序列。

2.原理

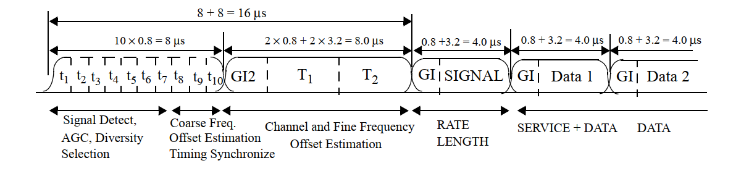

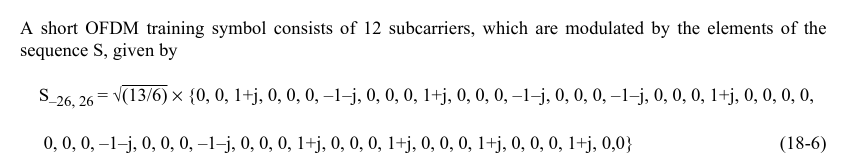

??短訓練序列的主要用途是進行信號的檢測、AGC和粗頻偏估計。短訓練序列都是經過精心的設計,每個短訓練序列的長度為0.8us,在802.11a的前導碼當中一共有10個短訓練序列。這些短訓練序列符號占據每個OFDM符號的52個非零子載波當中的12個。如果用-26~26來標識非零子載波的話,那么短訓練序列的子載波的序號為{-24, -20, -16, -12, -8, -4, 4, 8, 12, 16, 20, 24},其中傳輸的傳輸數據為一個固定的偽隨機序列,采用的QPSK的映射方式。

??由于短訓練序列只用了52個子載波當中12個來傳輸符號,因此為了保證OFDM符號的功率穩定,需要乘以因子 。短訓練序列的的選擇可以是的在較大的范圍內實現粗頻率估計,通常對于周期為T的重復符號而言,最大可估計的頻率偏差為,因此通過測量連續兩個長度為0.8us的短訓練序列符號的相位差,可以估計的頻率偏差可達625KHz。 訓練序列生成模塊主要是提前將長、短序列的時域樣值計算出并存入RAM中,需要時直接讀取數據即可。

3.Matlab仿真

??由于Data域數據在IFFT處理之前會擴大8倍,相應的長訓練序列在進行IFFT處理之前也需要擴大8倍。同時長、短訓練序列也是需要經過加窗處理的,即多輸出一個樣值,該值為第一個樣值,同時將第一個樣值與最后一個樣值縮小一倍。Matlab生成短訓練序列代碼如下:

%產生長短訓練序列、幀頭

short_training?=[0,0,0,0,-1-1i,0,0,0,-1-1i,0,0,0,1+1i,0,0,0,1+?...1i,0,0,0,1+1i,0,0,0,1+1i,0,0,0,0,0,0,0,0,0,0,0,0,0,...0,0,1+1i,0,0,0,-1-1i,0,0,0,1+1i,0,0,0,-1-1i,?...0,0,0,-1-1i,0,0,0,1+1i,0,0,0];?%?short?training?sequence

sts_frq?=?(13/6)^0.5?.*?short_training;

sts_time?=?8*ifft(sts_frq,64);????%對短訓練序列進行ifft

%取16點,將該序列重復10次

sts16?=?sts_time(1:16);

sts16_q?=?num2bin(q,sts16);%量化,存到FPGA的ROM

sts_rom?=?sts16;

for?n?=?1:9sts_rom?=?[sts_rom,sts16];

end

q?=?quantizer('fixed','round','saturate',[8,6]);%復數以8位定點數形式進行輸出,格式為:1位符號位,一位整數位,6位小數位,負數以補碼形式表示。

sts_rom?=?[0.5*sts_rom(1),sts_rom(2:end),0.5*sts16(1)];?????%加窗

??生成的STS序列如下表所示,把它們存到FPGA的ROM里面:

| 地址 | 實部 | 虛部 | 地址 | 實部 | 虛部 |

|---|---|---|---|---|---|

| 0 | 8'b00011000 | 8'b00011000 | 8 | 8'b00011000 | 8'b00011000 |

| 1 | 8'b10111100 | 8'b00000001 | 9 | 8'b00000001 | 8'b10111100 |

| 2 | 8'b11111001 | 8'b11011000 | 10 | 8'b11011000 | 8'b11111001 |

| 3 | 8'b01001001 | 8'b11111010 | 11 | 8'b11111010 | 8'b01001001 |

| 4 | 8'b00101111 | 8'b00000000 | 12 | 8'b00000000 | 8'b00101111 |

| 5 | 8'b01001001 | 8'b11111010 | 13 | 8'b11111010 | 8'b01001001 |

| 6 | 8'b11111001 | 8'b11011000 | 14 | 8'b11011000 | 8'b11111001 |

| 7 | 8'b10111100 | 8'b00000001 | 15 | 8'b00000001 | 8'b10111100 |

4.硬件實現

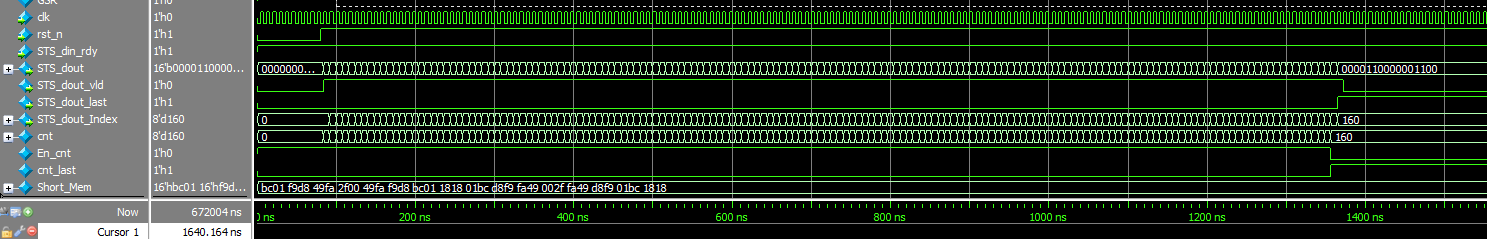

??STS一個周期的16個時域樣值被存入片內ROM中,ROM的具體內容如上面的表所示,該ROM共有16個地址空間,每個地址對應16位的字長,其中高8位存儲STS樣值的虛部,低8位存儲STS樣值的實部(與IFFT輸出保持一致)。ROM的地址信號由一個模161的計數器生成。STS_din_rdy作為ROM的讀使能信號,代表后面的模塊準備好接收數據。當STS_din_rdy為高時,計數器以模161形式開始計數161個時鐘,生成的地址信號為計數器的低4位,即cnt[3:0]控制ROM將其中存儲的16個STS樣值重復讀取10個周期,形成標準所規定的短訓練序列。 代碼如下:

assign?En_cnt?=?STS_din_rdy?&?~cnt_last;counter?#(.CNT_NUM('d161),.ADD(1'b1))

u_counter(

.clk??(clk????),?

.rst_n??(rst_n????),

.En_cnt??(En_cnt????),??????

.cnt??(cnt????),?

.cnt_last?(cnt_last???)

);always?@(posedge?clk?or?negedge?rst_n)?if(!rst_n)beginSTS_dout_last?<=?1'b0;STS_dout_Index?<=?'d0;endelse?beginSTS_dout_last?<=?cnt_last;STS_dout_Index?<=?cnt;endalways?@(posedge?clk?or?negedge?rst_n)?beginif(~rst_n)?begin??//時域樣值Im???????ReShort_Mem[0]??<=?{8'b00011000,8'b00011000};??????Short_Mem[1]??<=?{8'b00000001,8'b10111100};Short_Mem[2]??<=?{8'b11011000,8'b11111001};Short_Mem[3]??<=?{8'b11111010,8'b01001001};Short_Mem[4]??<=?{8'b00000000,8'b00101111};Short_Mem[5]??<=?{8'b11111010,8'b01001001};Short_Mem[6]??<=?{8'b11011000,8'b11111001};Short_Mem[7]??<=?{8'b00000001,8'b10111100};Short_Mem[8]??<=?{8'b00011000,8'b00011000};Short_Mem[9]??<=?{8'b10111100,8'b00000001};Short_Mem[10]?<=?{8'b11111001,8'b11011000};Short_Mem[11]?<=?{8'b01001001,8'b11111010};Short_Mem[12]?<=?{8'b00101111,8'b00000000};Short_Mem[13]?<=?{8'b01001001,8'b11111010};Short_Mem[14]?<=?{8'b11111001,8'b11011000};Short_Mem[15]?<=?{8'b10111100,8'b00000001};STS_dout?<=?'d0;STS_dout_vld?<=?1'b0;endelse?if(STS_din_rdy?&?STS_dout_last)STS_dout_vld?<=?1'b0;else?if(cnt?==?'d0?|?cnt_last)beginSTS_dout?<=?{Short_Mem[0][15:8]>>1,Short_Mem[0][7:0]>>1};STS_dout_vld?<=?1'b1;endelse?beginSTS_dout?<=?Short_Mem[cnt[3:0]];?STS_dout_vld?<=?1'b1;end

end

??此處的設計已經考慮了加窗處理(Windowing),該操作在硬件中的實現方法是:將要進行加窗處理的數據單元(STS)多輸出一個樣值(數據單元的第一個樣值),同時將數據單元的第一個樣值和最后一個樣值縮小1倍。在傳輸時,一個數據單元的最后一個樣值將與下一個數據單元的第一個樣值進行相加,成為一個采樣點。因此,本設計中計數161個而非160個時鐘,它將控制ROM在第161個時鐘周期內再輸出一個樣值(地址為0的第一個樣值)。模塊的輸出部分會對第一個和最后一個樣值執行右移1位(即除以2)的操作,從而最終完成加窗處理。

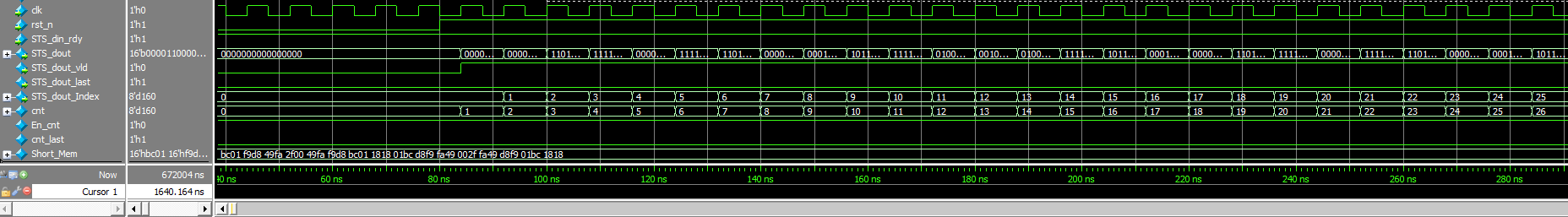

5.MosdelSim仿真

原文鏈接(相關文章合集):OFDM 802.11a的xilinx FPGA實現

)

)

)

)

——通過集合制作的學生信息管理系統)