摘要——軟件定義無線電可以在通用處理器 (CPU) 上實現,例如基于 PC 的處理器。處理器具有高度靈活性:它不僅可以用來處理數據樣本,還可以控制接收器功能、顯示瀑布圖或運行解調軟件。然而,由于處理速度相對較慢,處理器只能處理有限帶寬的信號。對于高帶寬信號,軟件定義無線電 (SDR) 算法必須以定制設計的數字電路形式在 FPGA 芯片上實現。FPGA 的處理速度非常快,但靈活性和用戶界面不足。最近,FPGA 制造商賽靈思 (Xilinx) 推出了一款名為 Zynq 的混合片上系統,它將兩種方案結合起來。它采用雙 ARM Cortex-A9 處理器和一個 FPGA,在單芯片上兼具處理器的靈活性和 FPGA 的處理速度。因此,Zynq 在軟件定義無線電 (SDR) 中的應用非常有前景。本文將討論 Zynq 及其評估板 (Zedboard) 的應用。作為示例,我們在 Zedboard 上實現了一個直接采樣接收器,該接收器使用一個 250 Msps 的高速 16 位 ADC。

一、SDR 硬件平臺

軟件定義無線電 (SDR) 依靠軟件和數字信號處理來接收無線電信號。SDR 算法

始終在硬件平臺上運行:在處理器(例如 PC 或微處理器)上運行,或在微芯片(例如 FPGA)中實現為數字電路。這些硬件平臺在處理速度、功耗、尺寸、靈活性和設計簡易性方面各不相同。

A. 常用硬件

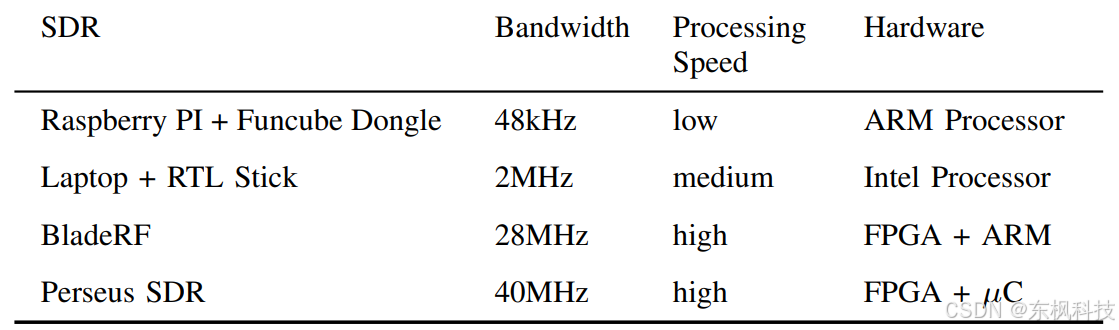

目前,市場上有各種各樣的平臺,

其中的一些示例如表一所示。帶有 Funcube Dongle SDR (FCD) 的 Raspberry Pi 是一款小型嵌入式便攜式設備,采樣率降低至 48 kHz,但處理速度非常有限。英特爾酷睿 i7 筆記本電腦處理器速度更快,可以處理帶寬為 2 MHz 的 RTL DVB 棒,但功耗更高,體積也更大。帶寬更大的軟件無線電(SDR),例如 bladeRF(28 MHz)或直接采樣接收機,例如 Perseus SDR(40 MHz),都需要更高的處理速度,而處理器無法提供這種能力。在這種情況下,FPGA 用于數字化射頻信號的高速處理。

B. 要求

SDR 硬件所需的處理速度不僅取決于信號帶寬,而且很大程度上取決于信號帶寬。帶寬越大,采樣率也就越高,需要處理的數據就越多。高性能直接采樣接收機通常以超過 50 Msps 的速度對模擬信號進行采樣。這對處理速度提出了巨大的要求——隨著直接采樣(即在天線之后直接對模擬信號進行采樣)在 SDR 中變得越來越普遍,這一事實將變得更加明顯。

另一方面,靈活性是現代 SDR 接收機的一個問題。解調就是一個例子。業余無線電愛好者已經開發出多種數字模式,商業應用中也需要在調制類型、糾錯和信源編碼之間切換。

C. 處理器 vs FPGA

處理器是一種執行軟件的電子電路。

軟件執行以串行方式逐條指令進行,因此速度較慢,不適合高端軟件無線電(SDR)中的大帶寬處理。多核處理器是一個例外,它們在一定程度上具有并行性。

尤其是在顯卡中,可以找到功能強大的多核處理器(GPU),非常適合信號處理。

然而,許多處理器功耗很高,

并且在PC(包括顯卡)中需要占用很大的空間。處理器的優勢在于它非常靈活,

因為它可以通過執行不同的軟件輕松更改其執行的任務。此外,通常可以運行操作系統,并具有易于訪問用戶界面(例如顯示器、鍵盤、鼠標)以及訪問硬盤進行存儲或連接互聯網的優勢。在 SDR 應用中,處理器非常適合:

解調不同模式

? 提供圖形用戶界面 (GUI)

? 控制接收器功能

? 記錄和存儲信號

? 提供互聯網接入

FPGA 與處理器有著根本的不同。FPGA 是一種微芯片,包含大量可用于構成數字電路的元件,包括加法器、乘法器、多路復用器、寄存器等。對于要在 FPGA 上“執行”的每種算法,都必須設計專用的數字電路(硬件實現)并將其加載到 FPGA 上(配置)。原則上,這種配置包括 FPGA 元件之間的布線,以形成所需的數字電路。FPGA 可以反復配置,這稱為重新配置,以便以后可以修改電路以消除錯誤或添加擴展功能。這使得 FPGA 成為一種相對便宜的微芯片,任何具備一些數字設計知識的人都可以設計它。FPGA 的一大優勢在于它們可以高度并行地處理數據。因此,它們速度非常快,可以輕松處理高達數百 Msps 的數據。盡管 FPGA 的時鐘頻率通常要低得多(大約幾百 MHz),但其可實現的加速通常可達處理器的 100 倍到 1000 倍。由于 FPGA 中的電路是定制設計的,因此可以根據具體應用選擇數據、存儲器和運算單元的位寬,這非常高效。例如,如果認為 6 位的位寬對于某個數據來說已經足夠,則處理單元的布局將僅使用這 6 位;而在處理器中,位寬或多或少會限制在一個預定義的數字(例如 24、32 或 64 位)內。此外,與具有類似處理速度的(多核)處理器系統(例如 GPU 顯卡)相比,FPGA 的功耗也更低。 FPGA 的缺點在于,算法的硬件實現(即電路設計)需要精通硬件描述語言、數字電路設計以及設計工具的使用經驗。此外,外部接口(顯示器、鍵盤、網絡連接)的實現也很困難。在軟件無線電 (SDR) 應用中,FPGA 非常適合高速、重復性計算,例如:

? 混頻和下變頻

? 濾波

? 高速 FFT

? 大量信號的并行解調

處理器和 FPGA 各有優缺點。在 SDR 中,各種不同的任務必須以不同的速度執行,這很難用單個處理器或單個 FPGA 實現。因此,SDR 的理想硬件是兩者的結合。事實上,高端 SDR 已經遵循了這一原則。

II. ZYNQ 片上系統

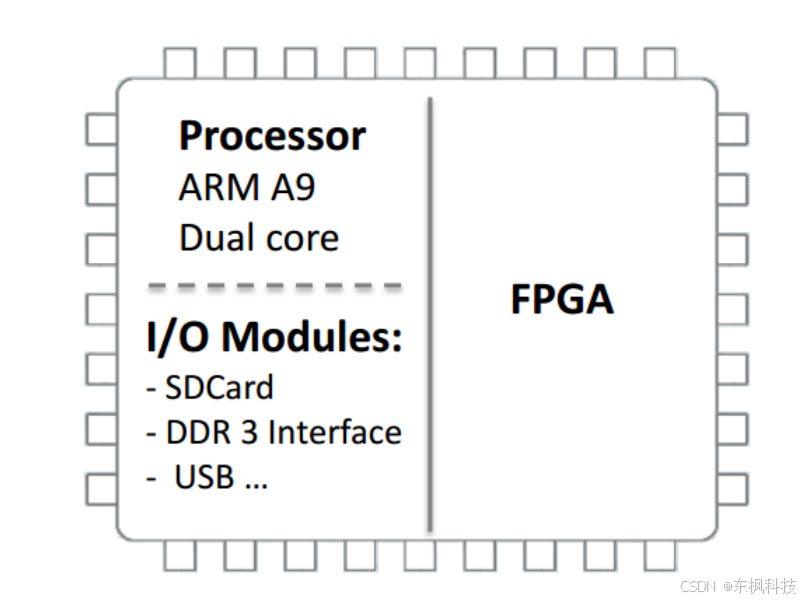

微電子技術的最新發展催生了一種新型微芯片,它將 FPGA 和處理器集成在單個芯片上。FPGA 制造商 Xilinx 推出了 Zynq 器件,而其競爭對手 Altera 則推出了 Altera SoC 系列。這兩款芯片在系統結構和性能上非常相似。下文我們將重點介紹 Xilinx Zynq,但許多細節也適用于 Altera SoC。

這些新型混合系統屬于片上系統 (SoC)。SoC 由多個截然不同的組件組成,例如處理器、存儲器、I/O 模塊、加速器等,這些組件集成在單個芯片上。這降低了成本和尺寸,并提供了組件之間緊密而快速的交互。

微控制器以及廣為人知的 Raspberry PI 都屬于 SoC。 Zynq 也是一款 SoC,因為它包含一個雙 ARM A9 內核、一個 FPGA 以及用于不同 I/O 的附加模塊(例如 DDR3 內存接口、USB、SD 卡控制器)。處理器和 FPGA 之間有數千種可能的內部連接,這些連接可編程,并支持快速數據傳輸。這比 PCB 上 FPGA 和處理器的單獨組合具有很大的優勢,因為 PCB 設計完成后,可能的連接數量很少,而且很難更改。Zynq 有六種不同的尺寸(Z-7010 至 Z-7100)。所有型號都包含一個雙 ARM A9 內核,但 FPGA 部分的尺寸差異很大。

Zynq 的編程包含兩個任務:處理器編程和 FPGA 數字電路設計。

這兩個任務幾乎可以通過不同的工具獨立完成。

處理器編程

處理器可以通過裸機編程或使用操作系統進行編程。裸機編程是指直接使用 C 語言對 ARM 處理器進行編程,無需任何操作系統,例如使用 Xilinx SDK 工具。然而,強烈建議使用 Linux 之類的操作系統,它通過使用硬件抽象層 (HAL) 隱藏了處理器的許多細節,并可以輕松訪問接口和標準 Linux 軟件。

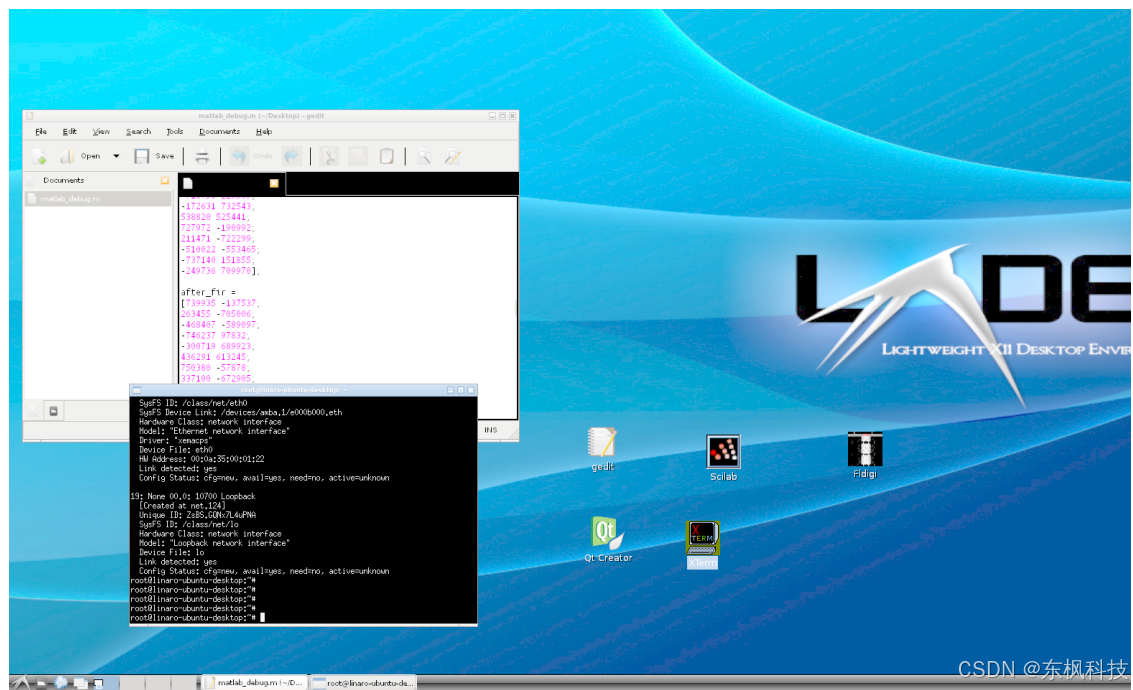

Linux 發行版(例如 Ubuntu/Linaro)可以作為操作系統安裝在 SD 卡上,SD 卡也可用作文件系統。可以通過網絡接口(例如通過 SSH 或 RDP)或直接連接顯示器、鍵盤和鼠標(作為獨立系統使用)訪問處理器。然后就可以使用標準軟件了(Linux 軟件包管理器提供或手動編譯)。像 SciLab(數學工具箱)或強大的解調軟件 Fldigi 這樣的軟件可以直接通過軟件包管理器安裝。編程可以使用多種語言進行,例如 C/C++、Qt、Python、Java 等。QtCreator 可以作為編程編輯器,它可以直接在 Zynq 上運行,無需繁瑣的交叉編譯。

FPGA 設計

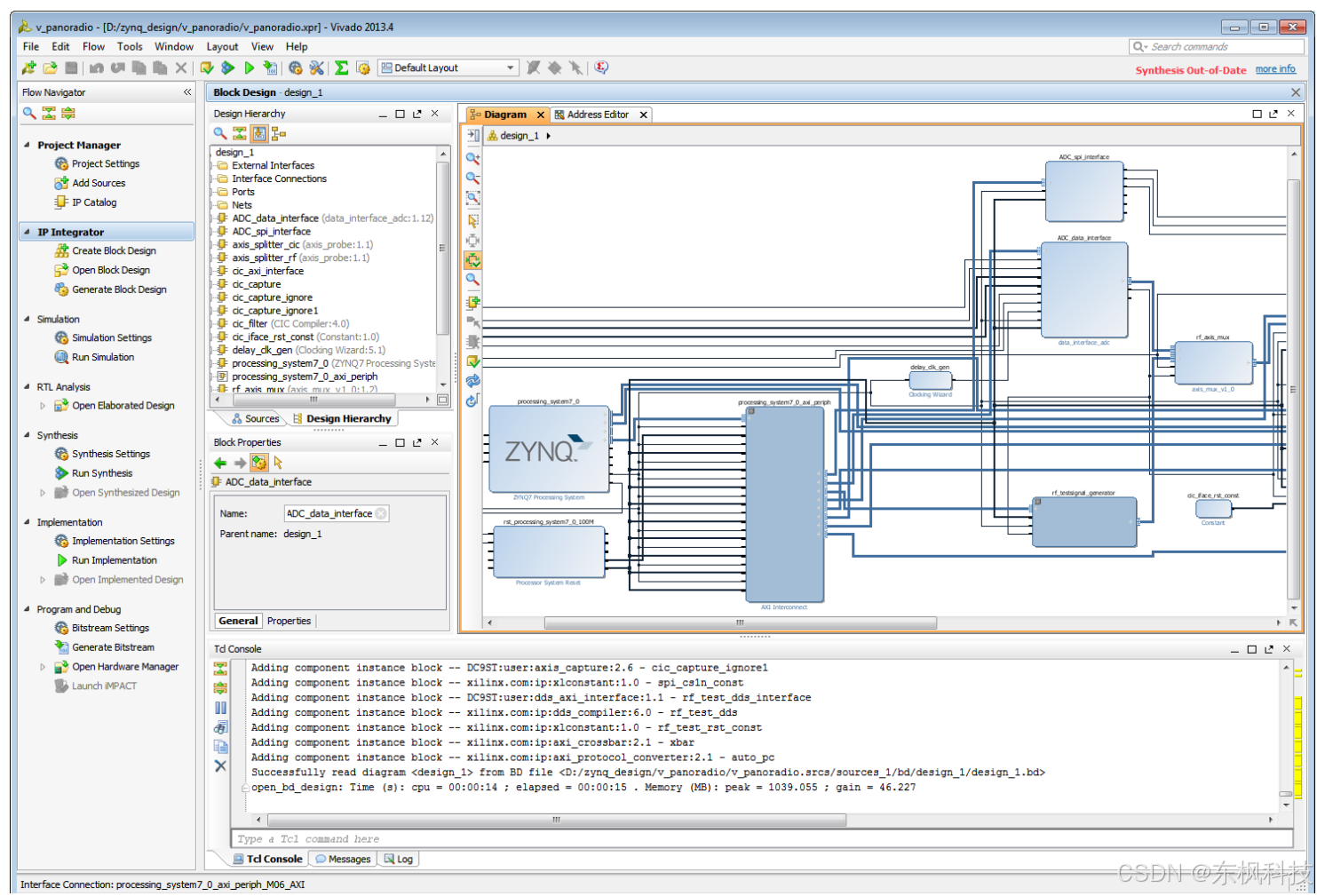

最具挑戰性的部分是 FPGA 的硬件設計。Xilinx 提供了一款名為“Vivado”的設計工具。

Vivado 的基本功能是免費的,Zedboard 評估板附帶了額外的調試功能(Vivado 邏輯分析儀)許可證。這些工具足以滿足 Zynq 的大多數設計需求。SDR 設計可以使用 Vivado 模塊設計工具來完成,該工具是一個頂層原理圖,用于連接不同的模塊。這些模塊包含主要功能,并且可以采用不同的設計方式。一種是使用硬件描述語言,例如 VHDL 或 Verilog。另一種選擇是依賴高級綜合,例如 Vivado HLS 或基于 Matlab 的工具(System Generator、HDL Coder),這些工具的主要目的是將 C 或 Matlab 代碼轉換為數字電路。

值得一提的是,Xilinx 提供了一些預定義的硬件組件,這些組件對于構建 SDR 非常有用:一個基于直接數字合成 (DDS) 的正弦信號發生器,可以進行參數化 [1]。頻率范圍、分辨率、位寬、時鐘速度和無雜散動態范圍 (SFDR) 均可選擇。可以輕松獲得 150 dB 的 SFDR。另一個有用的硬件模塊是 FIR 濾波器編譯器,它可以輕松實現 FIR 濾波器 [2]。許多硬件參數可供選擇,濾波器系數的設計本身可以使用 Matlab 等工具完成。

FPGA 硬件設計需要豐富的硬件設計和數字電路知識和經驗。

此外,經驗表明,Vivado 工具有時似乎相當不成熟且使用起來不夠直觀。

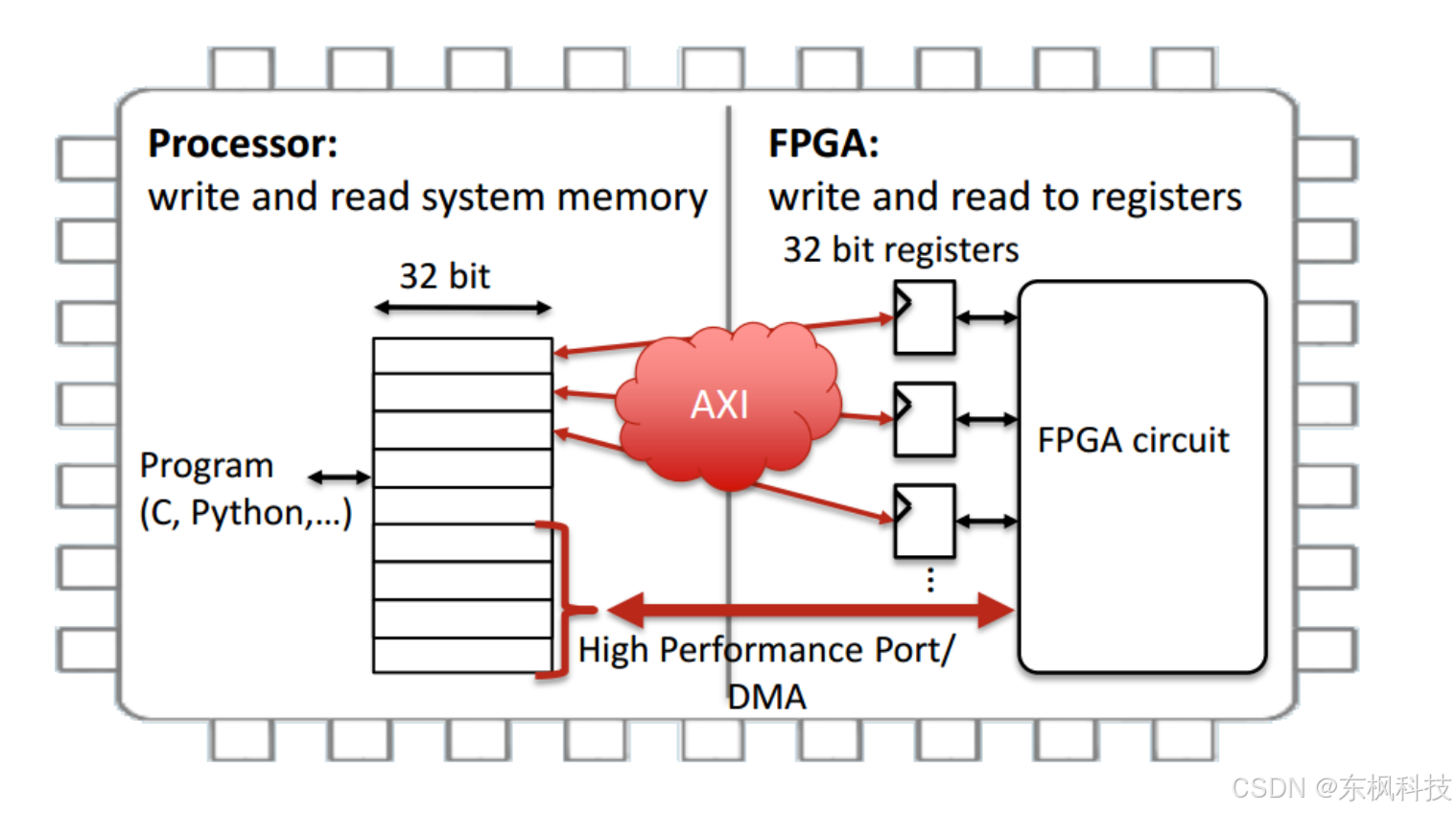

互連工作原理

如上所述,Zynq 在處理器和 FPGA 之間提供了數千個互連,用于這些互連能夠正常工作。

互連是一種內存映射接口。這意味著,處理器內存的一段32位數據會虛擬連接到FPGA中的一個32位寄存器。

處理器可以將數據寫入這個特殊的內存片段,然后這些數據會立即傳輸到FPGA寄存器。或者,處理器可以通過從內存中讀取數據來讀取FPGA中的寄存器。從FPGA的角度來看,數據傳輸只需讀寫32位寄存器即可完成。

雖然移動數據聽起來并不復雜,對于程序員來說也確實如此,但它卻涉及一個基于 AXI 標準的相當復雜的過程,幸運的是,該標準對用戶來說基本是隱藏的。

如果需要傳輸大量數據,可以使用直接內存訪問 (DMA)。這樣,通過使用 Zynq 的高性能 (HP) 或加速器一致性 (ACP) 端口,數據傳輸速度會更快。

重新配置

如果使用重新配置,Zynq 的另一個優勢就會顯現出來。如上所述,FPGA 中的數字電路可以更改。使用 Xilinx Vivado 工具設計數字電路時,設計會存儲在一個文件(.bit 或有時為 .bin)中,稱為比特流。上電后,FPGA 為空,可以將設計電路的比特流加載到芯片上,使 FPGA 正常工作。可以預先設計不同的硬件電路,并將它們存儲在不同的比特流文件中。這些比特流可以在運行時交換。這個過程稱為重新配置。重新配置只需幾毫秒即可完全改變 FPGA 中的電路。獨立的 FPGA 需要相當大的開銷來進行重新配置。設計文件首先必須以某種方式傳輸到 PCB 上的額外存儲器中。之后,每當觸發重新配置時,都需要再次傳輸到 FPGA,這就需要額外的邏輯(例如微控制器)。Zynq 消除了這種開銷,因為比特流文件可以存儲在 SD 卡或遠程計算機上的 Linux 文件系統中,并通過處理器傳輸到 FPGA。在 Linux 中,整個重新配置過程只需執行一條命令:cat new_bitstream.bin > /dev/xdevcfg。這為 SDR 開辟了新的可能性,因為高速數字電路可以在運行過程中進行更改。它們可以根據所需的無線電工作模式、頻譜環境或所使用的傳輸模式進行調整,這些模式在認知無線電和自適應無線電等現代無線電技術中也得到了充分考慮。

III. ZEDBOARD

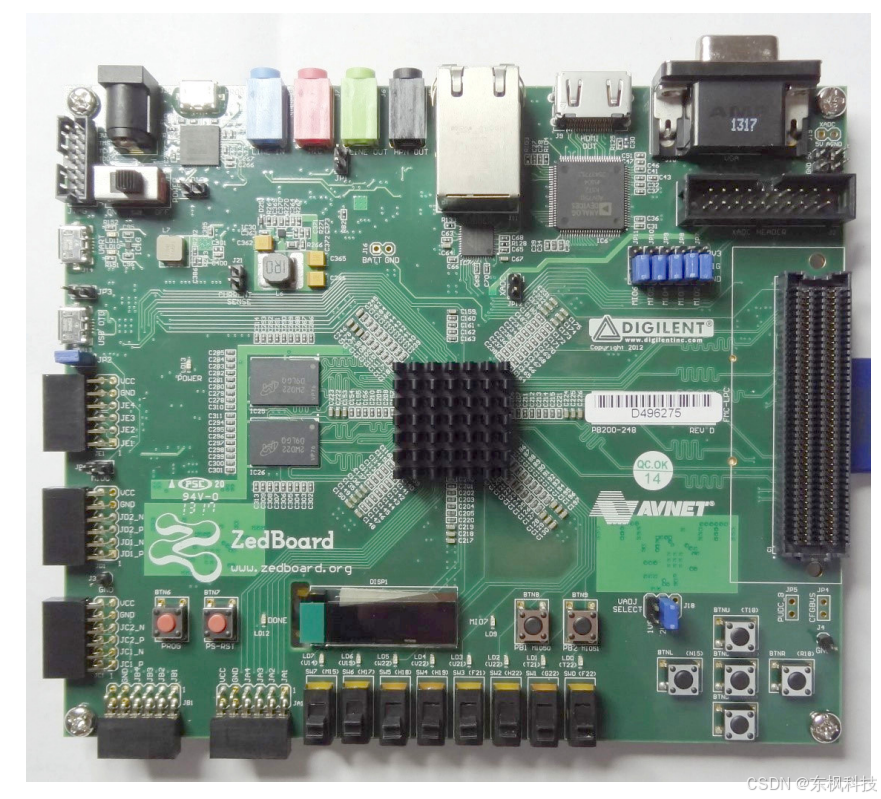

Zedboard 是一款用于 Xilinx Zynq 器件的低成本評估板。它包含許多外設,可以充分發揮 Zynq 的強大功能,例如電源、內存和眾多接口。

Zedboard 的具體功能包括:

? 512 MB DDR3 內存

? 千兆以太網

? USB OTG 和 USB UART

? HDMI 接口

? VGA 接口

? OLED 顯示屏

? SD 卡插槽

? GPIO 引腳、按鈕和 LED

? FMC 接口

? ADAU 1761 音頻接口

? 板載時鐘發生器

這些外設使 Zedboard 成為一個完全獨立的系統。可以連接顯示器、鼠標、鍵盤和耳機,并建立互聯網連接。

Zedboard 是實驗者的理想選擇,因為它提供了豐富的功能。它是許多不同應用的理想平臺,例如圖像處理、控制系統、算法加速以及軟件無線電 (SDR)。此外,www.zedboard.org 上有一個龐大的在線社區。教程、示例項目和論壇可供初學者使用。

圖 6. Zedboard

Zedboard 初學者。此外,該板的原理圖也已發布,可免費下載。

由于 Zedboard 本身不包含任何適用于 SDR 的 ADC 或 DAC,因此需要連接無線電模塊。FMC 連接器是理想的選擇。許多公司,例如 Analog Devices、Texas Instruments 或 Linear Technology,都提供帶有 FMC 接口的子板。這些板可以輕松連接到 Zedboard。Zedboard 相對于許多其他 SDR 平臺的優勢在于,無線電模塊并非固定的。用戶可以根據需求和預算進行選擇。更換 FMC 開發板并創建具有全新 ADC/DAC 系統的無線電系統非常容易。

除了“經典”的 Zedboard 之外,市場上還出現了更多 Zynq 開發板。值得一提的是 MicroZed 和 Zybo,因為它們價格更便宜,并且提供類似的功能。但需要指出的是,這些開發板沒有完整的 FMC 連接器。這使得連接 ADC 和 DAC 以創建完整的 SDR 平臺變得更加困難。

IV. 使用 ZYNQ 的現代軟件無線電 (SDRS) 示例

如前所述,Zynq 非常適合 SDR 應用的需求。這也是它已被應用于現代 SDR 的原因,下文將介紹其中一些。

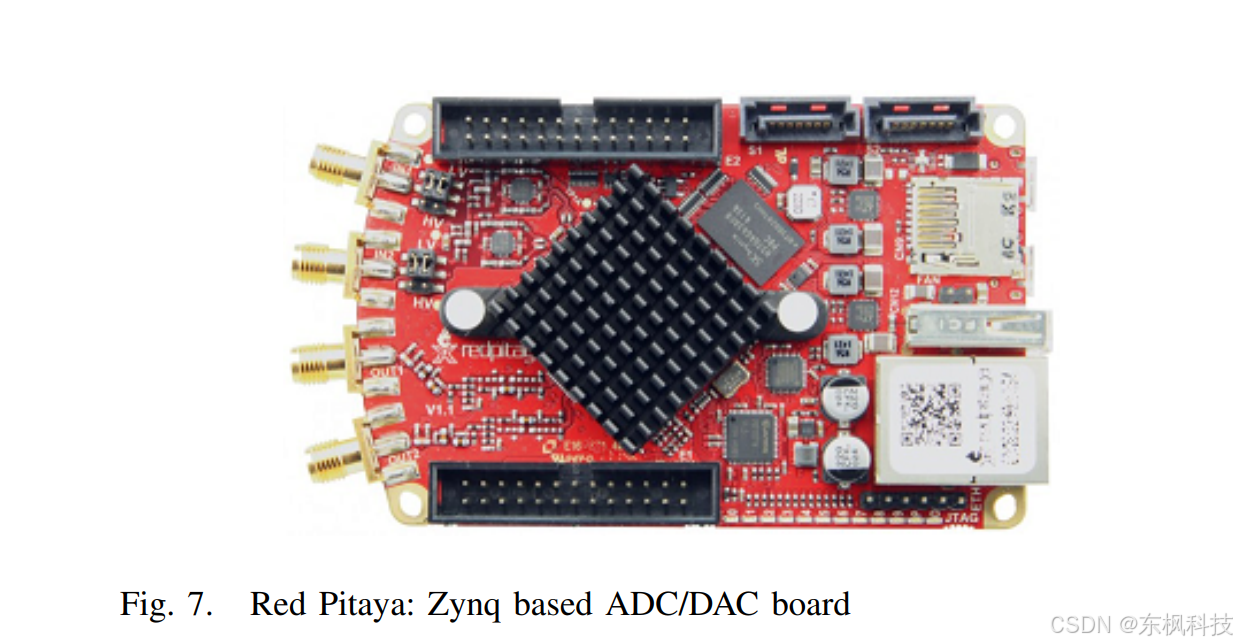

Red Pitaya

Red Pitaya 被開發為一款測量設備(示波器、頻譜分析儀、信號發生器)[3]。

它具有一個帶有 14 位 ADC 的雙通道輸入和一個帶有 14 位 DAC 的雙通道輸出。它是一個 125 Msps 的直接采樣接收器,可捕獲高達 50 MHz 的信號。信號處理依賴于 Zynq 7010,它是 Zynq 系列中最小的器件。該芯片運行 Linux,允許通過 LAN 連接 PC 或平板電腦,并提供與 C++、Matlab 或 Labview 的接口。它聲稱是開源的,但目前僅限于軟件部分。Red Pitaya 雖然是為測量應用而設計的,但它已轉換為完整的 SDR 系統 [4]。

Zepto SDR

Zepto SDR 由 Nutaq 開發,由 Zedboard 和 FMC 擴展板(Radio420S FMC)[5] 組成。它使用 12 位 ADC 和 DAC 轉換器,工作頻率范圍為 0.3 至 3 GHz。最大處理帶寬為 28 MHz。建議在 Zynq 上運行 GNU 無線電。

USRP E310

USRP E310 是 Ettus 著名 USRP 的嵌入式系列產品之一 [6]。由于采用了 Zynq 7020(尺寸與 Zedboard 相同),它是一款獨立設備。雙通道模擬前端支持 70 MHz 至 6 GHz 的頻率范圍,最大帶寬為 56 MHz。

R2T2

R2T2 是一款直接采樣收發器,具有兩個接收通道和兩個發送通道 [7]。它配備兩個 14 位 ADC(采樣率為 125 Msps)和 14 位 DAC(采樣率為 250 Msps)。它提供與 Zedboard 類似的處理功能:配備 DDR3 內存的 Zynq 7020、千兆以太網、HDMI、USB、SD 卡以及音頻編解碼器 ADAU1791。最多 8 位用戶可以通過 Web 界面遠程使用該 SDR [7]。

V. PANORADIO SDR:高速直接采樣接收器的技術演示

A. 概述

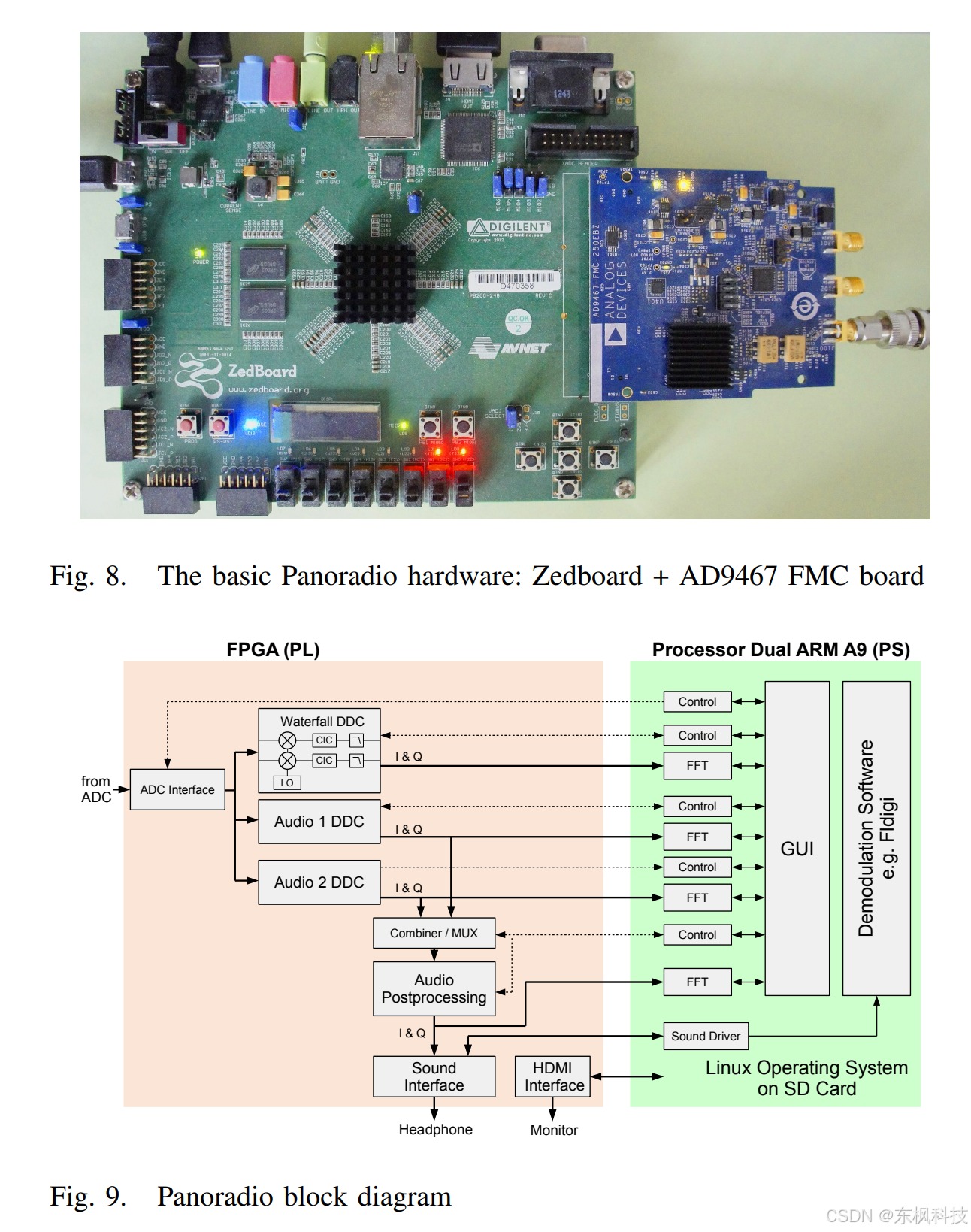

為了向實驗者展示其當今的各種可能性,我們開發了一個技術演示——Panoradio SDR。它包含一個 Zedboard,附帶一個內置高速 AD9467 ADC 的 FMC 卡,該 ADC 以 16 位分辨率和 250 Msps 的采樣率對模擬信號進行采樣 [8]。由于其精度高且采樣率高,它可以直接在天線后拾取信號,無需任何模擬下變頻,相當于一個直接采樣接收器。由于采樣率高,可以拾取并即時顯示高達 125 MHz 的帶寬(如果需要抗混疊濾波器,帶寬會降至

約 100 MHz)。

B. 功能

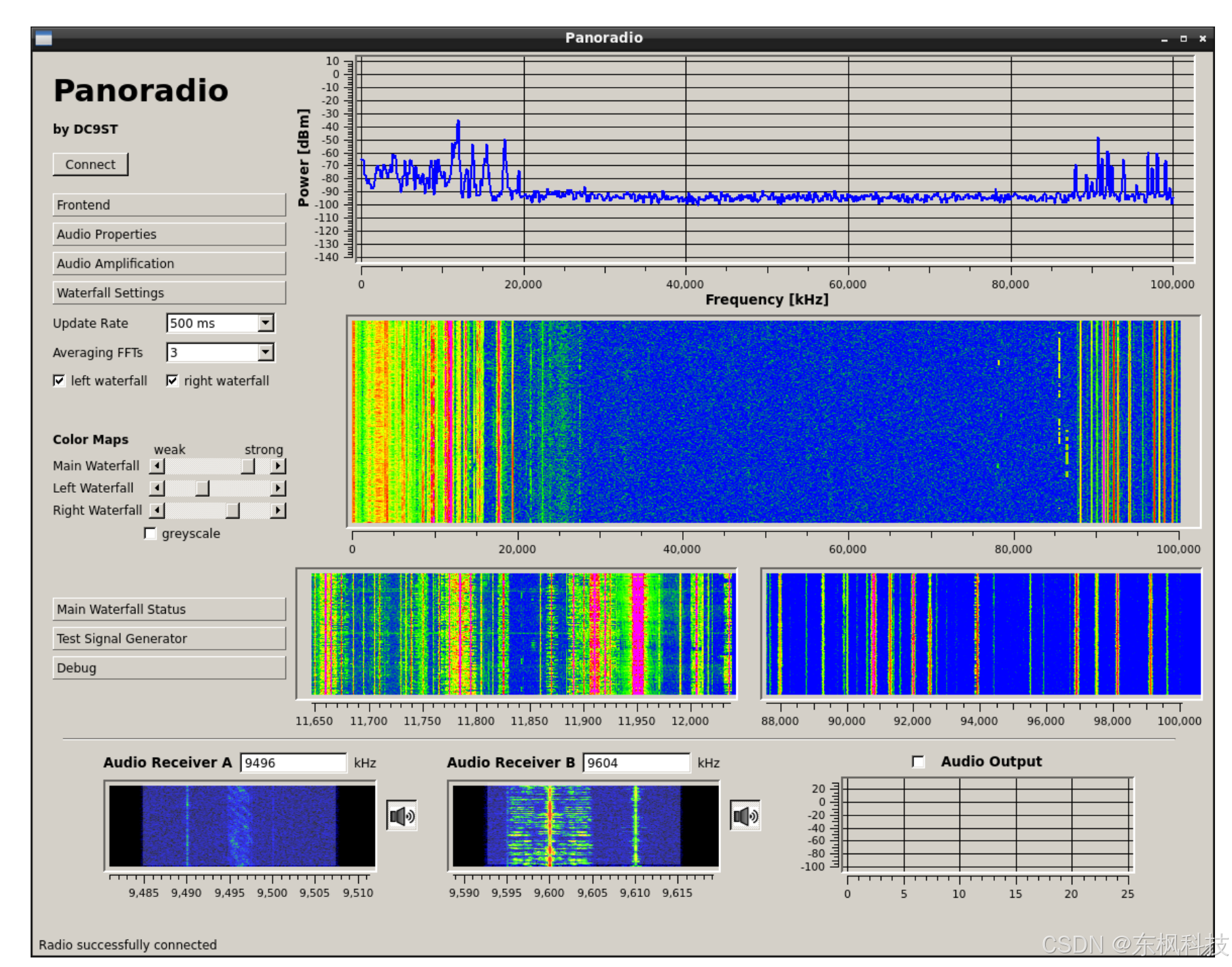

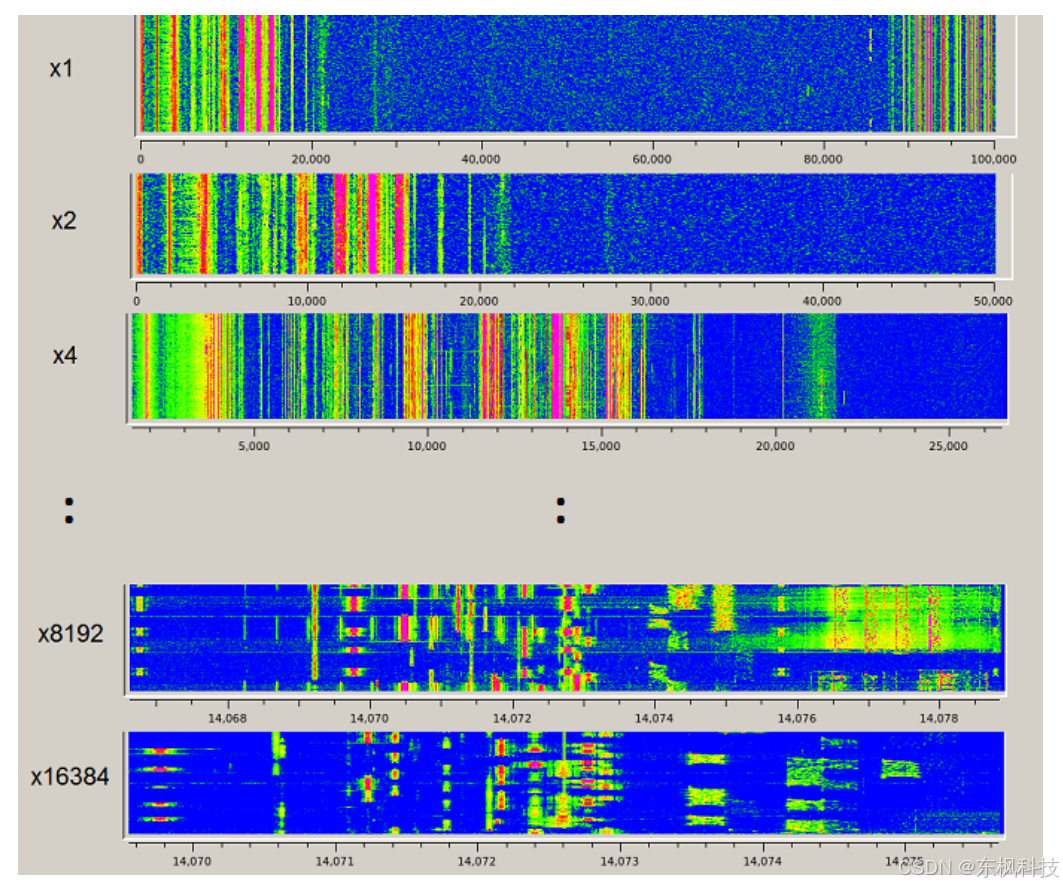

Panoradio 提供三個可縮放的全景圖或瀑布圖顯示,帶寬高達 100 MHz,并經過了

適當的抗混疊濾波處理。全景圖顯示可以獨立縮放至 6 kHz 的帶寬,從而提供低至 7 Hz 的最低分辨率。三個全景顯示可以同時觀察非常大頻率范圍內的不同頻段。例如,可以輕松同時觀察80米、10米和4米波段的信號。由于Zedboard上運行操作系統,用于控制無線電的軟件直接在接收器上運行,因此使其成為一個獨立的嵌入式系統,并且可以直接連接鼠標、顯示器和鍵盤。此外,諸如流行的Fldigi [9]等解調軟件也可以直接在無線電上運行。Panoradio還可以用作FFT頻譜分析儀。它的頻率范圍可以輕松檢查短波信號。由于ADC的SFDR高達100 dBFS [8],因此雜散預計會非常低。除了全景顯示外,還提供兩個獨立的音頻接收器。每個音頻接收器的帶寬為 22 kHz(可選 6 kHz 或 3 kHz),其信號頻譜以瀑布圖的形式顯示。音頻輸出可以直接復用或混合到 Zedboard 音頻編解碼器的耳機輸出和處理器的音頻接口(在 Linux 中顯示為聲卡設備)。此外,音頻接收器可以獨立且即時地調諧到 0 至 100 MHz 之間的任何頻率。

C. 描述

Panoradio 的結構如圖 9 所示。該設計分為在 FPGA 上完成的高速處理部分和在 Zynq 處理器部分完成的軟件處理部分。

圖 10. Panoradio 軟件及其圖形用戶界面:主瀑布圖顯示了從 0 到 100 MHz 的完整頻段。短波信號僅占據整個頻段左側的一小部分。88 MHz 以上的信號為調頻廣播電臺,88 MHz 以下的零星發射屬于應急服務。左側小瀑布圖顯示了 15 米的廣播頻段。右側小瀑布圖放大顯示了甚高頻 (VHF) 廣播信號。

FPGA 處理:來自 ADC 的數據樣本通過 ADC 接口模塊輸入 FPGA。該模塊執行一些 ADC 測試,處理線路延遲,并將差分雙倍數據速率信號轉換為可在 FPGA 中處理的單端數據。然后,這些樣本被送入三個數字下變頻 (DDC) 模塊,其中一個用于瀑布顯示器,另外兩個用于音頻接收器。每個 DDC 包含一個復數乘法器(用作 IQ 混頻器)、DDS 本振以及一對 CIC 和 FIR 濾波器(用于抽取和帶寬縮減)。瀑布 DDC 提供可縮放的全景圖功能。縮放功能由速率可編程的 CIC 濾波器實現。對于所有三個瀑布顯示器,僅使用一個接收器,該接收器在顯示器之間進行復用。然后,其接收頻率每秒多次切換到每個瀑布顯示器的中心頻率。音頻 DDC 的輸出 IQ 帶寬為 22 kHz。隨后,音頻數據在音頻后處理模塊中進一步處理,該模塊包含用于進一步降低帶寬(從 22 kHz 降至 6 kHz 或 3 kHz)的濾波器和用于 SSB 接收的 Weaver 解調器。最后,音頻接口將音頻 IQ 數據發送到耳機輸出和處理器。

軟件處理:處理器在 SD 卡上運行 Linaro/Ubuntu Linux 操作系統。應用程序編程使用 C++ 完成。此外,還使用了一些附加庫:Qt 和 Qwt [10] 用于圖形用戶界面,FFTW [11] 用于快速 FFT 處理。軟件和處理器的任務主要是控制 FPGA 設計的功能并為用戶提供接口。

FPGA 接口包括:從 DDC 讀取 IQ 數據用于 FFT,初始化 ADC 和音頻接口,設置 DDC 頻率和濾波器屬性,在系統啟動時加載 FPGA 設計,確定 ADC 的放大倍數。

圖 12. 縮放功能允許檢查小帶寬信號,

此處顯示的是 20 米業余無線電頻段的數字信號,包括一些

PSK31 傳輸。

和音頻接口。此外,瀑布圖的 FFT 計算(包括加窗、平均、抽取等)由處理器通過軟件完成。此外,

處理器提供以太網和 UART 作為用戶接口,顯示 GUI 并處理用戶輸入。

D. 未來發展方向

由于 AD9467 的模擬接口可以在

1 GHz 以上的頻率下工作,因此如果應用適當的模擬濾波,欠采樣可用于

接收遠高于奈奎斯特頻率 125 MHz 的頻率。這為直接采樣當今業余無線電中考慮的更高頻率提供了新的機會。然而,必須考慮相位噪聲

的衰減。

Panoradio 仍在開發中,并將持續發展。更多信息請訪問項目網站 www.panoradio-sdr.de。

六、結論

高性能 SDR 對其底層硬件平臺提出了挑戰性的要求。硬件需要提供高處理速度、靈活性和用戶界面。現代 SoC,例如 Xilinx

Zynq 和 Altera SoC 系列,在單芯片上同時提供這兩種功能。事實上,Zynq 已經在多個 SDR 項目中使用,而且由于價格實惠的 Zedboard 的推出,它也吸引了實驗者的興趣。作為技術演示,Panoradio SDR 已在本次演示中展示。它是一款基于 Zedboard 的 250 Msps 直接采樣接收器,展示了這些新設備的性能。

復現利用)

+ 二叉樹)

-介紹)

--配置使用RabbitMQ)