一、參考說明

1.沒有專門對AXI4-Stream Clock Converter IP說明的文檔;

2.可以參考PG085文檔;

3.可以參考PG035文檔;

二、IP的作用

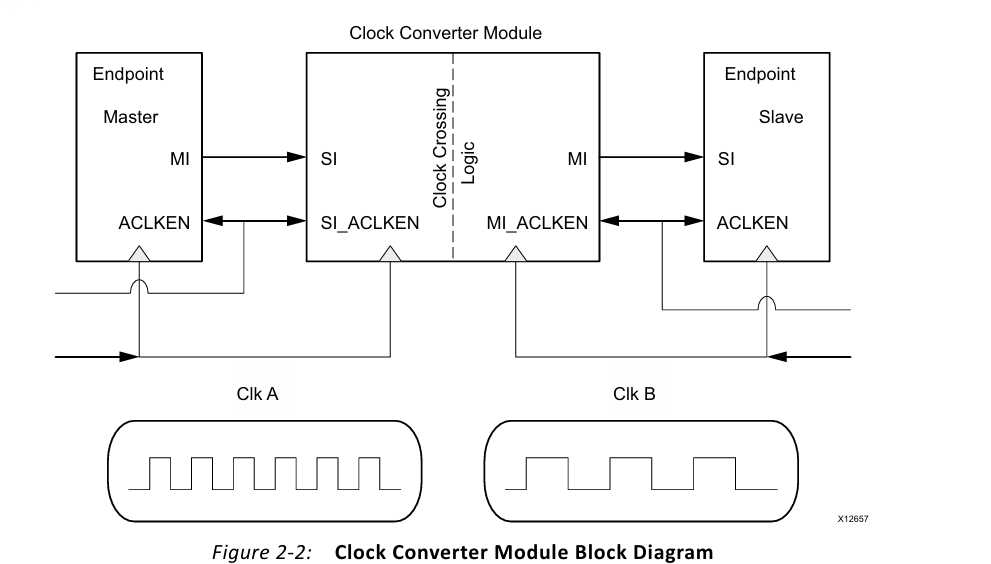

1.用于stream數據流再不同的時鐘域之間的可靠性傳輸;

2.支持跨時鐘域的場景;

3.內部使用FIFO或者寄存器Register slice管道實現數據同步;

三、注意問題

1.FIFO模式下,輸入和輸出的頻率不需要嚴格匹配,建議的是out_clk_freq >= 0.75*in_clk_req,避免FIFO溢出

2.寄存器管道模式register slice要求輸入和輸出時鐘頻率要接近,以確保數據同步的可靠性;

四、FIFO的深度

1.FIFO深度需根據數據突發長度和時鐘頻率差選擇,過小的深度可能導致背壓或數據丟失;

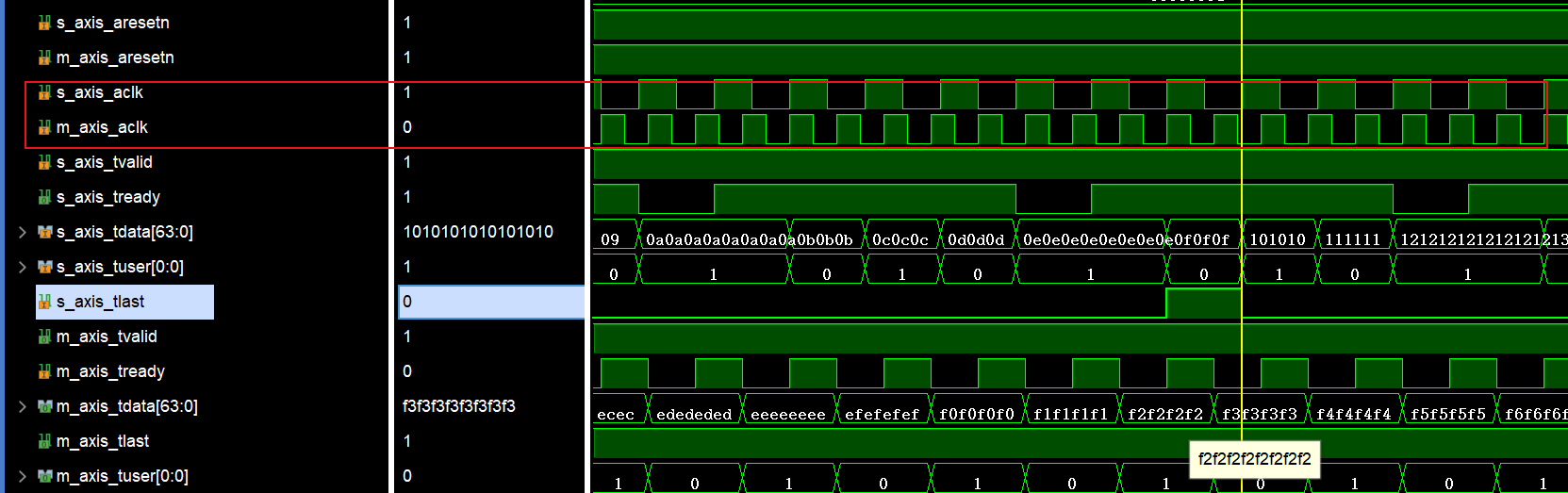

五、125MHZ--->200MHZ跨時鐘仿真

與鏡像(Image)的區別與聯系)

)

)