博圖 SCL 編程技巧:靈活實現上升沿與下降沿檢測案例分享

在 PLC 編程中,檢測信號從?0?變為?1?(上升沿) 或從?1?變為?0?(下降沿) 是最基礎也是最關鍵的操作之一。它常用于啟動單次動作、計數、狀態切換等場景。在西門子 TIA Portal 環境中,雖然梯形圖 (LAD) 提供了直觀的?P?(上升沿) 和?N?(下降沿) 指令,但在?SCL (結構化控制語言)?中,我們擁有更靈活和強大的實現方式。本文將分享幾種在 SCL 中實現邊沿檢測的方法及其適用場景。

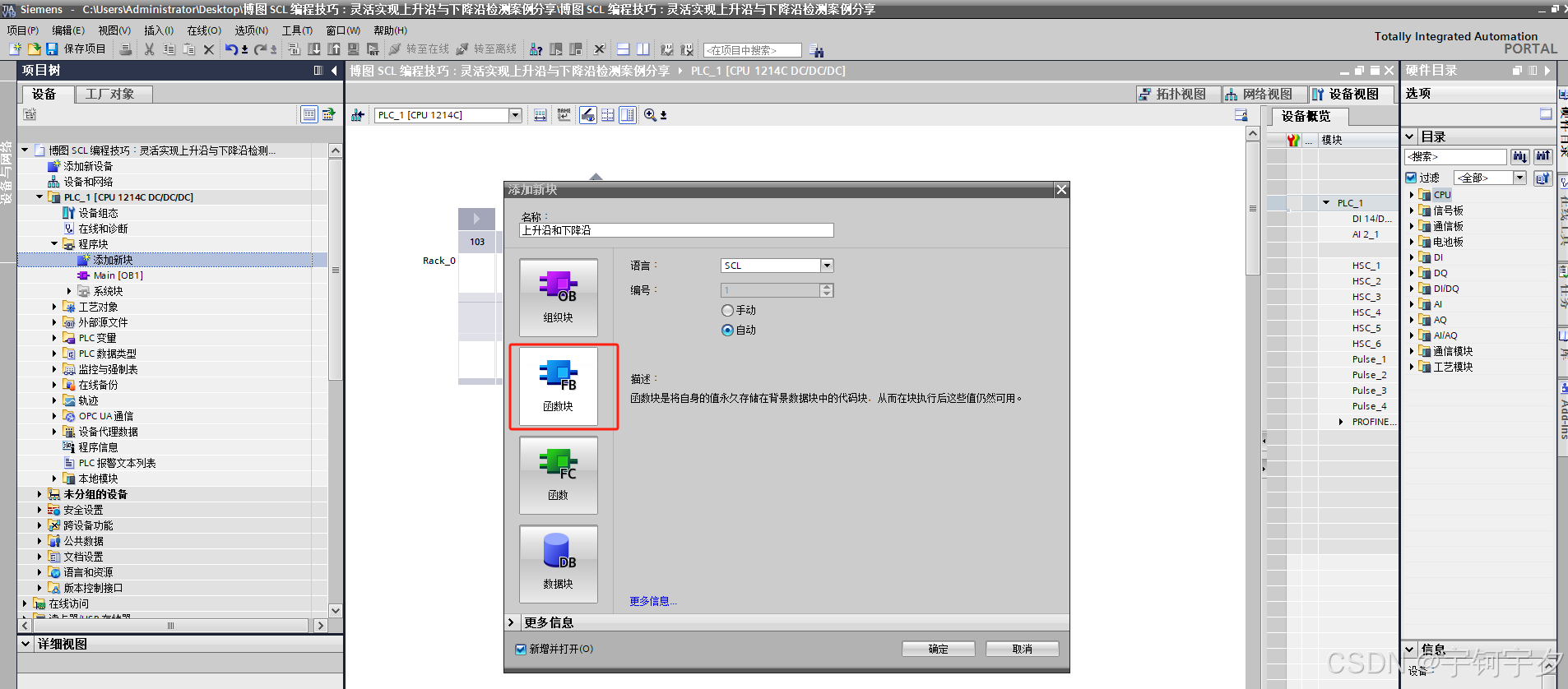

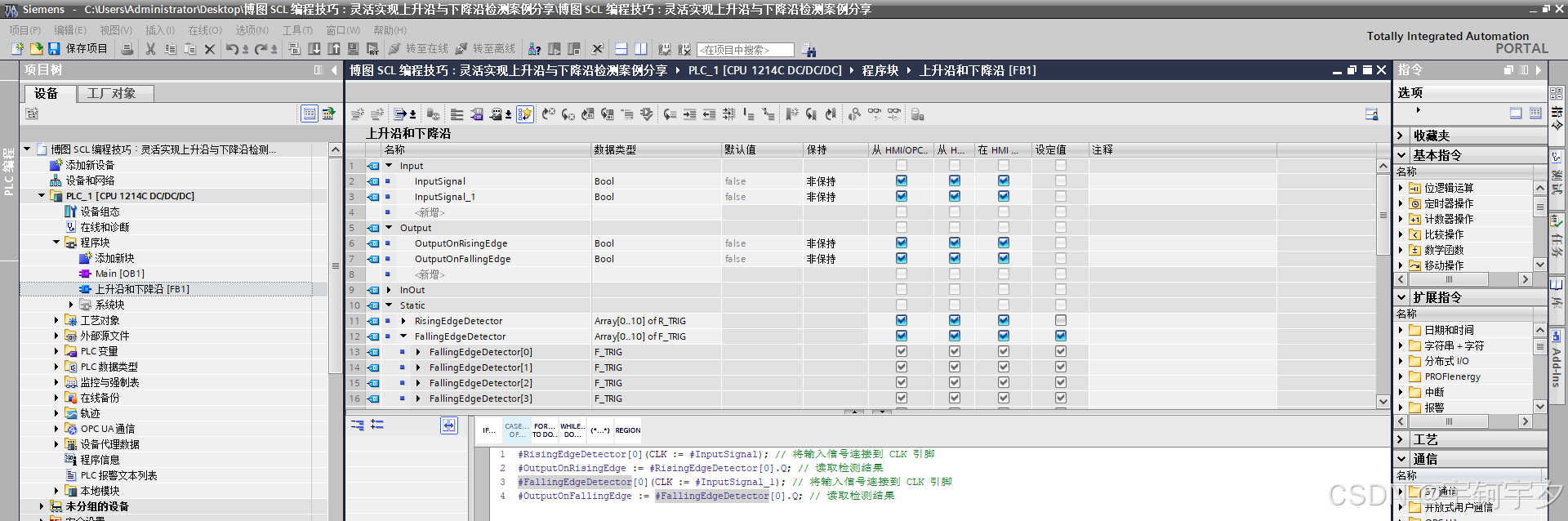

方法 1:使用標準系統函數塊 (R_TRIG / F_TRIG)

這是最推薦、最符合 IEC 61131-3 標準且資源管理最清晰的方式。TIA Portal 提供了現成的邊沿檢測函數塊。

1.1 上升沿檢測 (R_TRIG)l

VAR// 輸入信號InputSignal: BOOL;// 實例化上升沿檢測塊RisingEdgeDetector: R_TRIG;// 輸出 (檢測到上升沿時為 TRUE)OutputOnRisingEdge: BOOL; END_VAR

// 主執行邏輯 RisingEdgeDetector(CLK := InputSignal); // 將輸入信號連接到 CLK 引腳 OutputOnRisingEdge := RisingEdgeDetector.Q; // 讀取檢測結果

1.2 下降沿檢測 (F_TRIG)

VAR// 輸入信號InputSignal_1: BOOL;// 實例化下降沿檢測塊FallingEdgeDetector: F_TRIG;// 輸出 (檢測到下降沿時為 TRUE)OutputOnFallingEdge: BOOL; END_VAR// 主執行邏輯 FallingEdgeDetector(CLK := InputSignal_1); // 將輸入信號連接到 CLK 引腳 OutputOnFallingEdge := FallingEdgeDetector.Q; // 讀取檢測結果

優點:

-

標準化:?符合國際標準,代碼可讀性高。

-

封裝性:?邊沿檢測邏輯被封裝在塊內,隱藏了內部狀態。

-

易維護:?塊自動管理其內部存儲(通常是靜態變量),無需用戶手動聲明“上次狀態”。

-

多實例化:?同一個函數塊可以輕松創建多個實例檢測不同信號。

缺點:

-

需要實例化一個單獨的塊,稍微增加一點代碼量(但通常可以忽略)。

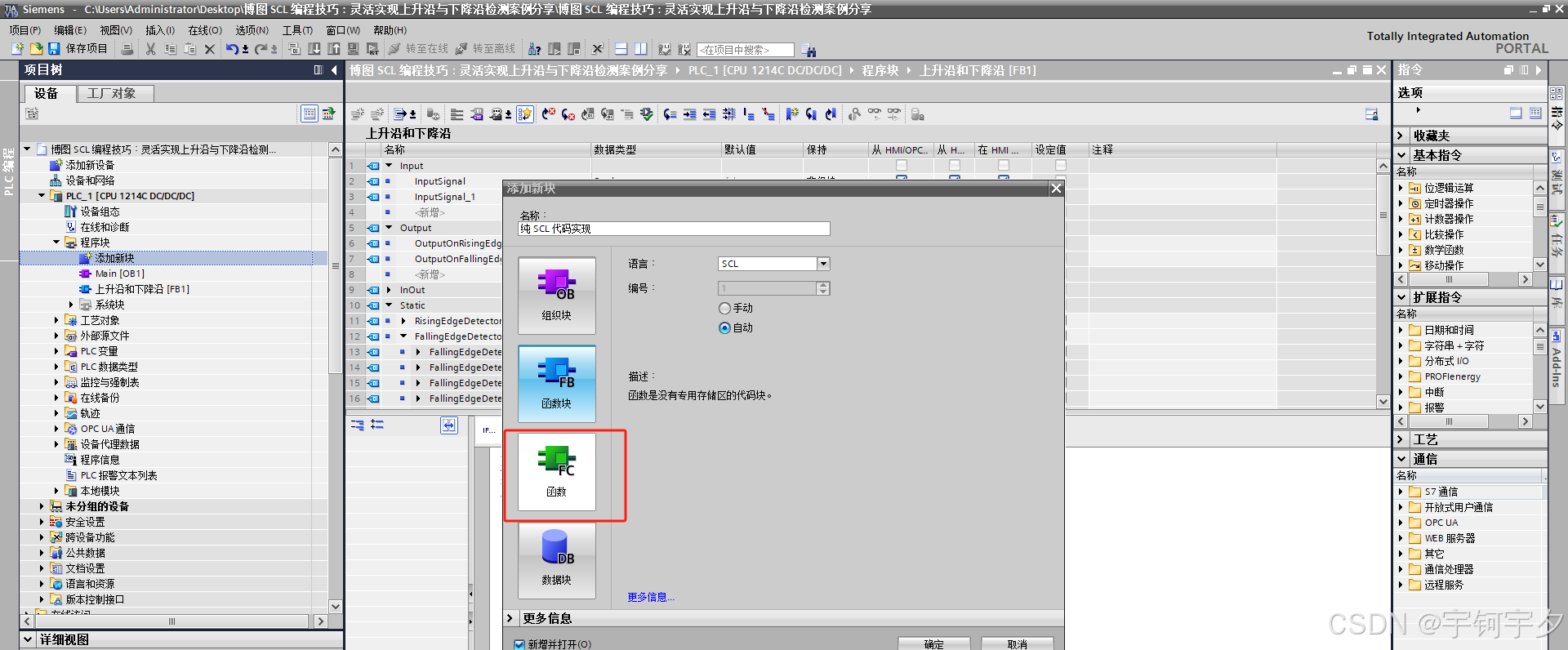

方法 2:純 SCL 代碼實現 (使用靜態變量存儲上次狀態)

如果你不想實例化額外的塊,或者需要在簡單邏輯中快速實現,可以直接用 SCL 代碼編寫邊沿檢測邏輯。核心是使用靜態變量 (STATIC) 保存信號在上一掃描周期的狀態。

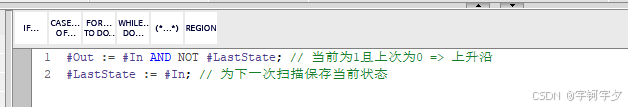

2.1 上升沿檢測 (純 SCL)

scl

VAR_INPUTIn: BOOL; // 輸入信號 END_VAR VAR_OUTPUTOut: BOOL; // 檢測到上升沿輸出 TRUE (僅一個周期) END_VAR VARLastState: BOOL := FALSE; // STATIC 變量 (默認初始化 FALSE) 存儲上一次狀態 END_VAR

// 主執行邏輯 Out := In AND NOT LastState; // 當前為1且上次為0 => 上升沿 LastState := In; // 為下一次掃描保存當前狀態

2.2 下降沿檢測 (純 SCL)

scl

VAR_INPUTIn_1: BOOL; // 輸入信號 END_VAR VAR_OUTPUTOut_1: BOOL; // 檢測到下降沿輸出 TRUE (僅一個周期) END_VARVARLastState_1: BOOL := FALSE; // STATIC 變量 (默認初始化 FALSE) 存儲上一次狀態 END_VAR

// 主執行邏輯 Out_1 := NOT In_1 AND LastState_1; // 當前為0且上次為1 => 下降沿 LastState_1 := In_1; // 為下一次掃描保存當前狀態

優點:

-

簡潔:?對于單個信號的簡單檢測,代碼非常緊湊。

-

無額外實例:?不需要創建?

R_TRIG/F_TRIG?實例。 -

理解底層原理:?幫助理解邊沿檢測的本質。

缺點:

-

狀態管理:?需要手動聲明和管理靜態變量?

LastState。 -

可讀性稍差:?對于不熟悉此模式的讀者,不如直接調用函數塊直觀。

-

復用性差:?如果需要檢測多個信號,需要為每個信號復制一份類似的代碼(聲明單獨的?

LastState),不如函數塊實例化方便。 -

易出錯:?如果忘記更新?

LastState?或在錯誤的位置更新,會導致邏輯錯誤。

)

![正點原子[第三期]Arm(iMX6U)Linux移植學習筆記-12.1 Linux內核啟動流程簡介](http://pic.xiahunao.cn/正點原子[第三期]Arm(iMX6U)Linux移植學習筆記-12.1 Linux內核啟動流程簡介)

:濾鏡命令)

結構的影響)