相關閱讀

SDC命令詳解![]() https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

目錄

????????指定端口列表/集合

????????簡單使用

????????注意事項

????????傳播時鐘是在進行了時鐘樹綜合后,使用set_propagated_clock命令可以將一個理想時鐘轉換為傳播時鐘(注意,虛擬時鐘即無時鐘源對象的時鐘無法被轉換為傳播時鐘)(設置對象的propagated_clock屬性為true),此時的時鐘延遲由源延遲和真實網絡延遲組成,這里的網絡延遲是根據時鐘路徑上的線延遲和單元延遲真實計算出來的,而不再使用set_clock_latency命令設置網絡延時。有關理想時鐘和傳播時鐘的更詳細內容,可以參考下面的博客。如果想要移除傳播時鐘,使用remove_propagated_clock命令。

靜態時序分析:ideal_clock、propagated_clock以及generated_clock的關系及其延遲計算規則(一)![]() https://blog.csdn.net/weixin_45791458/article/details/139998035?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522e4f4bf160af3c2b2f079b3291ac96a32%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=e4f4bf160af3c2b2f079b3291ac96a32&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-139998035-null-null.nonecase&utm_term=%E4%BC%A0%E6%92%AD%E6%97%B6%E9%92%9F&spm=1018.2226.3001.4450????????本文針對Design Compiler,但該命令同樣存在于PrimeTime、IC Compiler等工具中,它們大致相同,略有差別。set_fanout_load命令的BNF范式(有關BNF范式,可以參考以往文章)為:

https://blog.csdn.net/weixin_45791458/article/details/139998035?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522e4f4bf160af3c2b2f079b3291ac96a32%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=e4f4bf160af3c2b2f079b3291ac96a32&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-139998035-null-null.nonecase&utm_term=%E4%BC%A0%E6%92%AD%E6%97%B6%E9%92%9F&spm=1018.2226.3001.4450????????本文針對Design Compiler,但該命令同樣存在于PrimeTime、IC Compiler等工具中,它們大致相同,略有差別。set_fanout_load命令的BNF范式(有關BNF范式,可以參考以往文章)為:

set_propagated_clockobject_list指定端口列表/集合

????????指定一個列表/集合,包含時鐘對象、端口對象或引腳對象,對于列表而言,如果有多于一個對象,需要使用引號或大括號包圍(對使用集合無效),關于列表和集合的區別,可以參考下面的博客。

SDC命令詳解:使用集合(Collection)而不是字符串(String)/列表(List)作為命令參數![]() https://chenzhang.blog.csdn.net/article/details/147144571

https://chenzhang.blog.csdn.net/article/details/147144571

簡單使用

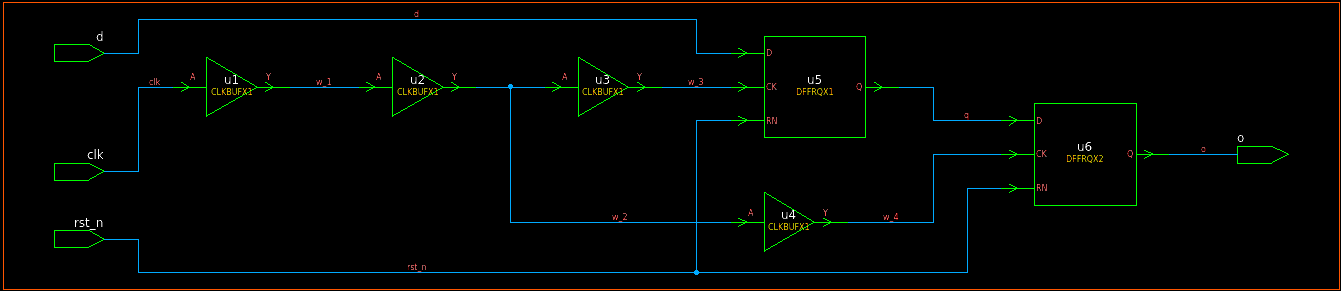

????????下面用一個簡單的例子進行說明,圖1是兩個D觸發器的簡單級聯,可以看出此時的時鐘路徑上人為插入了一些緩沖器。?

圖1 一個簡單的例子

????????下面使用create_clock命令,在clk端口創建了一個理想時鐘,周期為10。

dc_shell> create_clock -period 10 [get_ports clk]????????對于理想時鐘而言,它的延遲包括兩部分:源延遲(source)和網絡延遲(network delay),它們都是使用set_clock_latency命令進行設置的,關于該命令的使用,可以參考之前的文章SDC命令詳解:使用set_clock_latency命令進行約束。?注意:理想時鐘的網絡延遲值是直接設置的,而不會從時鐘路徑上的線延遲(net delay)和單元延遲(cell delay)中推斷出來。

????????下面的命令設置了時鐘clk的源延遲為2ns,網絡延遲為0.5ns。

dc_shell> set_clock_latency -source 2 [get_clocks clk]

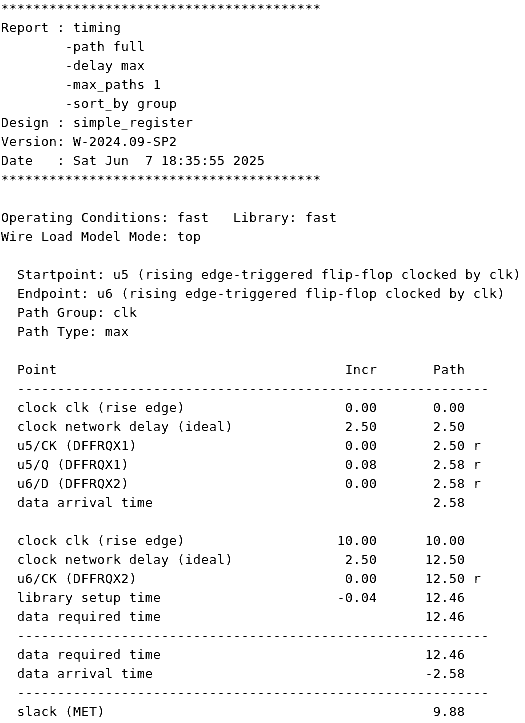

dc_shell> set_clock_latency 0.5 [get_clocks clk]????????圖2所示的建立時間時序報告顯示,時鐘的總延遲為2.5ns(注意這里的network delay其實指的是總延遲,而不只是網絡延遲),括號中的ideal提示了這是一個理想時鐘。

圖2 建立時間時序報告

????????下面使用set_propagated_clock命令將理想時鐘clk轉換成傳播時鐘,此時會給出警告。

dc_shell> set_propagated_clock [get_clocks clk]

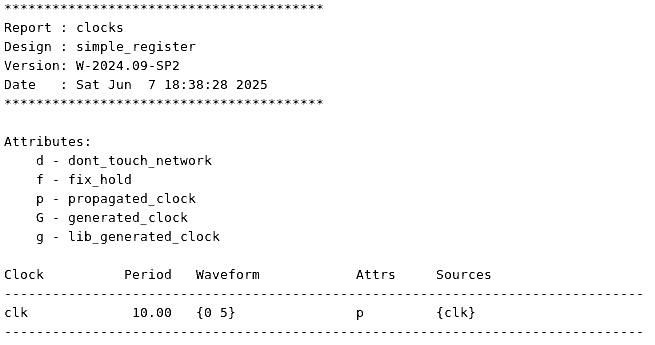

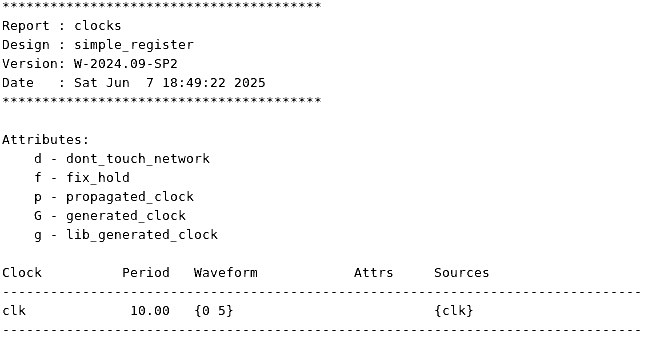

Warning: Converting ideal clock at 'clk' to propagated clock. (UID-477)????????圖3是此時的時鐘報告,可以看出此時的時鐘clk已經擁有propagated_clock屬性了,即是一個傳播時鐘了。?

圖3?時鐘報告(傳播時鐘)

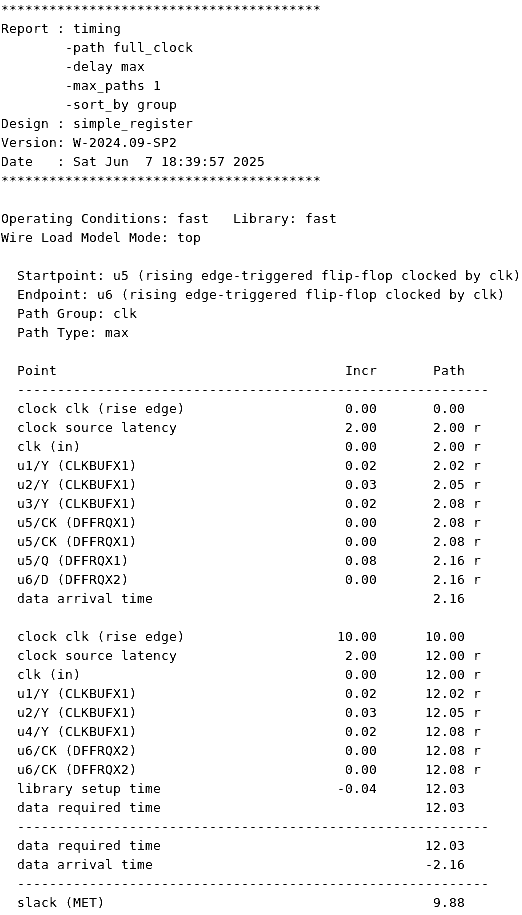

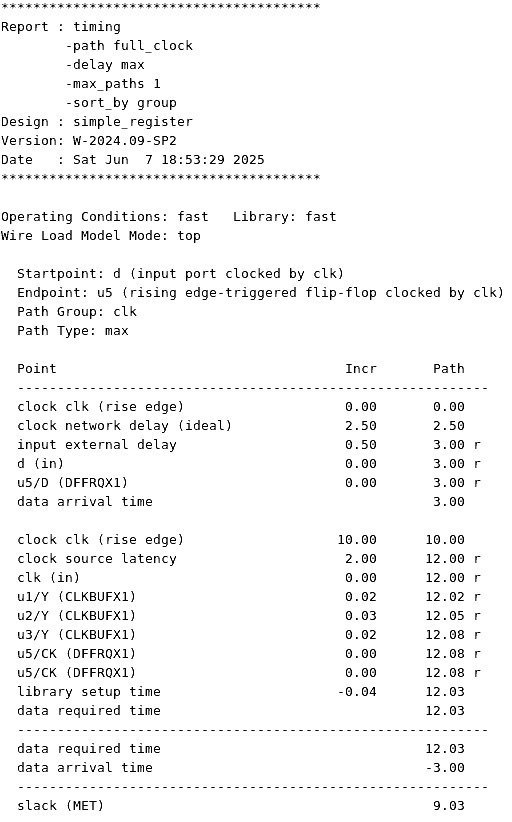

????????此時的時鐘延遲由源延遲和真實網絡延遲組成,這里的網絡延遲是根據時鐘路徑上的線延遲和單元延遲真實計算出來的,如圖4所示(此時添加了-path full_clock選項以顯示出完整的時鐘路徑)。

圖4?展開時鐘路徑的建立時間報告

注意事項

? ? ? ? 有些時候,會設置端口對象或引腳對象的傳播時鐘屬性,此時經過這些端口對象或引腳對象的時鐘對象將被視為傳播時鐘(注意,該時鐘本身可以是理想時鐘)。

? ? ? ? 下面依舊以圖1為例說明這種情況,使用set_propagated_clock命令設置輸入端口clk的傳播時鐘屬性。

?dc_shell> set_propagated_clock [get_clocks clk]? ? ? ? 此時時鐘對象依舊是理想時鐘,如圖5所示。

圖5?時鐘報告(理想時鐘)

? ? ? ? 下面使用set_input_delay命令設置輸入端口d的輸入延遲。

dc_shell> set_input_delay 0.5 -clock [get_clocks clk] [get_ports d]? ? ? ? 此時經過輸入端口d的建立時間時序報告如圖6所示(此時添加了-path full_clock選項以顯示出完整的時鐘路徑)。

圖6?展開時鐘路徑的建立時間報告

? ? ? ? 可以看出,即使是同一個時鐘對象clk,對于發射路徑其被視為理想時鐘(使用設置網絡延遲),?對于捕獲路徑其被視為傳播時鐘(使用真實網絡延遲)。

? ? ? ? 如果將時鐘本身設置為傳播時鐘,發射路徑將只包含源延遲,而不含網絡延遲(在不使用-reference_pin選項的情況下)。

)

)

. 強制類型轉換)