一、高速收發器

1.FPGA高速收發器:GTP,GTX,GTH,GTZ

2.每個Quad有4對高速收發器GT(4個TX和4個RX)和一個COmmon

3.走差分,提高抗干擾性

4.CPLL是每個lane私有的,QPLL是整個Quad的所有通道共享的

5.每個MGT的bank有兩對差分參考時鐘

6.CPLL的時鐘只能給其對應的Lane,這個時鐘是和其他Lane是物理割裂的,所以

不能給其他Lane使用

7.8b10b編碼目的保證直流平衡

二、aurora ip core

1.frame模式是帶有keep和last信號,非frame模式不帶keep和last信號

三、GT收發器認識

1.速率可以達到Gbps,屬于硬核資源,嵌入到Xilinx的FPGA中

2.在低速場合使用IO,GPIO進行通信

低速:IIC,SPI,UART,電平標準為CMOS或者TTL,在傳輸的時候不需要進行編碼。

高速:不同于同步通信和異步通信;使用時鐘嵌入技術,CDR時鐘恢復技術,來進行

恢復時鐘。

pcb需要嚴格等長

時鐘和數據的相位,建立時間和保持時間,信道偏斜

LVDS比CMOS抗干擾更強些

SDR單邊沿采樣;DDR雙邊沿采樣

3.技術發展,先從串行通信---并行通信----后面又轉到高速串行通信,是因為

解決了時鐘問題,將時鐘嵌入到數據中后,才又回到串行通信了;

4.通過8b10b編碼,將數據中直流平衡掉了,就是直流均衡;

四、GT收發器ug476文檔

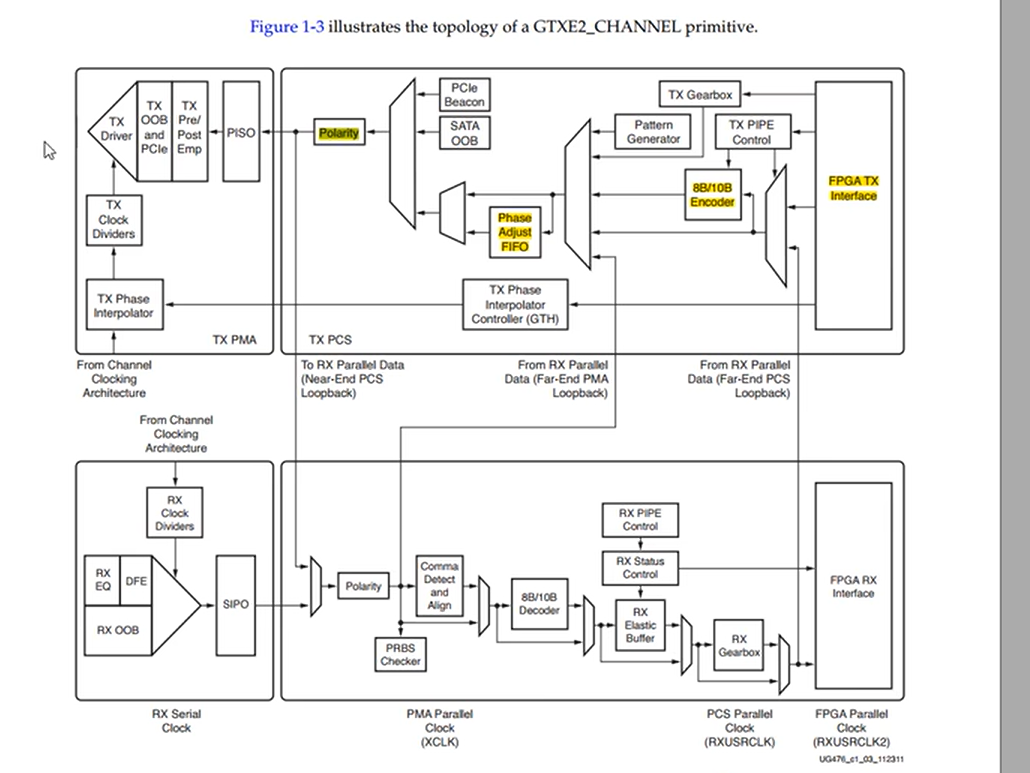

1.GT收發器內部結構

PMA+PCS

PMA是物理層中的模擬部分

PCS是物理層中的數字部分

PISO是GT中比較關鍵的部分,也就是serdes,進行串行和并行的轉換

加重:讓數據跳變更加明顯

DFE均衡器:將數據線上的數據去除加重和干擾,讓數據更加平穩一些

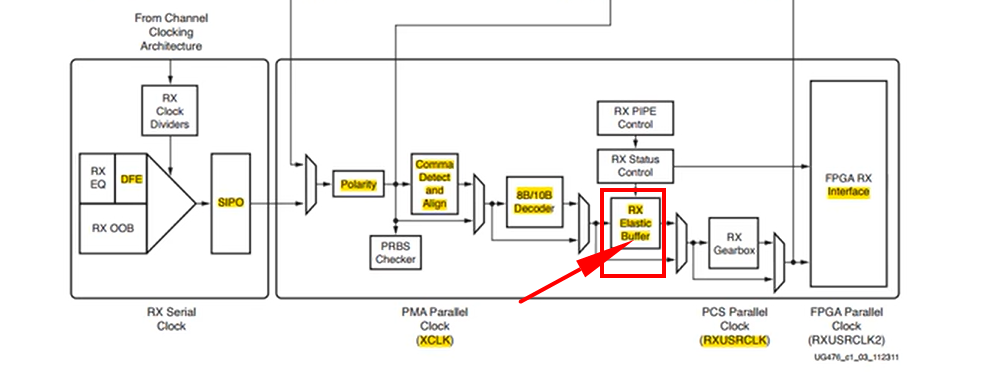

彈性緩沖器用于解決異步時鐘的問題。

)

)

)

:自動注解實現自動化緩存操作)