第二章 ARM處理器及系統結構

2.1 ARM處理器簡介

- 采用RISC架構的ARM微處理器的特點:

- 體積小、功耗低、低成本、高性能;

- 支持 Thumb(16位)/ARM(32位)雙指令集,能很好地兼容 8位/16位 器件;

- Thumb為壓縮指令集

- 大量使用寄存器,指令執行速度更快;-----通用寄存器更多

- 大多數數據操作都在寄存器中完成;

- 尋址方式靈活簡單,執行效率高;

- 指令長度固定

- 絕大多數指令單周期,少量不是

- 常見的ARM處理器的類別:

- ARM7系列

- ARM9系列

- ARM9E系列

- ARM10E系列

- ARM11系列

- SecurCore微處理器系列

- Coretex

2.2 ARM微處理器系列

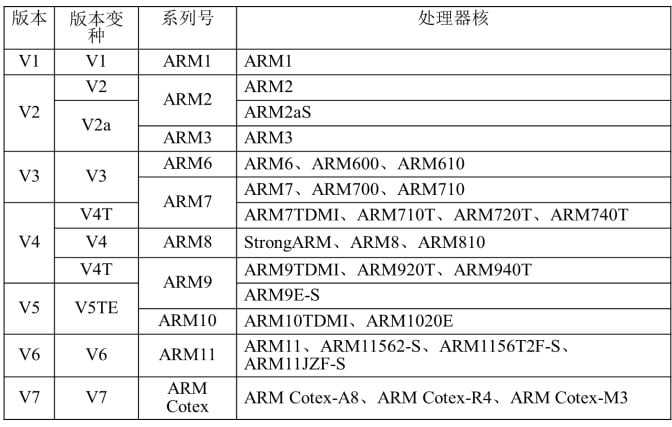

2.2.1 ARM指令集體系結構的演變

- 了解即可

- ARM處理器和指令集構架版本的對應關系

-

ARM/Thumb的命名規范

-

以ARMv開頭

-

ARM指令集的版本號(1-8)

-

可變功能標識

-

T—表示支持Thumb指令,

-

M—表示支持乘法指令,

-

E — 增強型DSP指令,

-

J — Java加速器Jazelle,

-

SIMD — ARM媒體功能擴展,

-

但是ARMv4和其上的版本缺省都支持M功能,因此ARMv4和其上的版本的標識中可以不用標識M.

-

-

如果3中描述的功能不存在,則在該功能標識符前加x 。

- 例如,ARMv5TxM 表示 ARM 指令集版本為 5,支持 T 變種,不支持 M 變種。

-

-

ARM處理器命名

- 規則:ARM{x}{y}{z}{T}{D}{M}{I}{E}{J}{F}{-S}

- x – 處理器系列

- y – 存儲管理/保護單元

- z – cache

- T – 支持Thumb指令集

- D – 支持片上調試

- M – 支持快速乘法器

- I – 支持Embedded ICE,支持嵌入式跟蹤調試

- E – 支持增強型DSP指令

- J – 支持Jazelle

- F – 具備向量浮點單元VFP

- -S – 可綜合版本

- 規則:ARM{x}{y}{z}{T}{D}{M}{I}{E}{J}{F}{-S}

-

ARM處理器指令集的特點

- ARM內核不是一個純粹的RISC體系結構,ARM指令集與純粹的RISC的定義有以下幾個不同。

- 一些特定指令的周期數可變,并不是每條ARM指令都是單周期的。

- 內嵌的桶形移位器產生了更為復雜的指令,擴展了指令的功能,因此改善了內核的性能。

- 支持16位的Thumb指令集,提高了代碼密度。

- 支持條件執行:每條指令都可以設置一個執行條件,只有條件滿足時才執行。

- 增強指令:一些功能強大的數字信號處理指令被加入到ARM指令集中。

- ARM內核不是一個純粹的RISC體系結構,ARM指令集與純粹的RISC的定義有以下幾個不同。

2.2.2 ARM體系結構的演變

-

ARM7

-

ARM9

- 存儲器:哈佛體系結構----區分了數據總線和指令總線

- 5級流水線:取指、譯碼、執行、緩沖/數據、回寫

-

ARM10E

- 6級流水線

-

ARM11

- 包含64個4種狀態的跳轉目標地址緩存

- 有產品用多核處理器

-

Cortex

-

SecurCore 微處理器系列

2.3 ARM9處理器內核

2.3.1 ARM9系列MCU

一、ARM9TDMI

- 后綴意義

- T:支持16位Thumb指令集;

- D:支持片上Debug;

- M:內嵌硬件乘法器;

- I:嵌入式ICE,支持片上斷點和調試點

- ARM9TDMI使用哈佛結構,通過cache可以同時讀取指令和數據。

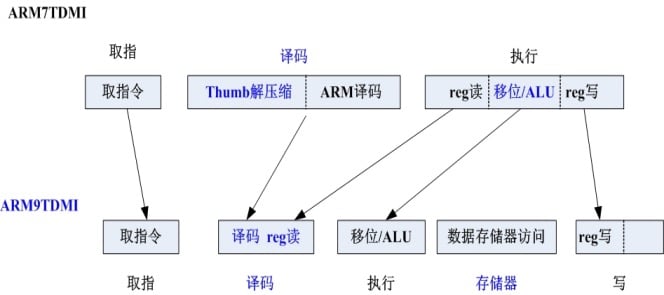

- 流水線從ARM7TDMI的 3級 增加到 5級。

- 在相同工藝下,ARM9TDMI的性能近似為ARM7TDMI的2倍。

2.3.2 ARM9TDMI的流水線

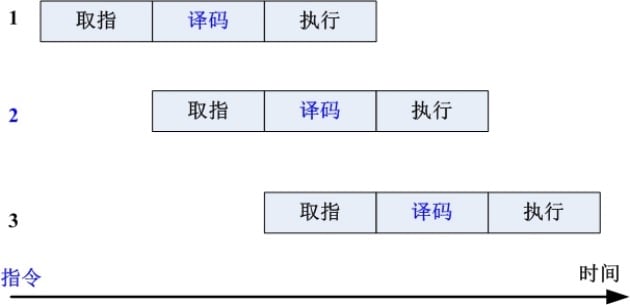

一、ARM7 的 3 級流水線

二、ARM9 的 5 級流水線

- 5級流水線 是 ARM9TDMI 的主要特征之一,其設計減少了在每個時鐘內必須完成的最大工作量,進而允許使用較高的時鐘頻率。

- 取指:指令從存儲器中取出,放入指令流水線;

- 譯碼:指令譯碼,從寄存器堆中讀取寄存器操作數;

- 執行:把一個操作數移位,產生ALU的結果。

- 如果指令是Load或Store,在ALU中計算存儲器的地址;

- 緩存/數據:如果需要,則訪問數據存儲器;

- 否則,ALU的結果只是簡單地緩沖一個時鐘周期,以便使所有指令具有同樣的流水線流程;

- 回寫:將指令產生的結果寫回到寄存器堆,包括任何從寄存器讀出的數據

? ARM9TDMI與ARM7TDMI流水線比較

2.3.3 協處理器接口

- 定義:

- 協處理器用于減輕系統微處理器的特定處理任務的芯片或模塊

- ARM處理器內置的協處理器通過擴展指令集或提供配置寄存器來擴展內核處理功能。

- 擴展指令集:

- 協處理器也能通過提供一組專門的新指令來擴展指令集。

- 例如,有一組專門的指令可以添加到標準ARM指令集中,以處理向量浮點(VFP)運算。

- 這些新指令是在ARM流水線的譯碼階段被處理的。

- 協處理器和ARM處理器連接到同一個指令總線,這意味著協處理器可以對指令流中的指令進行譯碼并執行其所支持的指令

- 如果在譯碼階段發現是一條協處理器指令,則把它交給相應的協處理器

- 如果該協處理器不存在,或不認識這條指令,則ARM認為發生了未定義指令異常,則執行未定義指令陷阱(即未定義指令異常服務子程序)

- 協處理器也能通過提供一組專門的新指令來擴展指令集。

- 擴展指令集:

- 可用的協處理器:

- 一個系統中最多可連接16個協處理器。每個協處理器都由唯一的ID標識

- ARM920T處理中包含兩個內部協處理器

- CP14通信通道協處理器,負責調試

- CP15為CACHE和MMU功能提供的系統控制協處理器

- ARM920T處理中包含兩個內部協處理器

- 一個系統中最多可連接16個協處理器。每個協處理器都由唯一的ID標識

2.4 ARM處理器工作狀態

2.4.1 指令集分類

-

ARM指令集和Thumb指令集

-

設計目的:為了讓用戶更好地控制代碼量

-

ARM指令集:

- 32位**(字)**長度,具有最完整的功能

-

Thumb指令集:

- 16位**(半字)**長度,能實現ARM指令集的大部分功能

-

在功能上可以認為Thumb是ARM指令集的子集

-

2.4.2 工作狀態切換

ARM9TDMI核是具有T變種的ARM處理器核,其工作狀態一般有以下兩種,并可在兩種狀態之間切換。

-

ARM狀態:

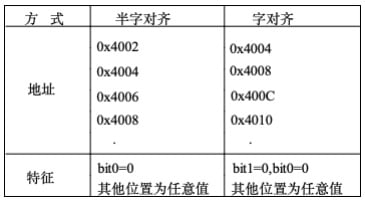

- 執行32位的字對齊的ARM指令

- 系統上電默認的狀態

-

Thumb狀態:

- 執行16位的半字對齊的Thumb指令

-

狀態切換:

- ARM處理器的兩種狀態可以通過相應的指令進行切換。

- ARM指令集與Thumb指令集不能同時混合使用。

- ARM和Thumb狀態間的切換并不影響處理器模式或寄存器內容

- 從一個ARM例程調用另一個Thumb例程時,內核必須切換狀態,反之亦然

- 用BX分支指令來執行狀態切換

-

指令長度和數據格式

-

ARM微處理器的指令長度可以是32位(在ARM狀態下),也可以為16位(在Thumb狀態下)

-

ARM微處理器中支持字節(8位)、半字(16位)、**字(32位)**三種數據類型

-

字對齊 & 半字對齊

- 數據以字存儲–字對齊

- 數據以半字存儲–半字對齊

- 在內存的地址

-

2.5 ARM處理器的運行/工作模式

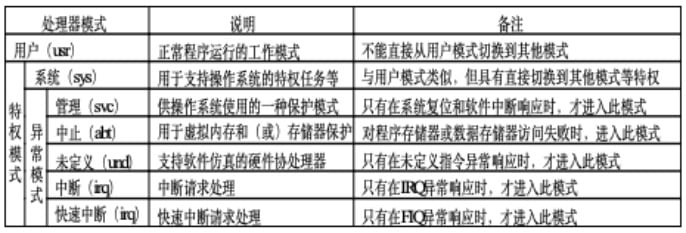

- ARM體系結構支持7種運行模式

2.5.1 用戶模式(USR)

-

正常程序執行模式,大部分任務執行在這種模式下。

-

用戶模式是用戶程序的工作模式,該模式權限最低

-

該模式操作的硬件資源是有限的

-

該模式沒有權限去操作其它硬件資源,也不能切換到其它模式下

- 若想這樣做只能通過軟中斷的方式

-

該模式只能處理自己的數據

2.5.2 系統模式(SYS)

-

系統模式是特權模式,不受用戶模式的限制

-

用戶模式和系統模式共用一套寄存器

-

系統模式比用戶模式有更高的權限,可以訪問所有系統資源及進行模式切換

-

OS的一些特權任務,可以使用這個模式訪問一些受控的資源

-

注意:

- 用戶模式與系統模式兩者使用相同的寄存器,都沒有SPSR

2.5.3 一般中斷模式(IRQ)

- 一般中斷模式也叫通用中斷模式

- 用于處理一般的中斷請求,通常在硬件產生中斷信號之后自動進入該模式

- 該模式為特權模式,可以自由訪問系統硬件資源

2.5.4 快速中斷模式(FIQ)

-

快速中斷模式是相對一般中斷模式而言的

-

它是用來處理對時間要求比較緊急的中斷請求

- 主要用于高速數據傳輸及通道處理

-

其中斷優先級相對普通中斷更高。

2.5.5 管理模式(SVC)

- 管理模式是CPU上電后默認模式

- 因此在該模式下主要用來做系統的初始化,軟中斷處理也在該模式下。

- 系統復位或開機、軟中斷時進入到SVC模式下。

- 用戶模式下的用戶程序請求使用硬件資源時,通過軟中斷進入該模式

2.5.6 中止模式(ABT)

- 中止模式用于支持虛擬內存或存儲器保護

- 當用戶程序訪問非法地址或沒有權限讀取的內存地址時,會進入該模式。

- 訪問非法地址— 在取指就出現問題

- 訪問沒有權限讀取的內存地址— 在訪問數據才出現問題

2.5.7 未定義模式(UND)

- CPU在指令的譯碼階段不能識別該指令操作時,會進入未定義模式,進行未定義陷阱處理。

- 該模式用于支持硬件協處理的軟件仿真

2.5.8 特權模式&異常模式

-

特權模式:

-

除用戶模式外的其它6種處理器模式稱為特權模式(Privileged Modes)。

-

在特權模式下,程序可以訪問所有的系統資源,也可以任意的進行處理器模式切換。

-

只有在特權模式下才允許對當前程序狀態寄存器(CPSR)的所有控制位直接進行讀/寫訪問,而在非特權模式下只允許對CPSR的控制位進行間接訪問(SWI方式)。

-

-

異常模式:

- 特權模式中除系統模式之外的其他5種模式又統稱為異常模式。

- 它們除了可以通過在特權下的程序切換進入外,也可以由特定的異常進入。

- 其中管理模式也稱為超級用戶模式,是為操作系統提供軟中斷的特有模式。

-

大多數的用戶程序運行在用戶模式下。當處理器工作在用戶模式時,需要進行處理器模式切換時,應用程序可以產生異常處理,在異常處理過程中進行處理器模式切換。這種體系結構可以使操作系統控制整個系統資源的使用

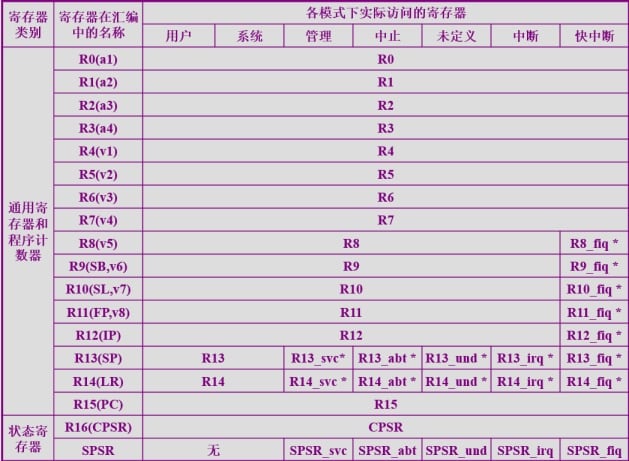

2.6 ARM寄存器

- ARM處理器有37個用戶可見的寄存器

- 31 個通用寄存器:

- R0~R15

- R13_svc、R14_svc 、 R13_abt、R14_abt 、R13_und、R14_und、R13_irq、 R14_irq

- R8_fiq~R14_fiq

- 6 個狀態寄存器:

- 1 個CPSR

- 5 個SPSR( SPSR_svr、 SPSR_abt 、 SPSR_und 、 SPSR_irq 、 SPSR_frq )

- 31 個通用寄存器:

2.6.1 ARM狀態下的寄存器

一、各模式可訪問的寄存器

- 在ARM狀態下,任一時刻都可以訪問到 16個 通用寄存器和1~2個狀態寄存器。各種模式下能訪問的寄存器如下圖所示:

- 在匯編中,R0-R13為保存數據或地址值的通用寄存器。它們是完全通用的寄存器,不會被體系結構作為特殊用途,并且可用于任何使用通用寄存器的指令。

二、一般通用寄存器

-

通用寄存器根據其分組與否可分為以下兩類:

-

未分組寄存器,包括 R0~R7

-

分組寄存器,包括 R8~R14。

-

-

未分組寄存器:

- 在所有處理器模式下對于每一個未分組寄存器來說,指的都是同一個物理寄存器

- 即對于任何處理器模式,這些寄存器都對應于相同的32位物理寄存器

-

分組寄存器:

- 它們每一個訪問的物理寄存器取決于當前的處理器模式

- 幾乎所有允許使用通用寄存器的指令都允許使用分組寄存器

- 寄存器R8-R12有兩個分組的物理寄存器

- 一個用于除FIQ模式之外的所有寄存器模式

- 另一個用于FIQ模式,這樣可在發生FIQ中斷后,加速處理速度

- 寄存器R13-R14分別有6個分組的物理寄存器

- 一個用于用戶和系統模式

- 其余5個分別用于5種異常模式

- 如果改變處理器的模式,新模式的分組寄存器將取代原來模式的分組寄存器組

- 例如,當處理器處于中斷模式時,執行的指令可訪問的名字仍然是R13和R14寄存器,但實際上是訪問分組寄存器R13_irq和R14_irq,而用戶模式下的R13_usr和R14_usr不會受到任何影響,程序仍然可以正常訪問R0 ~ R12寄存器

三、 堆棧指針R13

- 寄存器R13通常用作堆棧指針,稱作SP。

- 每種異常模式都有自己的分組R13。通常R13應當被初始化成指向給異常模式所分配的堆棧

- 用戶模式和系統模式共用一個R13寄存器

- 每種異常模式都有專用的R13寄存器。

- 它們通常指向各模式所對應的專用堆棧,也就是說ARM處理器允許用戶程序有6個不同的堆棧空間

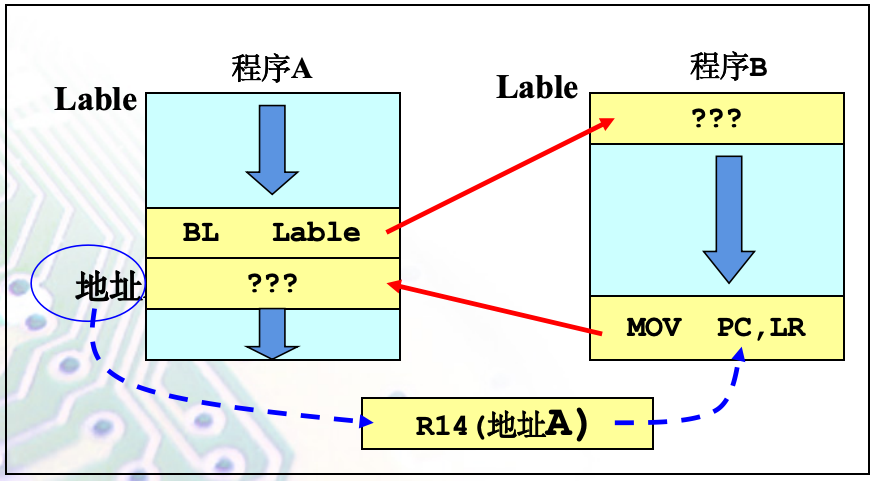

四、鏈接寄存器R14

寄存器R14(鏈接寄存器或LR)在體系結構中有兩種特殊用途:

- 在各種模式下,R14用來保存子程序的返回地址。當一條BL或者BLX指令執行子程序調用時,R14設為子程序的返回地址

-

返回時,通過復制R14中的地址值到PC中來實現子程序的返回。通常有以下2種方式:

-

執行下列指令之一

①MOV PC, LR ;把LR中的值寫入到PC寄存器中

②BX LR ;跳轉(帶狀態切換)到LR地址所指向的指令執行。用于從實現從一個狀態返回另外一個狀態并繼續執行。

-

在子程序入口,執行R14的入棧操作:

- STMFD SP!, { , LR} ;該條指令用于把和LR(R14)等多個寄存器壓入堆棧,SP(R13)指向堆棧頂部。

并使用匹配的指令返回:

- LDMFD SP!, {, PC} ;該條指令用于把堆棧頂部多個單元,執行出棧操作,出棧的數據保存到和PC等多個寄存器中。注:執行該操作后,原R14入棧的值,出棧后就保存到PC中了,相當于執行了把R14的值寫入到PC的操作。

-

- 當發生異常時,相關異常模式下的R14就設為異常返回地址。異常的返回地址與子程序的返回類似。區別在于有些異常有一個小常量的偏移。

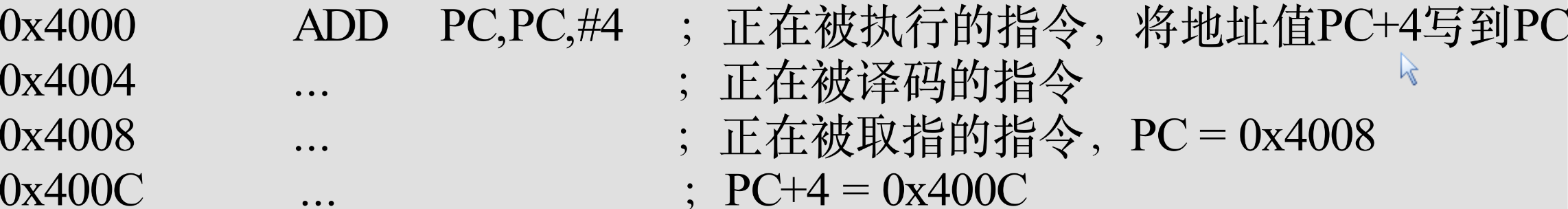

五、程序計數器R15

-

寄存器R15用作程序計數器(PC)

-

在ARM狀態,位[1:0]為0,位[31:2]保存PC

-

在Thumb狀態,位[0]為0,位[31:1]保存PC

-

-

無論處理器處于何種狀態,程序計數器R15(即PC)總是指向“正在取指”的指令,而不是指向“正在執行”的指令或正在“譯碼”的指令。

- 一般來說,人們習慣性約定將“正在執行的指令作為參考點”,稱之為當前第1條指令。

- 因此,PC總是指向第3條指令,或者說PC總是指向當前正在執行的指令地址再加2條指令的地址。–在三級流水線的情況下

- ARM狀態下:PC=當前程序執行位置+8字節

- Thumb狀態下:PC值=當前程序執行位置+4字節

-

寫程序寄存器

- 寫R15的通常結果是將寫到R15中的值作為指令地址,并以此地址發生轉移。由于ARM指令要求字對齊,通常希望寫到R15中值的位[1:0]=0b00(b指的是二進制)

2.6.2 ARM狀態下程序狀態寄存器CPSR

- 當前程序狀態寄存器(CPSR)可以在任何處理器模式下被訪問,它包含下列內容:

? (1)ALU 狀態標志(條件碼標志位);

? (2)當前的處理器模式;

? (3)中斷使能標志;

? (4)設置處理器的狀態。

- 每一種異常模式下,都有一個專用的物理寄存器做備份程序狀態寄存器(SPSR: Saved Program Status Register )。

- 當特定的異常中斷發生時,這個物理寄存器負責存放當前程序狀態寄存器的內容。當異常處理程序返回時,再將其內容恢復到當前程序狀態寄存器。

一、條件標志位

- 這些條件標志位會根據程序中的算數指令或邏輯指令的執行結果進行改變,而且這些條件標志位可由大多數指令檢測以決定指令是否執行。

- N:

- 本位設置成當前指令執行結果的第31位。當兩個由補碼表示的有符號整數運算時,N=1 表示結果為負數;否則結果為正數或零。

- Z:

- Z=1 表示運算的結果為零,否則結果不為零。

- C:

- 分 4 種情況設置 C 的方法:

- 在加法指令中(包括比較指令CMN),當結果產生了進位,則C=1,表示無符號數運算發生上溢出,其它情況下C=0;

- 在減法指令中(包括比較指令CMP),當運算中發生了借位,則C=0,其它情況下C=1;

- 對于在操作數中包含移位操作的運算指令(非加/減指令),C被設置成被移位寄存器最后移出去的位;

- 對于其它非加/減法運算指令,C的值通常不受影響。

- 分 4 種情況設置 C 的方法:

- V:

- 下面分兩種情況討論V的設置方法:

- 對于加/減運算指令,當操作數和運算結果都是以二進制的補碼表示的帶符號的數時,且運算結果超出了有符號運算的范圍時溢出。V=1 表示符號位溢出;

- 對于非加/減法指令,通常不改變標志位 V 的值。

- 下面分兩種情況討論V的設置方法:

- N:

二、Q標志位

-

了解即可

-

在帶DSP指令擴展的ARMV5及更高版本中,Q標志位被指定用于指示增強DSP指令是否發生了溢出。 在ARMV5以前的版本及ARMV5的非E系列處理器中,Q標志位沒有被定義,屬于待擴展的位。

三、控制位

-

CPSR的低8位屬于控制位。

(1)中斷禁止位(第7、6位)

? I=1:IRQ被禁止;F=1:FIQ被禁止。

(2)狀態控制位(第5位)

? T 位是處理器的狀態控制位。

? T=0:處理器處于ARM狀態;

? T=1:處理器處于Thumb狀態。

- 注意:絕對不要強制改變CPSR寄存器中的控制位T,否則處理器會進入未知狀態

(3)模式控制位

- 決定處理器的工作模式

- 如果將非法值寫入M[4:0]中,處理器將進入無法恢復的模式

-

注意

- 通過程序修改CPSR可以進入異常。除此之外,也可以在內核對異常或者中斷響應時由硬件切換到異常模式。

- 用戶模式與系統模式不能由異常進入,也就是說要想進入系統模式,必須通過修改CPSR才能實現。

2.7 ARM存儲系統

2.7.1 ARM存儲方法

-

ARM處理器外部采用馮·諾依曼結構,指令和數據共用一條32位數據總線,只有裝載、存儲和交換指令可訪問存儲器中的數據。

-

ARM處理器將存儲器看作是一個從0開始的線性遞增的字節集合,其中每個數組元素(字節)都是可以尋址的

-

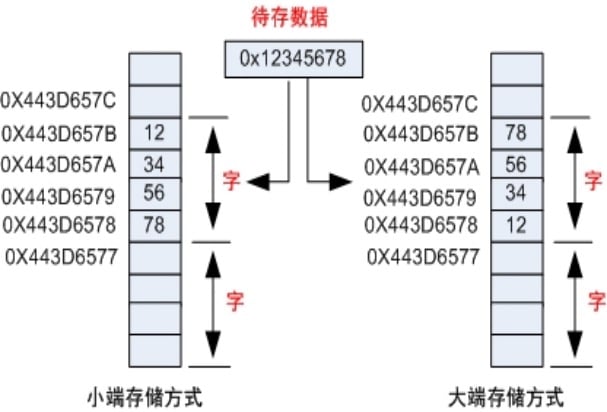

ARM支持**大端模式(big-endian)和小端模式(little-endian)**兩種內存模式

- 大端模式下,一個字的高地址單元放的是數據的低位;

- 小端模式下,數據的低位放在內存中低地址單元中。

- 一個基于ARM的實際芯片可能只支持小端存儲器格式,也可能只支持大端存儲器格式,還可能兩者都支持

- ARM指令集不包含任何直接選擇大小端存儲器格式的指令,但是一個同時支持大小端存儲器格式基于ARM的芯片可以通過硬件配置(一般使用芯片的引腳來配置)來匹配存儲器系統所使用的規則。如果芯片有一個標準系統控制的協處理器(例如ARM920T的CP15協處理器),系統控制協處理器寄存器1的bit7可用于改變配置。

- 注意:對于S3C2440是通過軟件來指定存儲器格式的(通過設置CP15協處理器協處理器寄存器1的bit7來實現),缺省為小端格式。

2.7.2 ARM體系的存儲結構

- ARM9使用 232?個8位字節地址空間,字節地址的排列從0~232-1。

- 地址空間也可以看作是包含 230 個32位字

- 地址以字為單位進行分配,也就是將地址除以4。

- 地址為A的字包含4個字節,地址分別為A、A+1、A+2和A+3。

- 地址空間還可被看作包含 231 個16位半字

- 地址按照半字進行分配。

- 地址為A的半字包含2個字節,地址分別為A和A+1

2.7.3 存儲器結構

- ARM處理器有的帶有指令cache和數據cache,但不帶有片內RAM和片內ROM。

- 系統所需的RAM和ROM(包括Flash)都通過總線外接。

- 有的ARM片內還帶有存儲器管理單元MMU(Memory Management Unit)

2.7.4 存儲器映射I/O

- ARM才用統一編址,每一個外設都分配一個地址

2.7.5 Flash組織形式

-

目前幾乎所有MCU的程序都存儲在Flash中。Flash分為片內和片外兩種。

-

片內Flash:雖然ARM處理器通常不帶有片內Flash,但有些特定的ARM微控制器(MCU)可能集成了片內Flash。這種片內Flash通常用于存儲固件和程序代碼,由于它直接集成在芯片內部,訪問速度較快,且功耗較低。

-

片外Flash:

-

**NOR Flash **

- NOR Flash讀取速度快,但是擦除和寫入速度慢。

-

NAND Flash

- NAND Flash讀取速度比NOR Flash慢,但擦除和寫入速度很快。

-

2.7.6 RAM的組織方式

- RAM的種類

- 芯片自帶的RAM不夠用時需要外加,外加的RAM一般是SDRAM和DDR RAM,極少數使用SRAM,因為SRAM的價格相對較貴,但SRAM速度要比動態RAM快。

- RAM的使用

- SRAM:只需要在IDE中設置好地址。

- SDRAM/DDR RAM:不僅要在IDE中設置好起始地址,還要在程序中做初始化操作后才能使用。如果使用仿真器,那么在仿真運行程序前,要執行一個初始化腳本文件,或者執行一系列命令對SDRAM和DDR RAM進行初始化,否則會運行出錯。

2.8 中斷和異常的基本概念

這個部分不考

- 中斷

- 是主機與外設進行數據通信的重要機制,它負責處理處理器外部的事件

- 異常

- 實質上也是一種中斷,只不過它主要負責處理處理器內部事件

- 計算機通常是用中斷來處理外中斷和內部異常,因此在ARM技術中,將二者統稱為異常。

2.8.1 中斷和異常

-

什么叫中斷

- 當處理器遇有外部設備發生 “緊急事件” 需要它來處理時,它就必須停下 “手頭上的工作” 先去處理這個 “緊急事件”。處理器的這種工作過程,或者這種工作狀態就叫做中斷。

-

什么叫中斷請求

- 當外部設備有緊急事件需要處理器進行處理時,外部設備必須向處理器發送一個 電信號(脈沖或電平) 來表示有事件需要處理器來處理。這個信號叫做 中斷請求信號 ,或稱 中斷請求。

-

什么叫中斷源

- 發出中斷請求信號的外部設備或事件就叫做中斷源。

-

什么叫異常

- 由內部事件引起的中斷叫做異常。

2.8.2 中斷請求信號屏蔽

-

可屏蔽中斷

- 人們把帶有開關,能阻止中斷請求的中斷輸入端叫做可屏蔽中斷信號輸入端。這類中斷叫可屏蔽中斷。

-

非屏蔽中斷

- 人們把不帶開關,不能阻止中斷請求的中斷輸入端叫做非屏蔽中斷信號輸入端。這類中斷叫非屏蔽中斷。

- 為了對處理器可以接收中斷源的數目進行擴充及對中斷進行必要的管理,在中斷源和處理器之間還配有中斷控制器

2.8.3 中斷優先級及中斷嵌套

- 中斷優先級

- 處理器通常只有一個可屏蔽中斷請求輸入端。對于具有 多個中斷源的系統來說,當有兩個或兩個以上中斷源同時發生中斷請求時就會出現所謂的競爭。

- 競爭可以通過優先級的方法來處理,具體實現方法有兩種:硬件實現方法和軟件實現方法。

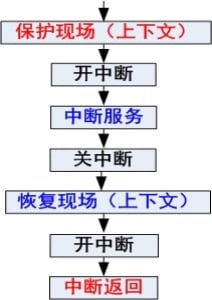

2.8.4 中斷服務程序

- 用來處理中斷事件的程序叫做中斷服務程序。

- 中斷服務程序與普通子程序的重要差別在于:

- 中斷服務程序要對中斷嵌套進行必要的管理。即中斷服務程序要根據需要,對程序狀態寄存器中的中斷允許標志進行相應的設置。

2.8.5 中斷向量和中斷向量表

- 為了與普通子程序的首地址進行區分,中斷服務程序的首地址(入口地址)通常被叫做中斷向量,或中斷矢量。

- 以后還會看到,凡是能直接或間接指向中斷服務程序的都叫中斷向量。

- 在處理器收到中斷請求之后,它們都需要獲得中斷服務程序首地址——中斷向量。

- 所有的中斷向量都按一定規律存放在一個固定的存儲區域,這個集中存放了中斷向量或與中斷向量相關信息的存儲區域就叫做中斷向量表。

2.8.6 中斷的處理過程

- 處理器響應中斷的條件

? 處理器響應中斷的條件主要有以下幾個:

? (1)處理器程序狀態寄存器的中斷屏蔽標志處于非屏蔽狀態;

? (2)沒有更高級的中斷請求正在響應或正在發出、正掛起;

? (3)處理器在現行指令執行結束后。

-

中斷處理的過程

-

當有中斷請求發生且滿足上述條件時,計算機系統就會響應中斷請求,并自動將被中斷程序的下一條指令地址(斷點地址)保存和關閉中斷;接下來便將自中斷向量表查詢得到的與該中斷源對應的中斷向量送入PC,并轉去執行中斷服務程序。

-

當執行到中斷服務程序末尾時,執行中斷返回指令或跳轉指令,把保存的斷點地址送回 PC,以在斷點處繼續執行被中斷的程序。

-

2.9 ARM的中斷(異常)

-

只要正常的程序流程被暫時中止,ARM處理器就進入異常模式。

-

ARM異常與中斷不做嚴格意義上的區別。

-

處理器響應中斷條件

- CPSR的中斷屏蔽標注處于非屏蔽狀態

- 處理器處于現行指令執行結束后的狀態,換一種說法就是一條指令執行中間不能被中斷

- 低優先中斷不能中斷高優先中斷

-

ARM處理器可以響應的中斷(異常)有7種,分別為:

- 中斷

- 快中斷

- 復位中斷

- 軟中斷異常

- 預取指令中止異常

- 數據中止異常

- 未定義指令異常

2.9.1 ARM的中斷(異常)向量表

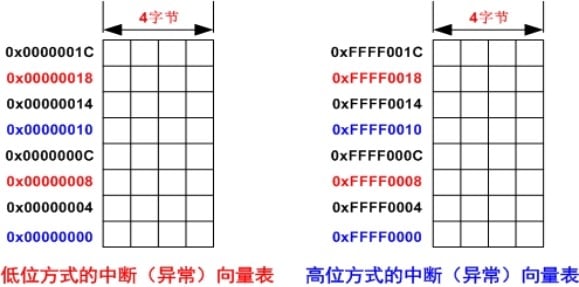

- 低端和高端向量表

- ARM中斷(異常)的各個向量在向量表中的分配如下

-

高端向量是ARM架構可選配置,可以通過硬件外部輸入管腳來配置是低端向量還是高端向量,不能通過指令來改變向量的位置。但可通過協處理器CP15配置

-

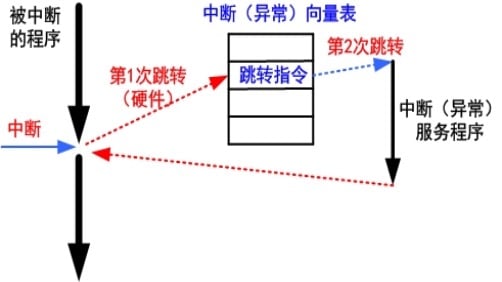

處理器在響應中斷(異常后),可以通過兩次跳轉轉移到中斷(異常)服務程序,示意圖如下

2.9.2 ARM異常響應

一、進入異常

-

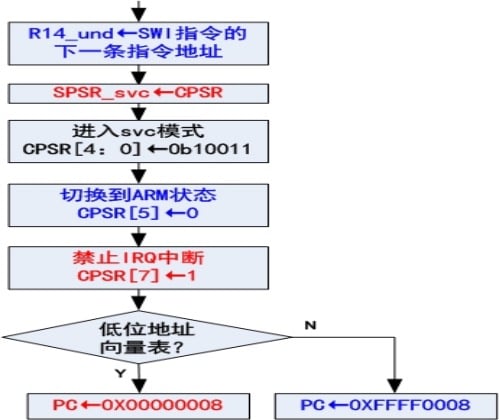

在異常發生后,ARM內核會作以下工作:

- 在適當的LR中保存斷點的地址,當異常入口來自:無論是ARM狀態還是Thumb狀態,ARM都將當前PC寄存器的值(運行指令地址加4或加8 )復制(取決于異常的類型) 到LR中;

- 把當前程序狀態寄存器(CPSR)中的內容保存到模式私有寄存器SPSR中;

- 將寄存器CPSR中的MODE域設置為中斷(異常)應進入的運行模式;

- 對CPSR的I位和F位進行相應的設置,以防止再次響應同一個中斷請求。

- 強制PC從相關的異常向量處取指,即到中斷向量表中獲取中斷向量,轉向用戶所編寫的中斷(異常)服務程序。

- 異常總是在ARM狀態中進行處理。當處理器處于Thumb狀態時發生了異常,在異常向量地址裝入PC時,會自動切換到ARM狀態

二、異常返回

-

當異常結束時,異常處理程序必須做如下處理:

-

將SPSR的值復制回CPSR

-

將LR中的值減去偏移量后存入PC,偏移量根據異常的類型而有所不同。

- 注:恢復CPSR的動作會將T、F和I位自動恢復為異常發生前的值。

-

-

看本章PPT的131和132頁ppt來理解整個過程

三、ARM異常進入/退出

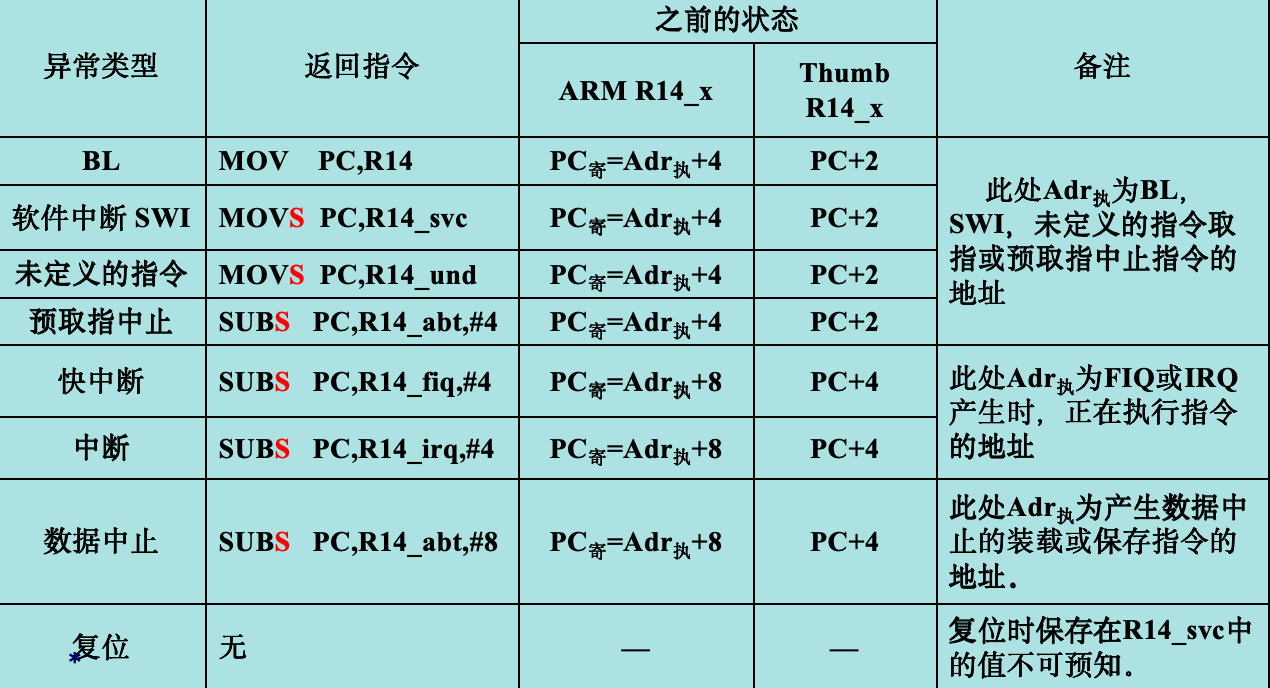

- ARM處理器進入異常時R14所保存的值及退出時推薦指令 :

- 理解并記住在進入異常時,LR存的PC應返回的值

2.9.3 ARM異常描述

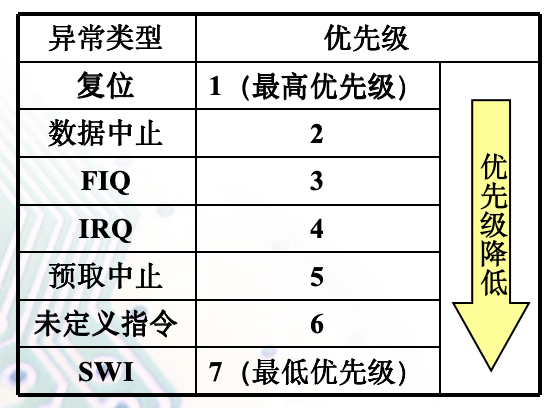

- ARM按事件的緊急程度為每個中斷(異常)都定義了一個固定的優先級別。當多個異常同時發生時,一個固定的優先級系統決定它們被處理的順序:

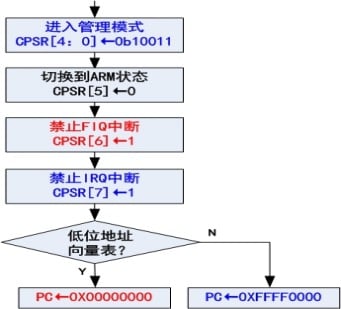

一、復位中斷

-

當nRESET信號被拉低時(一般外部復位引腳電平的變化和芯片其他復位源會改變這個內核信號),ARM處理器放棄正在執行的指令。

-

當nRESET信號再次變為高電平時,ARM處理器執行以下操作:

- 強制M[4 : 0]變為b100011,系統進入管理模式;

- 將CPSR中的控制位I和F置位,IRQ和FIQ中斷禁止;

- 將CPSR中的控制位T清零,處理器處于ARM狀態;

- 強制PC從地址0x00開始對下一條指令進行取指;

- 返回到ARM狀態并恢復執行。

-

在系統復位后,進入管理模式對系統初始化。復位后,

除PC和CPSR之外的所有寄存器的值都是隨機的。

-

復位通常在兩種情況下發生:

-

系統初始運行時的正常上電;

-

由程序引起的復位。

-

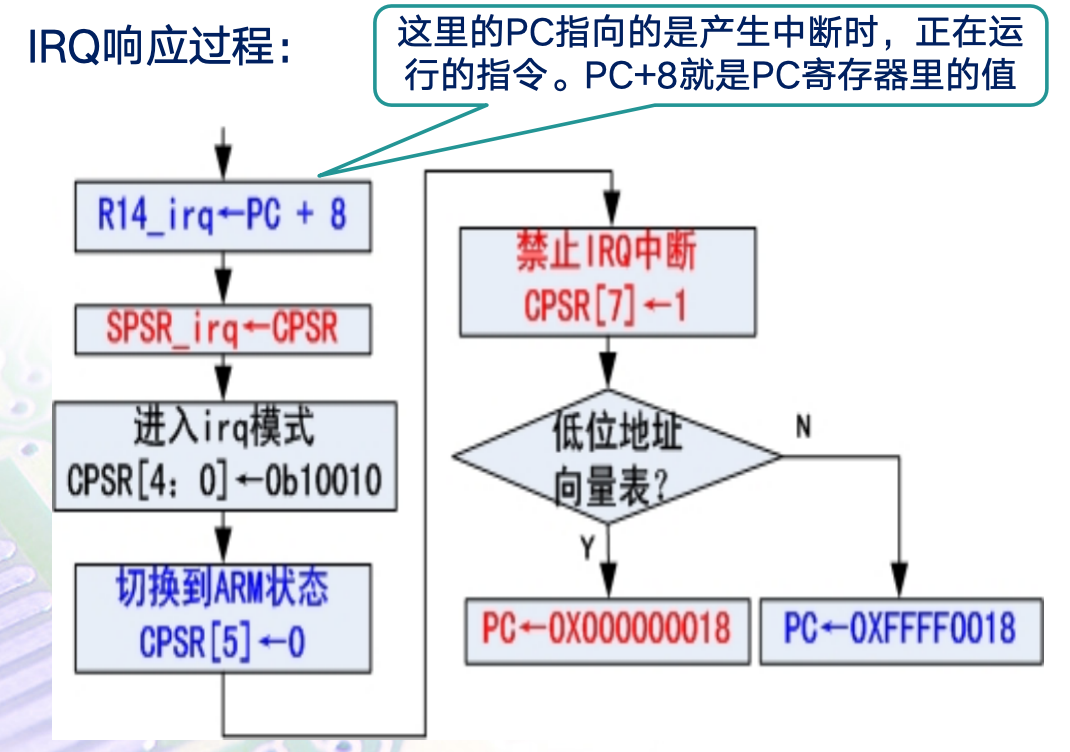

二、中斷請求異常IRQ

-

只有當CPSR中相應的中斷屏蔽被清除時,才可能發生中斷請求(IRQ)異常,IRQ異常是一個由nIRQ輸入端的低電平所產生的正常中斷。

-

當一個IRQ異常中斷發生時,內核切換到中斷模式,表明產生了中斷。

-

內核自動做出如下處理

- 將異常處理程序的返回地址(PC寄存器中的值)保存到異常模式下的R14(R14_irq或者LR)中,即**“中斷返回地址+4”**。

- 用戶模式的CPSR被保存到新的IRQ中斷異常模式SPSR_irq中。

- 修改CPSR。將I位置1,禁止新的IRQ中斷產生,但是不限制FIQ中斷的發生(F位保持原有狀態)。清零T標志位,CPU進入ARM狀態。

- 修改模式位,設置為IRQ模式,此時用戶模式下的R13和R14將不可操作,而IRQ模式下的R13和R14變為可操作,即R13_irq保存IRQ中斷模式的堆棧指針,R14_irq保存了**“IRQ中斷返回地址+4”**。

- 設置IRQ模式下的PC為IRQ異常處理程序的中斷入口向量地址,在IRQ模式下,該向量地址為0x0000 0018。

- 應該是PC+4,上圖有誤

- 返回時,可以通過“SUBS PC,R14,#4”指令返回。

- 實際上在中斷模式下執行的是“SUBS PC,R14,#4”指令,同時在SUB指令尾部有一個S,并且PC是目的寄存器,所以CPSR將自動從SPSR寄存器中恢復。

- 如果用戶需要嵌套IRQ中斷,那么必須在中斷服務程序中重新使能IRQ中斷,并將R14壓入R13所指向的IRQ堆棧之中以預先保留返回地址。程序應當首先通過壓入IRQ堆棧來預先保留ISR(中斷服務子程序)將會使用的R0~R12的值,這時就可以對異常進行處理了。

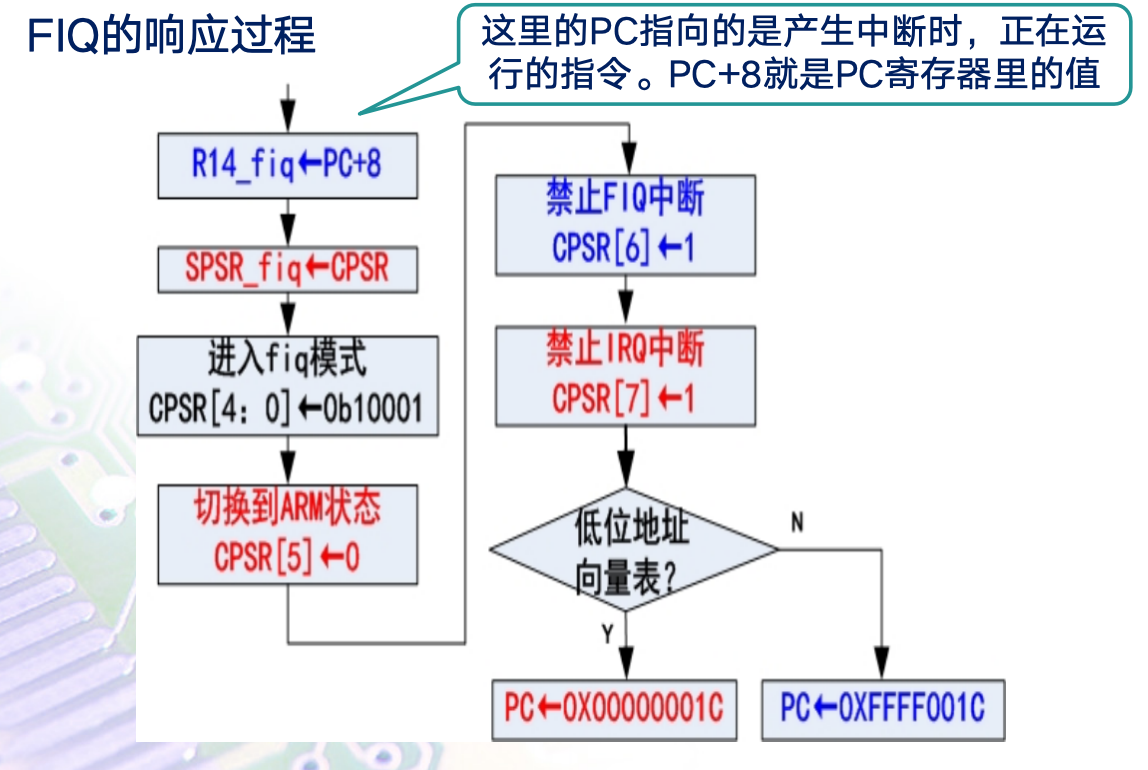

三、快速中斷請求異常FIQ

-

有些嵌入式系統的應用對實時性要求比較高,需要足夠快的中斷響應速度,ARM在IRQ異常之外還設計了一種快速中斷請求(FIQ)異常。

-

為減少延時,ARM在快中斷中采取了 兩個措施:

- 專門為快中斷配置了較多的私有寄存器,從而可使中斷服務程序有足夠的寄存器來使用,而不必與被中斷服務程序使用同一組寄存器,這樣就免去了因寄存器沖突而必需的保護及恢復現場工作。

- ARM把FIQ的中斷向量放在了中斷(異常)向量表末尾 0X0000001C處,因此它后面沒有其它中斷向量,允許用戶將中斷服務程序直接放在這里。

-

響應條件

- 只有當CPSR中相應的F位被清零時,才可能發生FIQ異常。

- 將ARM內核的nFIQ信號拉低,可實現外部產生FIQ,FIQ異常是優先級最高的外部中斷。

- 內核進入FIQ處理程序之后,FIQ、IRQ同時禁止任何外部中斷源再次發生中斷,除非在軟件中重新使能IRQ、FIQ請求。

- 當F控制位被清零時,ARM在每條指令執行結束時檢測FIQ同步器輸出端的低電平。

- FIQ異常進入與退出的流程與IRQ類似。

-

流程

- 同理PC還是+4

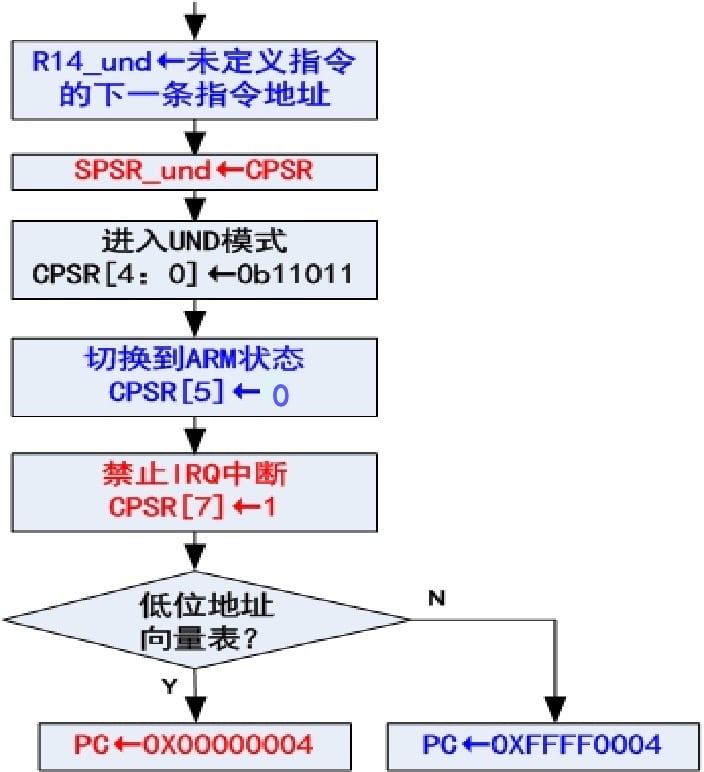

四、未定義指令異常

-

未定義指令異常是內部異常中斷。當ARM處理器遇到一條自己和系統內任何協處理器都無法執行的指令時,就會發生未定義指令異常,從而進入中斷處理程序;

-

軟件可使用這一機制,通過仿真未定義的協處理器來擴展ARM指令集。

-

返回方式

- 在仿真未定義的指令后,不管處于哪種處理器操作狀態(ARM或Thumb狀態),處理器執行下面的指令返回:

- MOVS PC, R14_und

- MOVS指令將R14的值寫入PC,CPSR將自動從SPSR寄存器中恢復并返回到未定義指令之后的指令。

- 在仿真未定義的指令后,不管處于哪種處理器操作狀態(ARM或Thumb狀態),處理器執行下面的指令返回:

-

響應流程:

五、中止異常

-

中止表示當前對存儲器的訪問不能被完成,這是由外部ABORT輸入信號引起的異常中斷。

-

中止有2種類型:

-

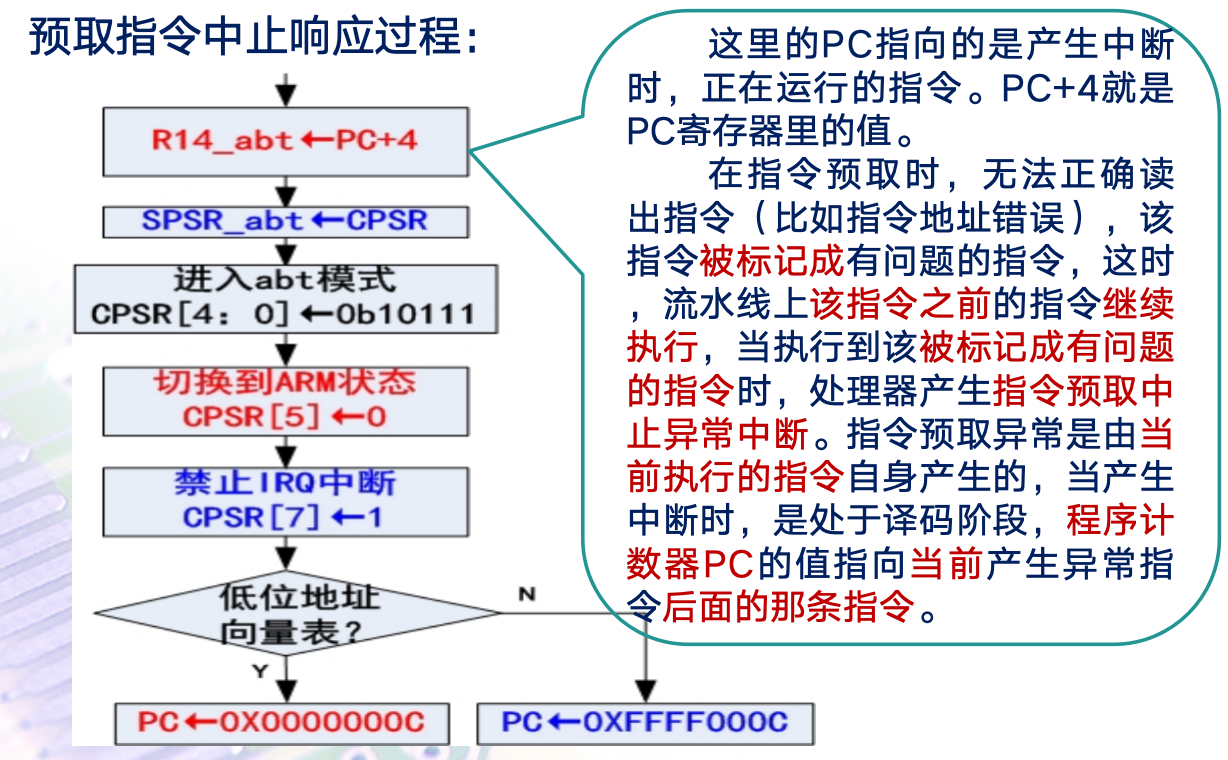

預取指中止:由程序存儲器出錯引起的中止異常;

-

數據中止:由數據存儲器出錯引起的中止異常。

-

-

預取指中止異常:

-

當發生預取中止時,ARM內核將預取的指令標記為無效,但在指令到達流水線的譯碼階段時才進入異常。如果指令在流水線中因為分支而沒有被執行,中止將不會發生。

-

流程:

-

-

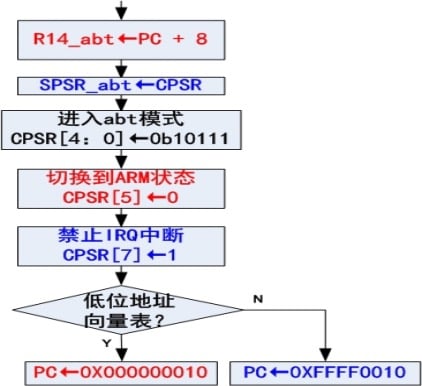

數據中止異常

-

當發生數據中止異常時,理想的狀況是進入數據中止異常的ISR,然后在內存中挑選出問題,再重新執行導致異常的指令。于是就會將PC返回2條指令,也就是將R14的值減去8,并將結果存入PC。

-

流程

-

六、SWI軟件中斷異常

-

事實上,所有的任務都是在用戶模式下運行的,因此任務只能讀CPSR而不能寫CPSR。**任務由用戶模式切換到特權模式的唯一途徑,就是使用一個SWI指令調用。**SWI指令強迫處理器從用戶模式切換到SVC管理模式,并且IRQ中斷自動關閉,所以軟件中斷方式常被用于系統調用。只有處理器切換到系統模式時,IRQ中斷才能繼續使用。

-

由于它是由用戶在程序中使用指令而產生的中斷,所以叫做軟中斷。它也是所有中斷(異常)中唯一的一個同步事件。

- 同步事件的發生時機是確定的,因為它是由程序中的指令直接觸發的。例如,當程序執行到

SWI指令時,軟中斷一定會發生。 - 與異步事件(如硬件中斷)不同,異步事件的發生時機是隨機的,因為它是由外部硬件或條件觸發的,與程序執行流程無關。

- 同步異步的主要區別是發生順序的確定與否,不一定非要由時間信號約束

- 同步事件的發生時機是確定的,因為它是由程序中的指令直接觸發的。例如,當程序執行到

)

全面詳解)

)

的時間復雜度快速求區間和))

)

)