目錄

- 一、用狀態機實現LED流水燈

- 1.狀態機思想簡介

- 1. 1基本概念

- 1.2.核心要素

- 1.3分類與模型

- 2.LED流水燈

- 二、CPLD與FPGA

- 1.技術區別

- 2.應用場景

- 3.設計選擇建議

- 三、HDLbits組合邏輯題目

一、用狀態機實現LED流水燈

1.狀態機思想簡介

1. 1基本概念

? 狀態機(Finite State Machine, FSM)是一種用于描述系統行為及其狀態轉換的數學模型。它將系統抽象為有限個狀態,并通過事件觸發實現狀態間的遷移,同時可能伴隨特定的動作。其核心思想是“基于狀態的邏輯控制”,適用于具有明確階段性和條件依賴性的系統

1.2.核心要素

? 現態(Current State):系統當前所處的狀態。

? 事件(Event):觸發狀態遷移的條件(如用戶輸入、傳感器信號等)

? 動作(Action):狀態遷移時執行的操作(如開啟設備、發送數據等)

? 次態(Next State):事件觸發后系統將進入的新狀態

1.3分類與模型

? Moore型:輸出僅由當前狀態決定(如交通信號燈的紅綠燈切換)

? Mealy型:輸出由當前狀態和輸入共同決定(如網絡協議中的應答機制)

? 確定型(DFA):每個狀態對同一事件有唯一遷移路徑

? 非確定型(NFA):同一事件可能觸發多個遷移路徑,需額外邏輯處理

2.LED流水燈

核心代碼如下:

module led_flow(input clk, // 50MHz時鐘input rst_n, // 復位信號(低有效)output reg [7:0] led

);// 狀態定義(8個狀態)localparam [2:0] S0=0, S1=1, S2=2, S3=3, S4=4, S5=5, S6=6, S7=7;reg [2:0] state;reg [24:0] cnt;wire en = (cnt == 25'd24_999_999); // 分頻使能// 分頻計數器always @(posedge clk or negedge rst_n) beginif (!rst_n) cnt <= 0;else if (en) cnt <= 0;else cnt <= cnt + 1;end// 狀態機主邏輯always @(posedge clk or negedge rst_n) beginif (!rst_n) beginstate <= S0;led <= 8'b00000001; // 初始狀態S0點亮LED0endelse if (en) begincase(state)S0: begin led <= 8'b00000010; state <= S1; end //S0→S1(第2個LED亮)S1: begin led <= 8'b00000100; state <= S2; end //S1→S2(第3個LED亮)S2: begin led <= 8'b00001000; state <= S3; end //S2→S3(第4個LED亮)S3: begin led <= 8'b00010000; state <= S4; end //S3→S4(第5個LED亮)S4: begin led <= 8'b00100000; state <= S5; end //S4→S5(第6個LED亮)S5: begin led <= 8'b01000000; state <= S6; end //S5→S6(第7個LED亮)S6: begin led <= 8'b10000000; state <= S7; end //S6→S7(第8個LED亮)S7: begin led <= 8'b00000001; state <= S0; end //S7→S0(第1個LED亮,循環)default: state <= S0; // 默認回到初始狀態endcaseendend

endmodule

仿真文件編寫:

`timescale 1ns / 1ps

module led_flow_tb;// 輸入信號reg clk; // 50MHz時鐘reg rst_n; // 復位信號(低有效)// 輸出信號wire [7:0] led; // LED輸出// 實例化被測模塊led_flow uut (.clk(clk),.rst_n(rst_n),.led(led));// 1. 生成50MHz時鐘initial beginclk = 0;forever #10 clk = ~clk; // 周期20ns(50MHz)end// 2. 控制復位信號initial beginrst_n = 0; // 初始復位有效#100; // 保持100ns復位rst_n = 1; // 釋放復位#2000000000; // 仿真運行2秒(覆蓋多個狀態循環)$finish; // 結束仿真end// 3. 監視信號變化initial begin$monitor("Time=%tns | State=%d | LED=%b", $time, uut.state, led);end

endmodule

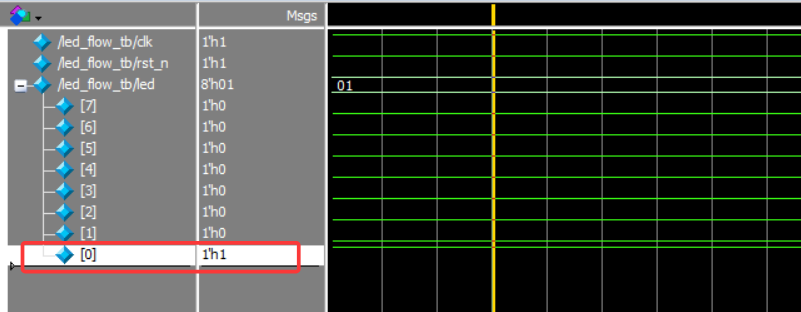

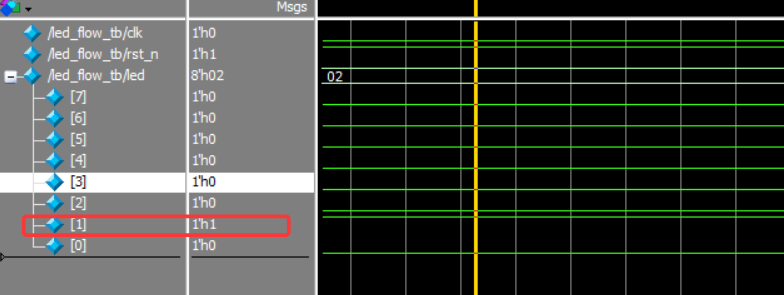

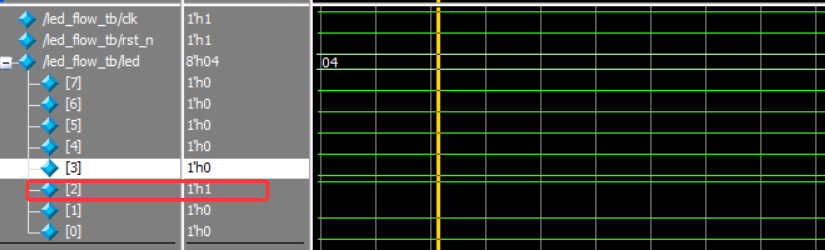

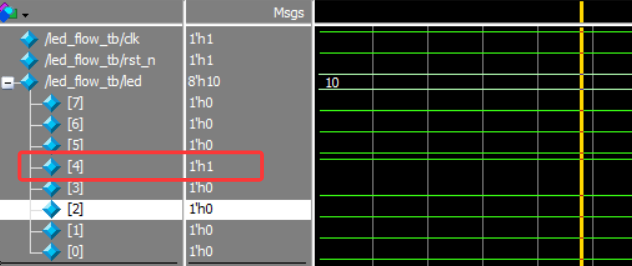

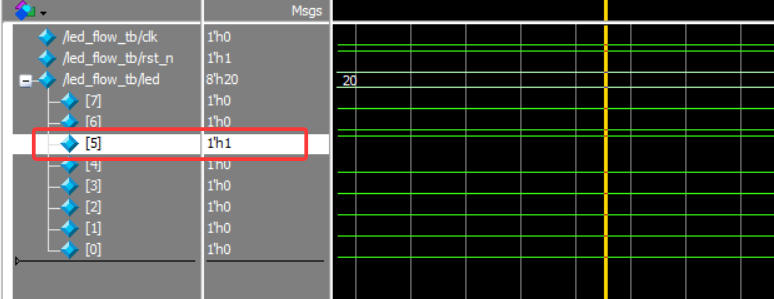

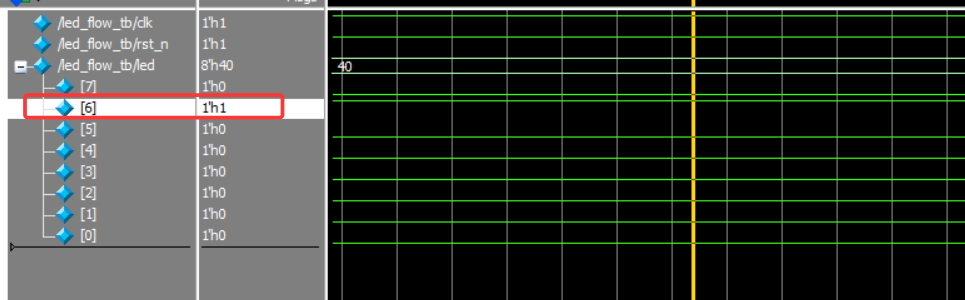

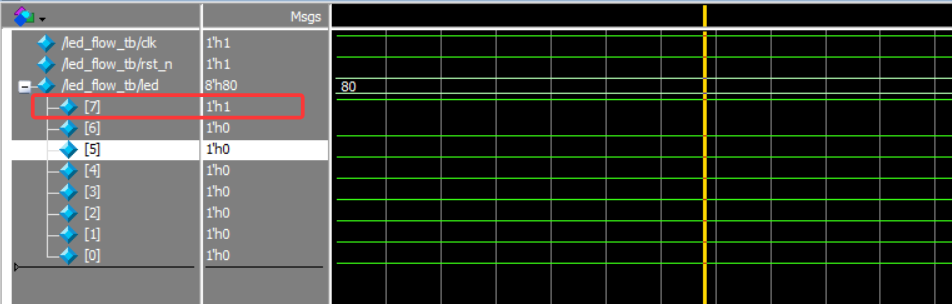

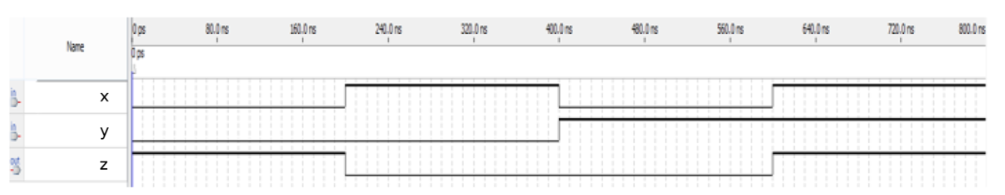

仿真:

因為我流水燈的周期太長了,沒有辦法顯示全,所以調整分頻

wire en = (cnt == 25'd4_999_999); // 分頻使能

可以看到仿真結果符合預期

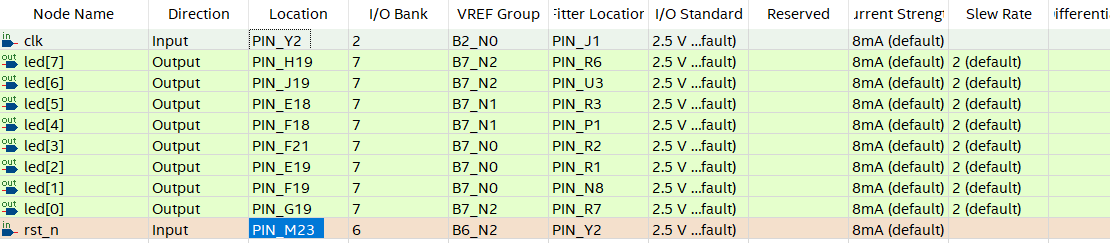

引腳綁定:

實現效果:

led 流水燈狀態機思想

二、CPLD與FPGA

1.技術區別

| 特性 | CPLD | FPGA |

|---|---|---|

| 架構 | 基于乘積項(Product Term)結構,邏輯塊較大 | 基于查找表(LUT)結構,邏輯單元粒度小 |

| 資源規模 | 較小(通常<10萬門) | 較大(可達數百萬門) |

| 時序特性 | 延時均勻,可預測性強 | 延時依賴布局布線,需時序約束優化**7 |

| 編程方式 | 非易失性(EEPROM/Flash),無需外部配置 | 易失性(SRAM),需外部存儲器加載配置 |

| 功耗 | 靜態功耗低,適合低功耗場景 | 動態功耗高,適合高性能計算 |

| 重構靈活性 | 配置固定,不支持動態重構 | 支持實時動態重構 |

2.應用場景

-

CPLD:

- 控制密集型系統:如接口轉換(UART轉SPI)、簡單狀態機、工業控制邏輯

- 低功耗場景:電池供電設備,需長期穩定運行

- 快速原型驗證:中小規模邏輯的快速實現

-

FPGA:

-

數據密集型系統:圖像處理、高速通信(如PCIe)、數字信號處理(DSP)

-

復雜算法加速:深度學習推理、加密解密算法

-

可重構計算:航天電子設備需在軌更新功能

-

3.設計選擇建議

-

若需簡單邏輯控制且對成本敏感,選CPLD

-

若需高性能并行處理或動態重構,選FPGA

三、HDLbits組合邏輯題目

HDLBits(點擊進入練習) 是一個專注于 Verilog硬件描述語言(HDL)學習和實踐 的在線平臺,由多倫多大學開發,旨在通過小型電路設計習題幫助用戶:夯實Verilog基礎、理解數字電路設計思想(例如狀態機設計、時序約束優化等關鍵概念)、銜接實際項目(平臺題目與FPGA開發中的常見模塊,如FIFO、接口控制器,高度相關)

題目1:簡單電路B

module top_module ( input x, input y, output z );assign z = ~(x ^ y);

endmodule

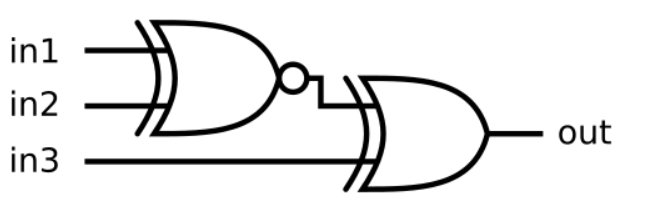

題目2:Two gates

module top_module (input in1,input in2,input in3,output out);assign out=(~(in1^in2))^in3;

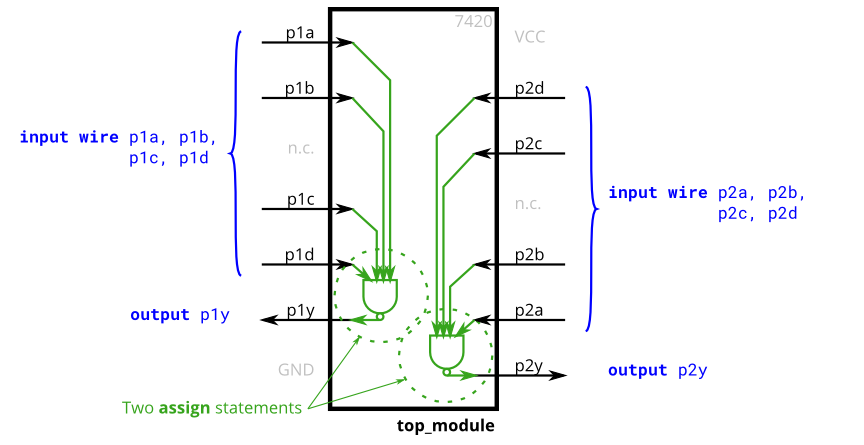

endmodule題目3:7420chip

module top_module ( input p1a, p1b, p1c, p1d,output p1y,input p2a, p2b, p2c, p2d,output p2y );assign p1y=~(p1a&p1b&p1c&p1d);assign p2y=~(p2a&p2b&p2c&p2d);

endmodule

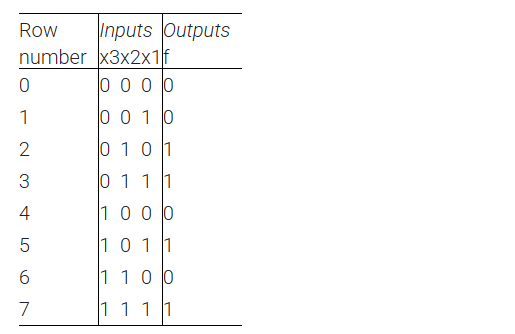

題目4:真值表

module top_module( input x3,input x2,input x1, // three inputsoutput f // one output

);wire and1 = (~x3 & x2 & ~x1);wire and2 = (~x3 & x2 & x1);wire and3 = (x3 & ~x2 & x1);wire and4 = (x3 & x2 & x1);assign f = and1 | and2 | and3 | and4;

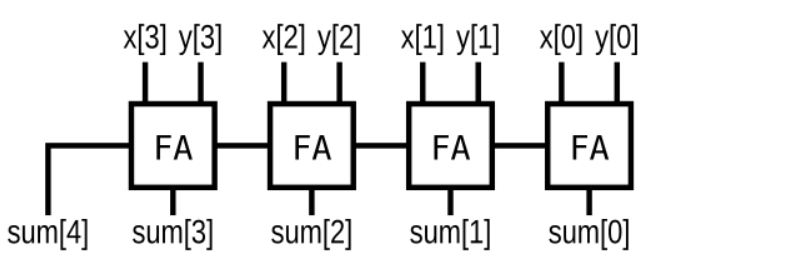

endmodule題目5:加法器

module top_module (input [3:0] x, input [3:0] y, output [4:0] sum);assign sum = x + y;

endmodule參考鏈接:

百度詞條CPLD與FPGA

CPLD與FPGA的用途及其區別

百度百科狀態機

聊一聊狀態機

數組中的第K個最大元素)