一、引言

? ? ? ? 在FPGA(現場可編程門陣列)設計中,時鐘信號是不可或缺的關鍵要素。時鐘信號作為時序邏輯的心跳,推動著FPGA內部各個存儲單元的數據流轉。無論是實現復雜的邏輯運算還是處理高速數據流,都需要精確的時鐘信號來保證時序的正確性和數據的準確性。本文將詳細介紹FPGA時鐘的基本概念、時鐘電路結構原理以及時鐘設計中的重要考量。? ? ? ?

? ? ? ??

二、FPGA時鐘的基本概念

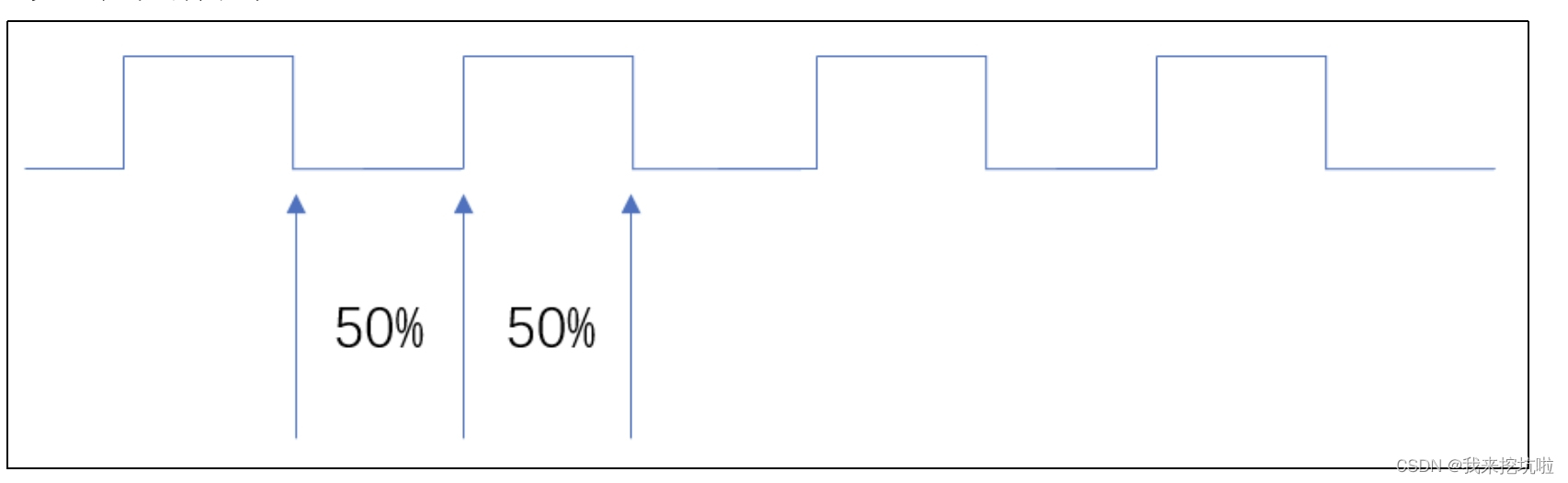

? ? ? ? FPGA中的時鐘信號通常具有固定的周期和頻率,以方波的形式存在。時鐘周期是指一個時鐘邊沿到下一個同類時鐘邊沿之間的時間間隔,而時鐘頻率則是時鐘周期的倒數。時鐘信號的基本特征包括占空比,即波形處于高電平占周期的時間比。

? ? ? ? 理想的時鐘模型是一個占空比為 50%且周期固定的方波。時鐘是 FPGA 中邏輯運行的

一個基準。如下圖所示:

? ??

? ??

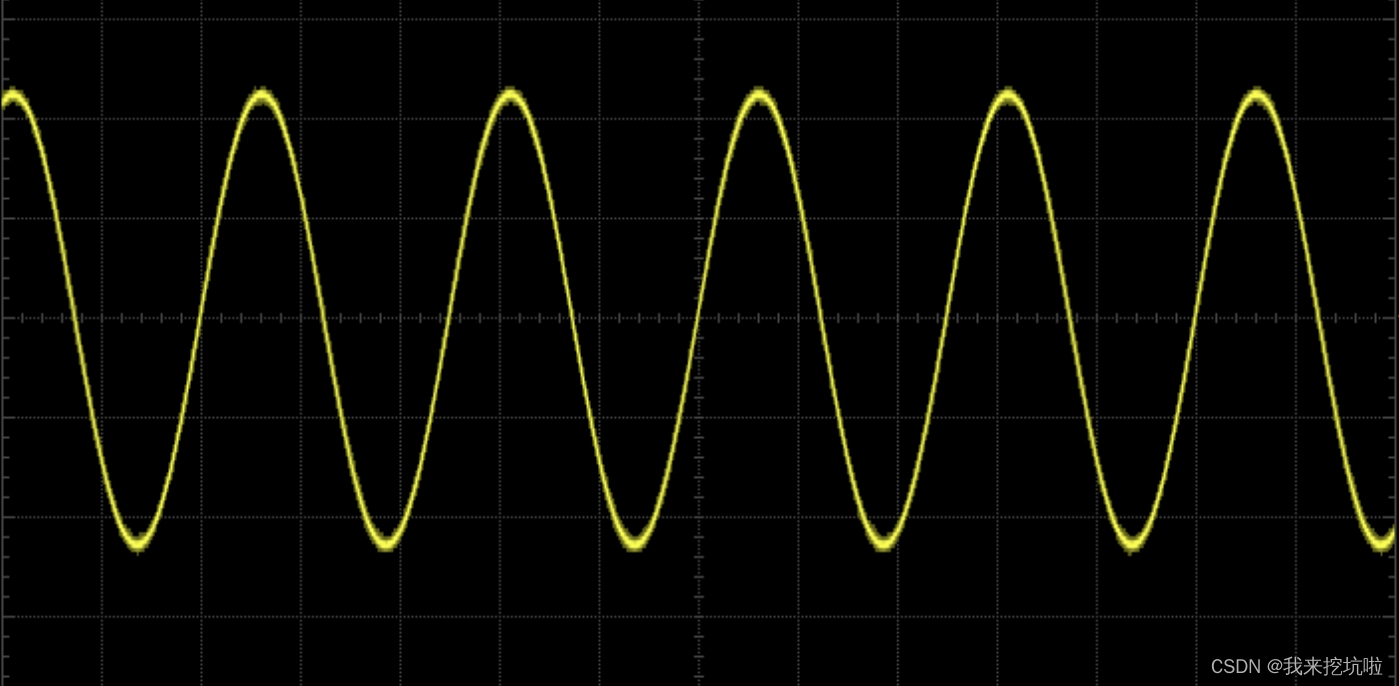

? ? ? ?實際電路中輸入給 FPGA 的晶振時鐘信號其實是正弦波,這個波形不影響 FPGA 對時

鐘的識別。

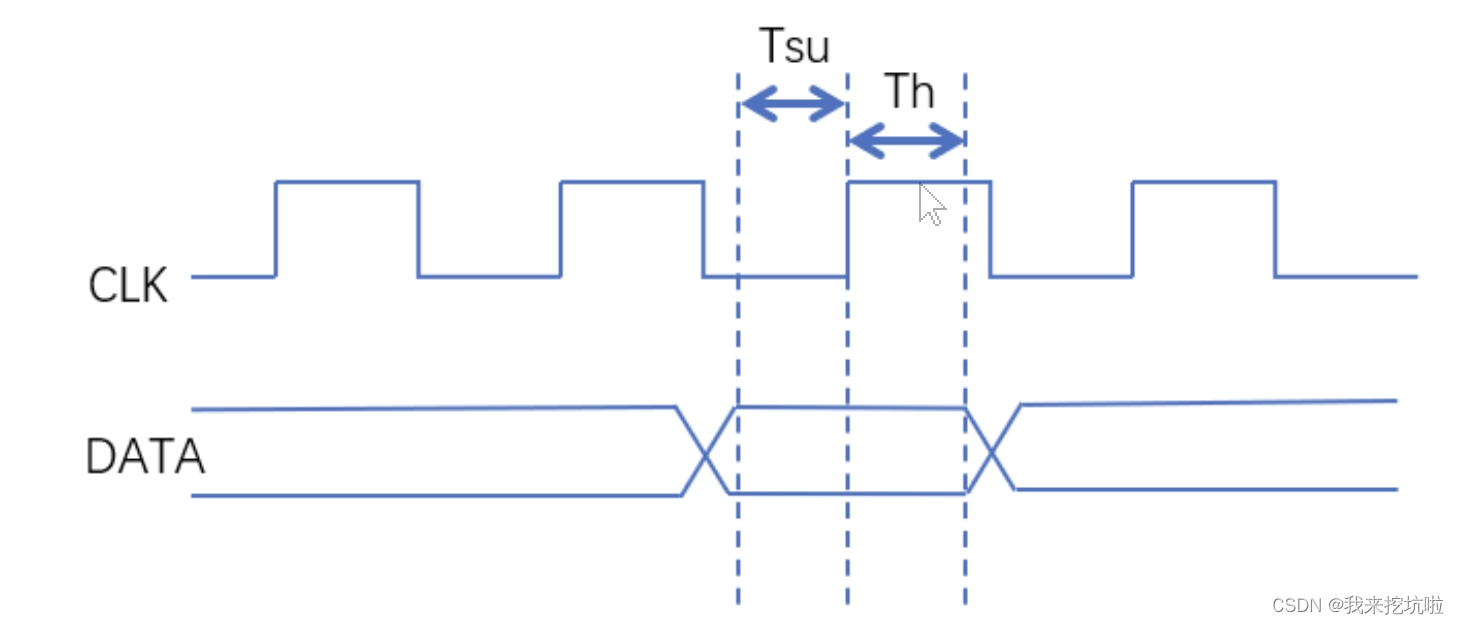

? ? ? ? 時鐘信號在FPGA設計中起著至關重要的作用。它用于同步數字信號發射器和接收器,確保數據傳輸過程中的同步性。在數據傳輸過程中,發射器可以在時鐘信號的每個上升沿或下降沿發送數據位,而接收器則可以使用相同的時鐘信號來讀取數據。時鐘的有效邊沿(即上升沿或下降沿)對于確保數據傳輸的正確性至關重要。

三、FPGA時鐘電路結構原理

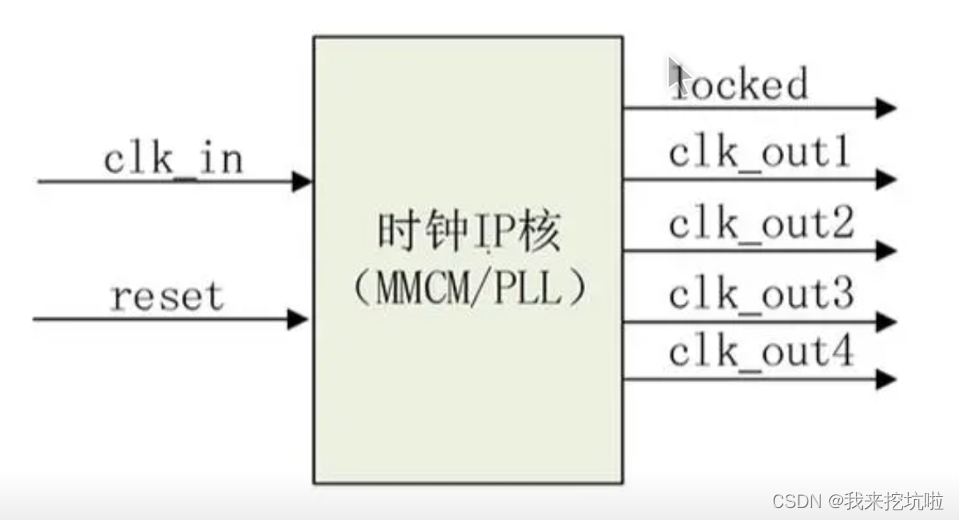

? ? ? ? FPGA中包含了一些全局時鐘資源,這些資源由時鐘管理器(CMT)產生。以AMD公司近年的主流FPGA為例,時鐘資源包括DCM(數字時鐘管理器)、PLL(相位鎖定環)和MMCM(混合模式時鐘管理器)等【后續會對這些IP核進行比較系統的講解】。其中,DCM在舊器件中應用較多,但目前已逐漸被淘汰;PLL是較為常見的時鐘資源,可以實現分頻、倍頻及相位調節等功能;MMCM在PLL的基礎上提供了更為強大的高階功能,如動態相位調節、時鐘擴頻功能及時鐘分配動態變化等。

?

? ? ? ? 在FPGA設計中,時鐘信號的分配和布線是至關重要的。正確的時鐘信號分配可以確保數據在正確的時間被處理和傳輸。時鐘信號的布線質量對設計的性能和功耗有很大影響。此外,當設計中存在多個時鐘域時,需要正確處理不同時鐘域之間的數據傳輸,以防止時序違規和異步時鐘域之間的不穩定性問題。

?

四、FPGA時鐘設計的重要考量

- 時鐘頻率和時序約束:在設計FPGA時,需要根據應用需求選擇合適的時鐘頻率。同時,為了確保時序要求得到滿足,需要設置適當的時序約束,包括時鐘頻率約束、時序路徑約束和時鐘域約束等。

- 時鐘緩沖與時鐘延遲:在FPGA中,時鐘緩沖和時鐘延遲對時鐘信號的傳播和同步至關重要。需要注意時鐘緩沖的插入和時鐘延遲對設計的影響。

- 時鐘偏移和抖動:時鐘信號可能存在偏移和抖動,這可能導致時序不穩定或違反時序約束。因此,在時鐘設計中需要考慮時鐘信號的穩定性和可靠性。

- 門控時鐘和多級邏輯時鐘:在某些應用中,可能需要使用門控時鐘或多級邏輯時鐘來優化功耗或實現特定的功能。然而,這些時鐘設計方式可能會引入額外的時序問題,需要仔細分析和驗證。

?

五、結論

? ? ? ? FPGA時鐘是驅動數字邏輯的核心。在FPGA設計中,時鐘信號的正確性、穩定性和可靠性對系統的性能和功能有著至關重要的影響。因此,在FPGA設計中需要充分考慮時鐘信號的設計和實現方式,以確保系統的正確性和可靠性。

事件系統)

LRU緩存、)

模型的編輯、軸網和標高)

)