Verilog代碼bug:一種特殊的組合邏輯環

組合邏輯環(Combinational Loop)是什么,別的文章已經寫的很多了,本文就不贅述了,本文主要記錄遇到過的一種特殊的邏輯環;

代碼如下所示:

module test(b, a0

);input b;

output a0;assign a = !b ? a0 : 1'b1;

assign a0 = !b ? 1'b0 : a;endmodule

理論上,若b=0, 則a0 = 1’b0;

若b=1,則a0 = 1’b1;不會產生組合邏輯環

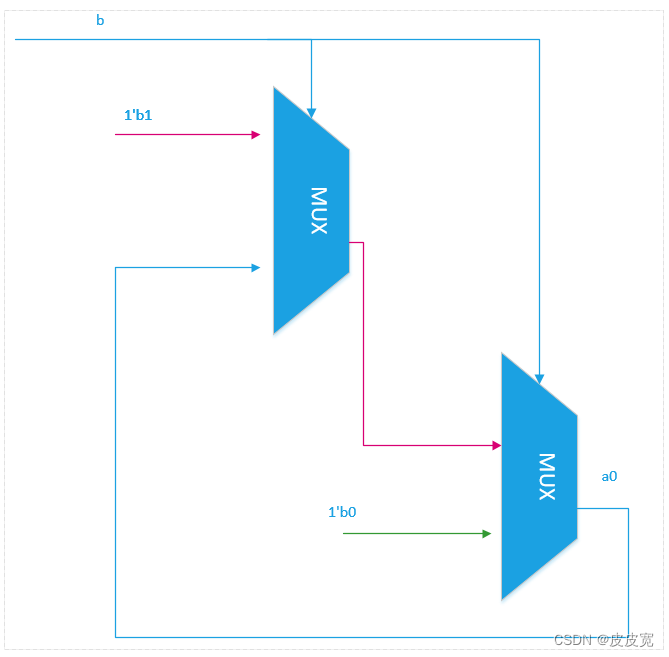

但實際電路結構如下所示:

- b = 1時,數據傳輸如紅線所示,

- b=0時,數據傳輸如綠色線所示;

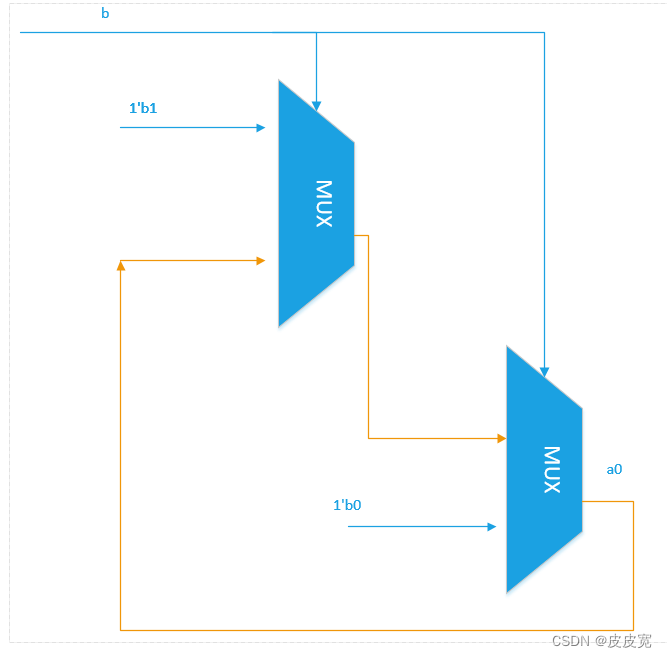

但由于b信號傳輸到兩個MUX選擇器端點存在延時的差異,因此當b從1變為0時,可能存在某一時刻,兩個MUX接受的b信號,一個是0,另一個還是1(延時差異,還未傳輸過來),從而導致如下的邏輯環路

因此,這種電路依然會產生組合邏輯環,需要被優化;

)