目錄

單選題

多選題

判斷題

單選題

1.reg[7:0]A; A=2'hFF;則A=()

A.8'b11111110

B.8'b03

C.8'b00000011

D.8'b11111111

C

2'hFF實際上等效于2位二進制2'b11,賦值給8位寄存器A之后,低位賦值,高位補0

A=8'b00000011

AMD FPGA器件中URAM的大小為()

A.18kb

B.36KB

C.288kb

D.320kb

C

URAM(Ultra RAM)是一種高性能片上存儲器,在AMD Xilinx FPGA器件中,URAM的大小同城為288kb,配置為4K*72bit的存儲單元,其容量是Block RAM的八倍

3.FPGA中的分布式RAM是由()構成

A.進位鏈

B.Block RAM

C.LUT

D.MUX

C

FPGA中的分布式RAM(Distributed RAM)是由查找表(LUT)構成的存儲資源,相比于Block RAM等其他樂行的RAM,分布式RAM可以根據需要靈活地分布在FPGA的各個區域,適合小規模、不規則的存儲需求

進位鏈主要用于實現加法等算術運算;

Block RAM是FPGA專用大容量存儲模塊;

多路選擇器MUX主要用于數據選擇;

LUT本質上是一種數據存儲邏輯單元,通過將LUT配置乘特定模式可以實現RAM的功能

【FPGA】LUT如何實現組合邏輯、時序邏輯_fpga lut-CSDN博客

4.關于AMD FPGA Slice說法錯誤的是()

A.SliceX沒有存儲功能,也沒有進位鏈

B.SliceM除具有存儲功能外,還包含進位鏈、多路復用器、查找表LUT和可變長的移位寄存器

C.SliceL具有存儲功能,但沒有進位鏈

D.Slice中含有多路復用器

A

Slice是AMD Xilinx FPGA的基本邏輯單元,由查找表(LUT)、寄存器、進位連和多路復用器(MUX)等組件構成,包括SliceX、SliceM和SliceL三種不同的類型。

SliceX具有存儲功能和進位鏈,適用于累加等運算和結果存儲,A錯

SliceM具有存儲功能、進位鏈、多路復用器、查找表和可變長移位寄存器,適用于數字信號處理算法卷積運算和數據濾波等操作,B對

SliceL僅具有存儲功能,適用于簡單邏輯處理和數據存儲,C對

Slice中包含多路復用器,D對

【基本知識】CLB、Slice、logic cell、LUT... - 要努力做超人 - 博客園

5.'b00110 ^ 'b10000的結果為()

A.'b10110

B.'b01001

C.1'b1

D.1'b0

A

異或,相同位為0,不同位為1

00110

10000

10110

6.十進制負整數-10的8bit有符號數表示正確的是()

A.8'h76

B.8'hF6

C.8'hF5

D.8'hA

B

+10

0000 1010

-10

按位取反,末尾+1

1111 0101

? ? ? ? ? ? ? ?1

1111 0110

8'hF6

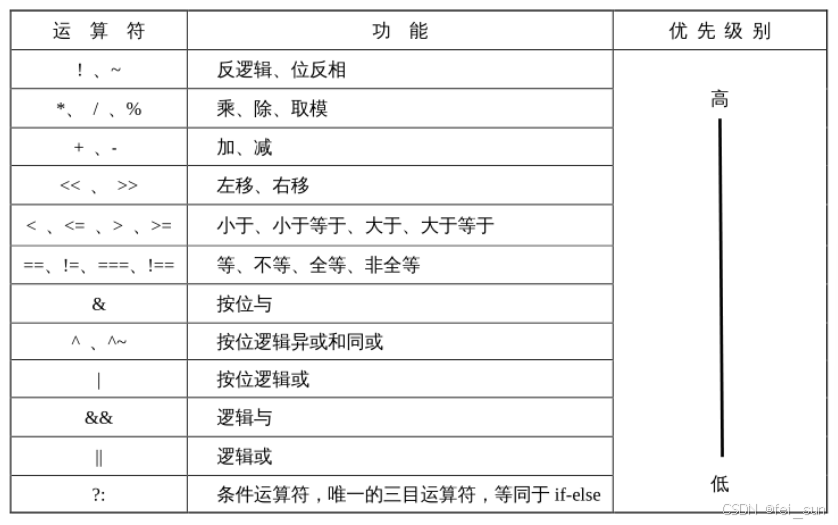

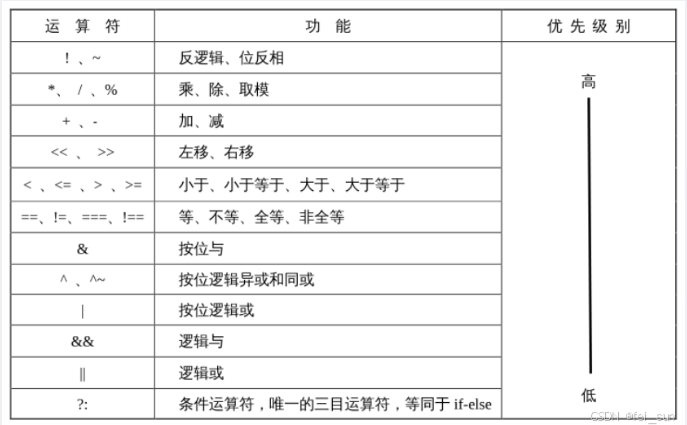

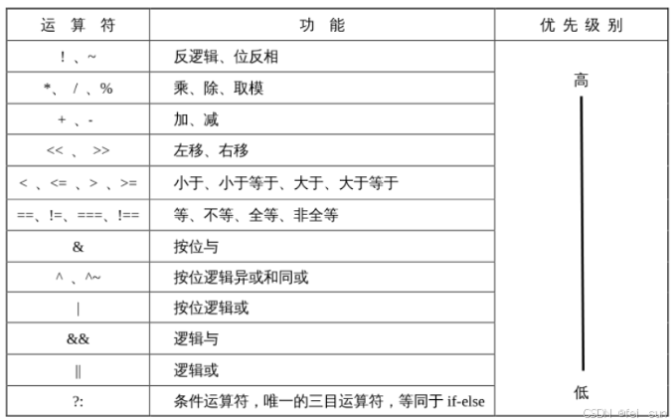

7.以下運算符,()優先級最低

A. ? :

B. + |

C. ||

D. <<

A

!? ? ? ? ~ 高(從高到低) *? ? ? ? /? ? ? ? % +? ? ? ? - <<? ? ? ? >> <? ? ? ? <=? ? ? ? >? ? ? ? >= ==? ? ? ? !=? ? ? ? ===? ? ? ? 1=== & ^ | && || ?: 低

【Verilog】基于Verilog HDL的FPGA設計基礎-CSDN博客

8.在下列程序中,always狀態將描述一個帶異步Nreset和Nset輸入端的上升沿觸發器,從選項中找出空括號內應填入的正確答案

always@()

? ? ? ? if(!Nreset)

? ? ? ? ? ? ? ? Q<=0;

? ? ? ? else if(!Nset)

? ? ? ? ? ? ? ? Q<=1;

? ? ? ? else

? ? ? ? ? ? ? ? Q<=D;

A.negedge Nset or posedge clk

B. negedge Nreset or posedge clk

C. negedge Nreset or negedge Nset

D. negedge Nreset or negedge Nset or posedge clk

根據要求實現一個帶有異步復位(Nreset)和異步置位(Nset)的上升沿觸發器,異步信號低有效,需要直接包含在敏感列表中,即敏感列表應該包括:

1. 異步復位信號(Nreset)下降沿;

2. 異步置位信號(Nset)下降沿;

3. 時鐘信號(clk)上升沿。

同時包含三個觸發條件,選擇D

特性??

??同步設計??

??異步設計??

??敏感信號類型??

僅時鐘邊沿(

posedge/negedge)時鐘邊沿 + 電平敏感信號(如復位、使能)

??敏感列表約束??

單一時鐘邊沿,不可混合其他信號

允許多個異步信號電平變化

??復位實現方式??

同步復位(通過

if條件判斷)異步復位(直接敏感列表觸發)

??時序控制??

嚴格依賴時鐘,時序確定性高

依賴信號電平,時序不確定性高

??綜合結果??

綜合為寄存器,時序邏輯

可能綜合為組合邏輯或帶異步控制的時序邏輯

9.線網中的值被解釋為無符號數。在連續賦值語句中,assign addr[3:0]=-3。addr被賦予的值是()

A.4'bxx11

B.4'bzz11

C.4'b0011

D.4'b1101

D

+30011

-3

按位取反,+1(補碼)

1100

? ? ? 1

1101

10.關于保持時間說法正確的是 ( )

A. 指時鐘采樣沿穩定之前,數據保持穩定的時間

B. 當保持時間不滿足要求時,可以降低時鐘頻率解決

C. 當保持時間不滿足時,可以調整數據走線延時解決

D. 指時鐘采樣沿穩定之后,數據保持穩定的最長時間

C

保持時間是指時鐘采樣沿到來之后,數據需要保持穩定的時間,A 錯誤;

降低時鐘頻率會使時鐘周期變長,數據的建立時間更容易滿足,但對保持時間沒有幫助,因為保持時間與時鐘周期無關,B 錯誤;

當保持時間不滿足要求時,可以通過調整數據走線延時來解決。例如,增加數據路徑的長度或插入緩沖器等,使數據到達采樣點的時間延遲,從而滿足保持時間的要求,C 正確;

保持時間是指時鐘采樣沿穩定之后,數據保持穩定的最短時間,D 錯誤

11.Verilog代碼中錯誤的注釋符是()

A. //

B. ///

C. /*...*/

D.#

D

在Verilog語言中,通常使用符號//或///實現單行注釋,使用符號/*...*/實現多行注釋。符號#是VHLDL語言的注釋方法,而非Verilog語言的注釋方式

12.SignalTap文件后綴是()

A.cdc

B.stp

C.lpf

D.sdc

B

SignalTap是Intel Altera FPGA開發工具Quarter Prime中的嵌入式邏輯分析儀,用于實時捕捉和分析FPGA內部信號,其配置文件的標準后綴為.stp(SignalTap Project)

.cdc為時鐘域交叉(Clock Domain Crossing)約束文件;

.lpf為布局與布線約束文件(Lay);

.sdc為Synopsys設計時序約束文件(Synopsys Design Constraint)

13.在Verilog語言中,下列哪個不屬于分支語句()

A.if...else

B.case

C.casez

D.repeat

D

if...else語句是典型的分支語句,根據條件判斷執行不同的代碼塊;

case和casez語句根據表達式的值執行多個分支中一部分代碼塊,casez在進行比較時會將高阻態z值視為無關項,均屬于分支語句;

repeat語句用于重復一段代碼,屬于循環語句;

14.下列EDA軟件中,哪一個不具有邏輯綜合功能()

A.Vivado

B.Quarter II

C.Synplify

D.ModelSim

D

Vivado是Xilinx FPGA開發套件,集成了邏輯綜合、實現(布局布線)和仿真功能;

Quartus II是Intel Altera FPGA 開發工具,同樣具備邏輯綜合能力;

Synplify是Synopsys推出的專業邏輯綜合工具,主要關注于將HDL代碼轉換為門級網表

Modelsim是Mentor Graphics的仿真工具,僅用于驗證設計功能,不具備邏輯綜合能力

15.下列屬于Verilog HDL非開源仿真工具的是()

A.IceStorm

B.Icarus Verilog

C.Questasim

D.Yosys

C

IceStorm是Lattice冰河系列FPGA的開源工具鏈,包含仿真等功能

Icarus Verilog是支持Verilog代碼編譯仿真的開源Verilog HDL仿真工具

QuestaSim是Mentor Graphics公司開發的Verilog HDL商業仿真軟件,屬于非開源仿真工具

Yosys是支持仿真的Verilog開源綜合工具

16.在FPGA中實現FIR濾波器時,必須要使用哪種資源()

A.DSP

B.LUT

C.SRL

D.BRAM

B

DSP模塊是用于高速乘法和累加專用硬件,雖然FIR濾波器使用DSP可以顯著提升性能,但是小規模FIR濾波器完全可以由LUT實現;

LUT是用于實現組合邏輯的FPGA基本邏輯單元,FIR濾波器的核心運算是乘法和累加,其中乘法器可以由LUT或DSP模塊實現,控制邏輯和其他賦值功能仍然需要LUT支持,因此LUT是實現FIR濾波器的必須資源;

SRL用于實現數據延遲功能,可以使用普通寄存器替代

BRAM用于數據存存儲功能,可以使用普通寄存器替代

17.AMD的1個可編程邏輯(CLB)內共有幾個LUT()

A.1

B.2

C.4

D.8

D

AMD Xilinx FPGA的可編程邏輯塊(CLB)結構中,每個CLB由兩個Slice(SliceL和SliceM)構成,每個Slice包含4個6輸入LUT(可配置32*1位RAM或移位寄存器)

所以,每個CLB共包含8個LUT

18.選出下列運算符中優先級最低的一個()

A.!

B.&

C.||

D.<<

C

19.下列不屬于底層可編程邏輯(CLB)的基本構成元素的是()

A.查找表(LUT)

B.乘法器(DSP)

C.寄存器(FF)

D.進位鏈(CARRY4)

B

可編程邏輯塊(CLB)是FPGA的底層單元,不同廠家的CLB具體結構有所不同,但是通常都包含查找表(LUT)、寄存器(FF)和進位鏈(CARRY4)等基本構成元素,其中LUT用于實現組合邏輯功能,FF用于實現時序邏輯功能和數據存儲,CARRY4用于實現快速進位運算,DSP通常是獨立于CLB的高速乘法運算專用資源,不屬于CLB構成部分

20.關于設計文件的代碼注釋率描述正確的是()

A.無需進行代碼注釋

B.代碼注釋符是'/'

C.注釋是為了更好的維護代碼

D.代碼注釋會干擾編譯器

C

多選題

1.FPGA DSP資源可以完成哪些功能

A.加法和減法運算

B.乘累加運算

C.乘法運算

D.邏輯運算

ABC

DSP模塊是FPGA的專用硬件資源,主要用于高效實現高性能算術運算,典型功能包括:

加法和減法運算:DSP模塊內置加法器/減法器,可以直接實現高速加減運算,常用于FIR濾波器的累加部分

累乘加運算(MAC):DSP模塊通過級聯乘法器和累加器實現乘累加勻速那,常用于傅里葉變換FFT和卷積運算

乘法運算:DSP模塊包含專用乘法器,可以實現高速定點或浮點乘法,勻速效率遠高于LUT

DSP模塊的主要功能包括加法和減法運算、乘法運算,邏輯運算由查找表LUT資源完成

2.可以用于FPGA功能仿真的語言有哪些()

A.Verilog

B.SystemVerilog

C.Perl

D.SystemC

ABD

FPGA功能仿真主要使用硬件描述語言(HDL)或專用仿真語言,Verilog是主流的HDL語言,廣泛應用于FPGA設計和仿真,所有FPGA工具鏈(例如Vivado和Quartus)都支持Verilog語言;

SystemVerilog是Verilog的擴展,增加面向對象特性和驗證功能(如約束隨機測試),廣泛應用于復雜設計驗證;

Perl是腳本語言,主要應用于自動化任務(如測試腳本生成),不直接應用于硬件行為描述和仿真;

SystemC是C++的擴展,主要應用于系統級建模和硬件-軟件協同仿真,常用于ASCI設計,也可以用于FPGA高層次驗證

3.對于FPGa管腳輸入信號的建立時間()和保持時間(

)約束,以下說法正確的是()

A.保持時間約束可以通過調整數據路徑延時解決

B.建立時間約束僅與時鐘頻率有關

C.靜態時序分析工具會同時驗證和

是否滿足

D.異步時鐘域的/

約束比同步時鐘域更復雜

ACD

當保持時間不滿足時,可通過增加數據路徑延時(如插入緩沖器)使數據延遲到達,確保時鐘沿后數據穩定時間滿足

要求;

建立時間約束與時鐘頻率、數據路徑延時、時鐘抖動等因素相關,并非僅由時鐘頻率決定;

靜態時序分許(STA)工具會分別檢查所有路徑的建立時間和保持時間是否滿足約束,任何一項違例都會報錯;

異步時鐘域需要考慮時鐘間的相位差和抖動,通常需要特殊處理(如異步FIFO和打拍器),約束更為復雜

4.下列哪些說法是錯誤的()

A.FPGA的配置程序在器件斷電后消失

B.時鐘沿觸發的觸發器本質上也是組合器件組成的

C.TTL與CMOS電平可以直接互連

D.鎖存器是邊沿觸發器件

BCD

FPGA通常采用SRAM工藝存儲配置數據,數據斷電后丟失,需要通過外部Flash重新加載;

觸發器是時序邏輯器件,由門電路構成的鎖存器和時鐘控制電路組成,本質上依賴時鐘邊沿觸發,與組合邏輯有本質區別;

TTL輸出高電平(2.4V)與COMS輸入高電平閾值(3.5V~5V)不匹配,需要通過電平轉換器(例如74LVC系列)或上拉電阻適配,不能直接互連;

鎖存器是電平觸發事件,例如D鎖存器在時鐘高電平時透明,而觸發器是邊沿觸發事件,僅在時鐘上升沿或下降沿采樣

5.FPGA的常用設計方法包括()

A.并發設計

B.流水線設計

C.乒乓緩存

D.源同步設計

BCD

FPGA常用設計方法是指針對其并行計算特性和資源特點優化的技術,包括流水線設計、乒乓緩存和源同步設計等:

流水線設計:將復雜邏輯拆分為多級寄存器級聯的階段,提高時鐘頻率

乒乓緩存:使用雙緩存區交替處理數據,實現數據流無縫切換;

源同步設計:數據與時鐘同源傳輸,例如DDR接口利用DQS信號消除時鐘偏移,提高高速數據傳輸可靠性

“并發設計”是FPGA通過硬件資源復用實現的廣義概念,并非常用設計方法

6.下面可能會產生Latch的情況有()

A.if...else語句不完備

B.缺少begin...end

C.case語句中缺少default

D.復位操作時,信號賦值是變量

AC

在Verilog/VHDL中,鎖存器(Latch)通常由不完整的條件賦值產生,使組合邏輯記住當前狀態,增加時序分析復雜度,導致毛刺和亞穩態,降低設計系統的可靠性

if...else語句不完備,沒有對應的else分支,綜合工具會生成Latch保持上一個狀態;

缺少begin...end僅影響代碼塊范圍,不會直接導致Latch;

case語句中缺少default,代碼不能覆蓋所有可能得輸入,綜合工具會生成Latch保持未定義狀態下的輸出;

復位操作時,信號賦值是變量與Latch無關

7.對于提高FPGA設計的時鐘頻率,下列說法正確的是()

A.增加流水級別,分割組合邏輯

B.組合邏輯平衡(register balance-register retiming)

C.寄存器復制,減少一個寄存器的輸出(register duplicate),控制扇出,規定每個寄存器的最大扇出

D.優化狀態機編碼,使用ONE-HOT獨熱碼進行編碼

ABCD

提高FPGA時鐘頻率的核心是縮短關鍵路徑時延,即寄存器到寄存器之間的組合邏輯延時。

增加流水級別,分割組合邏輯,使每級組合邏輯延時縮短,從而允許更高的時鐘頻率;

通過調整寄存器的位置,例如將寄存器存邏輯前級移到后級,重新平衡組合邏輯延時,使路徑延時更加均勻,提升整體時序性能;

當單寄存器驅動多負載導致扇出過大時,輸出網絡的電容負載會增加RC時延,通過賦值寄存器降低單寄存器的扇出,可以減少輸出延時改善時序;

獨熱碼利用1位表示1個狀態,雖然導致寄存器數量增加,但組合邏輯譯碼復雜度顯著降低;

8.下列關于行為描述和結構描述特點正確的是()

A.行為描述是指描述電路的功能行為

B.結構描述有門級和開關級

C.結構描述是指描述元件或較大部件的互連

D.行為級描述有系統級、算法級和RTL級

ABCD

在硬件描述語言(HDL)中,行為描述和結構描述是兩種核心建模方式,行為描述側重于電路功能,結構描述側重于電路實現。

行為描述是指描述電路的功能行為,不涉及具體硬件結構,按照抽象層級可以分為系統級、算法級和RTL級;

結構描述是指底層元件實例化與接口互聯,包括門級和開關級

9.在下列程序中,給出了幾種硬件實現,以下的模塊被綜合后可能是哪種?()

always@(posedge clk)

? ? ? ? if(A)

? ? ? ? ? ? ? ? C=B;

A.一個上升沿觸發器和一個多路器

B.一個輸入是A,B,clk的三輸入與門

C.一個透明鎖存器

D.一個有使能引腳的clk上升沿觸發器

AD

根據代碼分析:行為描述的是時鐘邊沿觸發的寄存器邏輯,屬于時序邏輯電路,與門和鎖存器均屬于組合邏輯電路,B、C錯誤;

if(A)語句可以被綜合為組合邏輯多路器,或觸發器的使能信號。

若綜合為組合邏輯多路器,當A=1時,多路選擇器B作為輸入,當A=0時,多路器默認保持寄存器原值,此時代碼被綜合為一個上升沿觸發器和一個多路器;

若綜合為觸發器的使能信號,當A=1時,時鐘上升沿到來時更新數據,當A=0時,數據保持原值,此時代碼被綜合為一個帶有使能引腳的clk上升沿觸發器

10.對FPGA器件的接口約束正確的有()

A.所有同步輸入信號都要進行建立時間和保持時間

的約束

B.約束的建立時間小于實際測得的建立時間和保持時間,以保證一定的時序裕量容忍實際工作過程中存在的時序波動

C.具體的約束值需要參考邏輯器件輸入管腳實際測得的時鐘數據相位關系確定

D.建立時間和保持時間無需約束

AC

所有同步輸入信號都要進行建立時間

和保持時間

的約束,避免產生亞穩態;

約束的建立時間應大于實際測得的建立時間和保持時間,以確保設計在最壞情況下仍滿足時序;

具體的約束值需要參考邏輯器件輸入管腳實際測得的時鐘數據相位關系確定;

未約束建立時間和保持時間會導致靜態時序分析工具無法驗證時序,可能在實際運行中出現亞穩態或數據采樣錯誤

判斷題

1.邏輯開發軟件的版本沒有統一要求,任何補訂的版本都可以使用()

A.錯誤

B.正確

A

邏輯開發軟件(如Vivado、Quartus、ISE等)的版本選擇對設計流程至關重要,不同版本軟件對硬件器件、IP核和第三方工具的支持存在差異,低版本軟件可能不支持新器件或新特性,高版本軟件可能無法打開舊版本工程文件;

新版本通常修復舊版本的bug、優化性能或增加新功能,若設計依賴某版本特有的功能或存在已知bug,必須使用特定版本;

團隊開發需統一版本,避免因版本差異導致設計不兼容,例如網表格式、約束文件語法,維護舊項目時,可能需要使用與原開發一致的版本,否則可能因工具鏈變化導致編譯失敗;

部分軟件版本的許可證類型不同,功能限制或授權范圍可能影響設計流程

2.Verilog語言運算符沒有優先級()

A.錯誤

B.正確

A

3.Moore狀態機的輸出由輸入和當前狀態確定()

A.錯誤

B.正確

A

狀態機根據輸出信號是否與輸入信號相關可以分為Moore狀態機和Mealy狀態機:

Moore狀態機的輸出僅由當前狀態決定,與輸入信號無關;

Mealy狀態機的輸出由當前狀態和輸入信號共同決定

4.使用四個空格符縮排,可以使用TAB鍵()

A.錯誤

B.正確

A

在代碼編寫過程中,不同編輯器對TAB鍵的解析不同,可能為 4 個空格,也可能為 8 個空格,空格和TAB混合使用將導致代碼縮進混亂,影響代碼的可讀性。代碼開發團隊應遵循統一的縮進風格,選擇全空格或全TAB的縮排方式

5.模塊內部的聲明,reg類型必須要聲明,wire類型可以不聲明()

A.錯誤

B.正確

A

在Verilog語言中,無論是reg還是wire類型的信號都必須顯式聲明后才能使用。其中,reg類型信號用于存儲數據或表達時序邏輯;wire類型信號用于連接不同模塊或表達組合邏輯

)

)

——心若安,便是晴天;心若亂,便是陰天。)

)

機制)

)