hclk的分頻電路,得到的分頻時鐘作為sd卡時鐘。

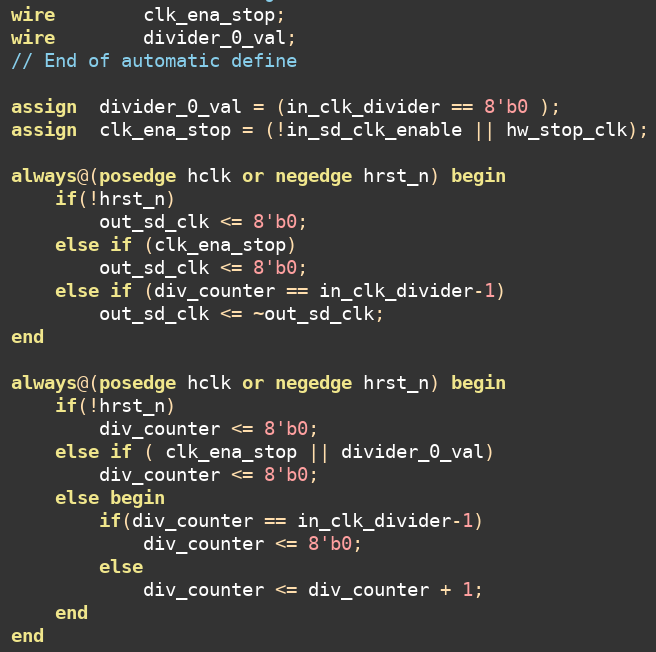

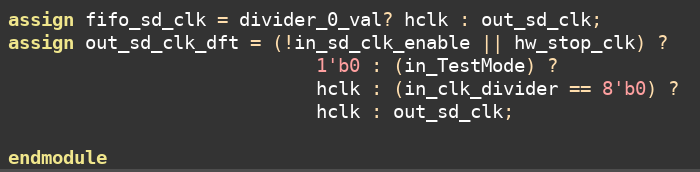

該模塊最終輸出兩個時鐘:一個為fifo_sd_clk,另一個為out_sd_clk_dft。當不分頻時,fifo_sd_clk等于hclk;當分頻時候,div_counter開始計數,記到相應分頻的時候,將hclk進行翻轉,得到分頻的時候給到fifo_sd_clk;當sd clk使能為低或者停時鐘信號為高的時候,fifo_sd_clk為0。

第二個為out_sd_clk_dft。當sd clk使能為低或者停時鐘信號為高的時候,fifo_sd_clk為0。當進入testmode的時候,接hclk;當不進入testmode時,分頻系數為0 的時候為hclk,分頻系數不為0的時候,則接分頻后的時鐘。

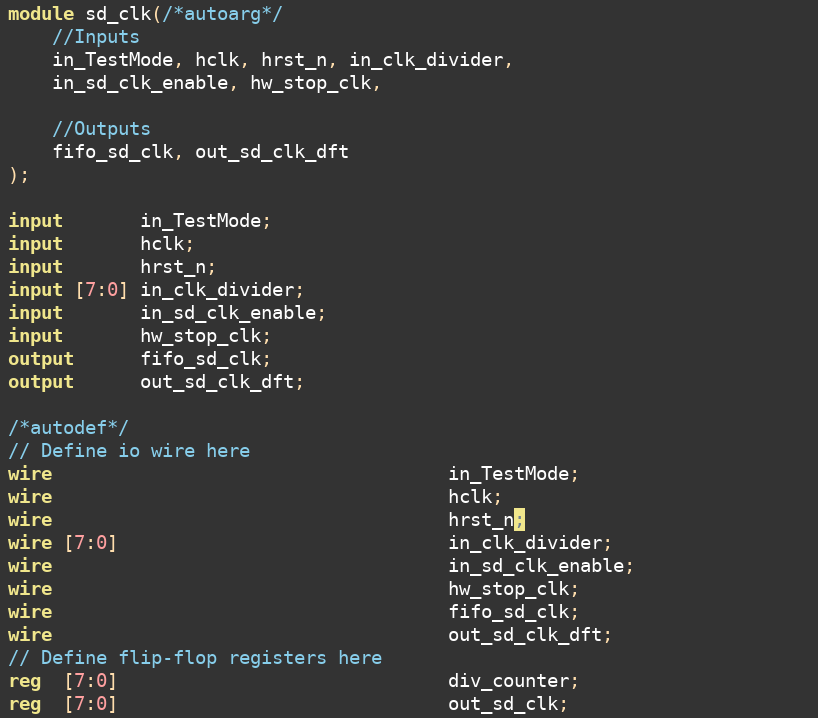

代碼實現:

)

![[計算機網絡]網絡層](http://pic.xiahunao.cn/[計算機網絡]網絡層)