作者:Hello,Panda

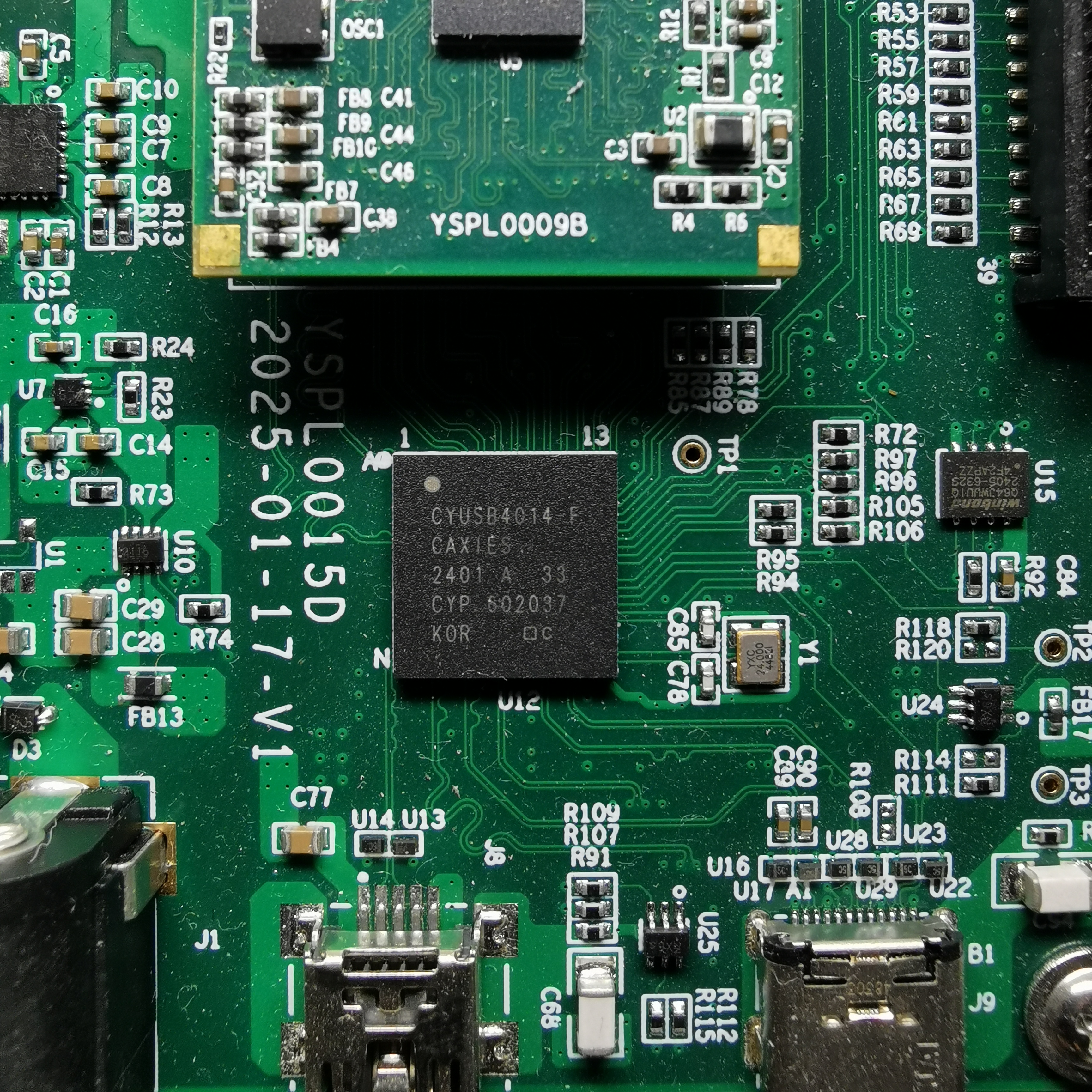

大家早上好,中午好,下午好,晚上好,熊貓君又來了。這次計劃做一個連載,大概6期左右,主要介紹英飛凌最新的FX5/10/20的器件應用。目前,熊貓君手上調試的是一個Sensor(IMX586)+Crosslink-NX FPGA(LIFCL-40)+ FX10(CYUSB4014)的一套板子,調試FPGA采集Bayer圖像經USB3.2(10Gbps)傳輸到計算機。

一、器件介紹

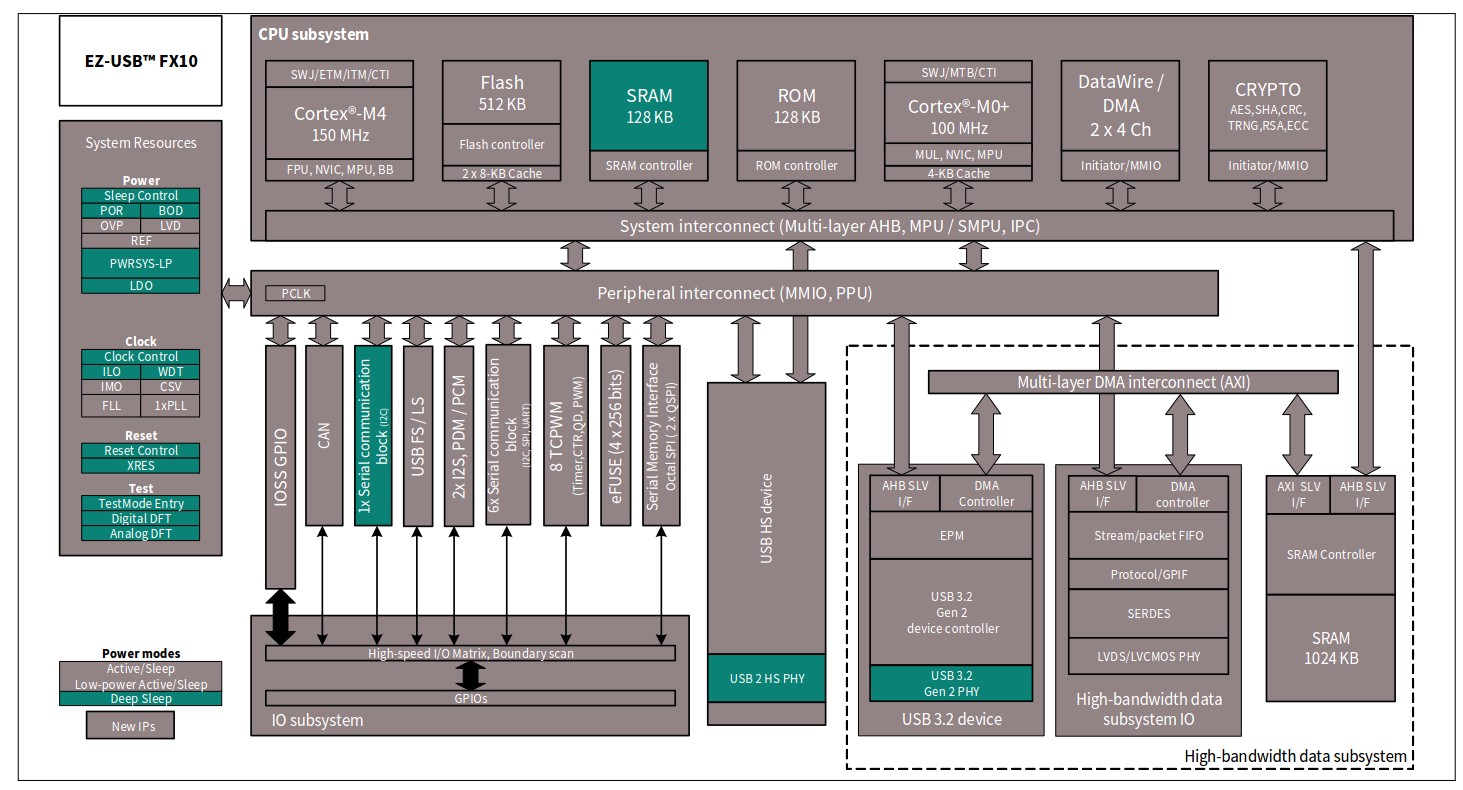

因為拿到的是FX10系列的器件,那么介紹就以CYUSB4014為例。(有消息人士傳FX5/10/20都是基于同一個Die,熊貓君這里沒有得到官方信息,不予置評)。

(1)支持USB3.2Gen2,兼容10/5GBps和480Mbps PHY;支持USB Type-C,最高32個USB Endpoint;

(2)SoC內置1個150MHz的Cortex-M4F核和1個100MHz的M0+核;

(3)內部存儲資源如下:

a)512KB的應用程序Flash空間,用于存儲用戶應用程序;

b)128KB SRAM,可以配置為4個32KB區域,在在Deep Sleep模式下,這些區域能夠配置為Retain Data模式;

c)128KB ROM,內置ROM Boot啟動代碼,包含設備初始化、寫Flash、安全、eFuse編程和其他系統級的函數功能。ROM代碼由CM0+ CPU執行;

d)1MB數據緩存SRAM,用做LVSD/LVCMOS到USB的數據緩沖區;

e)1024位的OTP eFuse,其中648bit用于存儲系統的Die ID、設備ID、初始化的Trim設置、設備生命周期和安全設置等。其它區域用于存儲秘鑰、hash值、unique ID等等。在編程eFuse時,VDDD必須是2.5V。

(4)GPIF III接口

支持LVDS/SubLVDS和LVCMOS兩種類型的接口輸入:

??? a)兩組LVDS接口,每組由8對數據、1對時鐘、1對控制和7根單端LVCMOS控制信號構成,兩組可合并為16對數據的鏈路使用。最高LVDS速率為1.25Gbps/Lane(FX10是接收端時);

b)兩個port,每個port由16根數據線,1個時鐘和10根控制線構成,2個port可合并為32bit的數據總線,FX10是接收端時,可支持最高160MHz的DDR/SDR數據,是發送端時,最高100MHz。

(5)外設

支持最高48個GPIO:可用作QSPI,7個可配置的I2C、UART或SPI接口,2通道音頻接口(I2S或PDM轉PCM),一個全速USB2.0 FS用于VCOM通信,8個PWM輸出和1個CAN FD接口。

(6)時鐘資源

內置了8MHz振蕩器,32KHz振蕩器,可接入24MHz的外部晶振;內置PLL和FLL,多個時鐘分頻器。

(7)加密與安全

支持“Secure Boot”,僅允許可執行(execute-only)的代碼安全模式,秘鑰和TRNG功能。

(8)封裝:BGA-169 Ball,10×10mm,0.75mm球間距。

下圖是FX10的體系架構框圖。

圖1 FX10架構框圖

二、硬件設計

硬件設計主要考慮供電、啟動和接口,PCB Layout時重點考慮信號完整性。本例中將FX10的輸入接口設計為LVDS以減少IO使用量。

(1)供電設計

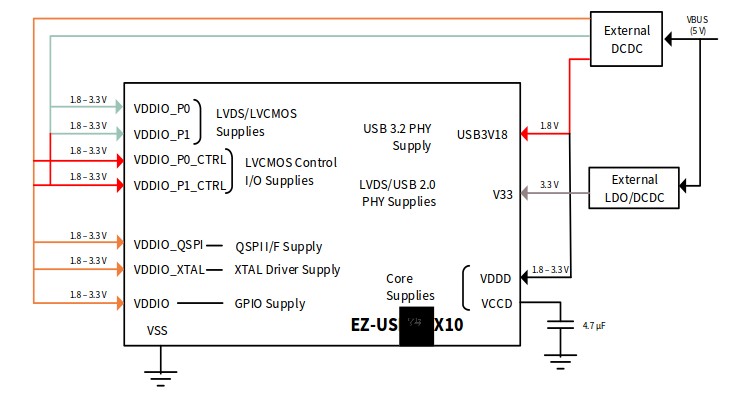

如下圖2所示是FX10的供電系統:

圖2 FX10供電系統

設計電源系統的兩大要點:其一是必須滿足功能性能要求,其二是將系統功耗降到最低。將系統功耗降低有兩層考慮,一層是使用效率高的電源芯片,第二層就是使FX10工作在最佳最省電的狀態。從數據手冊上可以看到,在內核電壓VDDD工作在1.8V使,能效比最高,因此,各路電軌可設計如下:

a)VDDD:內核供電,設計為1.8V。但需要注意的是,在編程efuse時,需要配置為2.5V;

b) VCCD:FX10內部轉換器,將VDDD變為1.1V電壓,外接退耦電容即可;

c)VDDIO_X:給外設IO供電,全部設計為1.8V;

d)USB3V18:給USB3.2物理層供電,1.8V;

e)V33:給USB2 HS PHY供電,3.3V;

f)VDDIO_P0/1:LVDS/LVCMOS接口模塊,因為選擇的是LVDS接口,該處必須使用3.3V供電;

g)VDDIO_Px_CTRL:單端控制信號供電,選擇1.8V。

由上可知:需要3.3V、2.5V和1.8V三組供電,如無需使用efuse功能或3.3V為可在線編程電源,則只需3.3V和1.8V兩組供電即可。

(2)啟動模式

BOOT模式通過GPIO PMODE_13.0選擇,該IO低電平時從內部Flash啟動,高電平時從USB啟動。

(3)Layout設計

FX10器件Layout設計請參見官方文檔AN238422《EZ-USB FX5/FX10 hardware design Guidelines and schematic checklist》。

三、開發環境

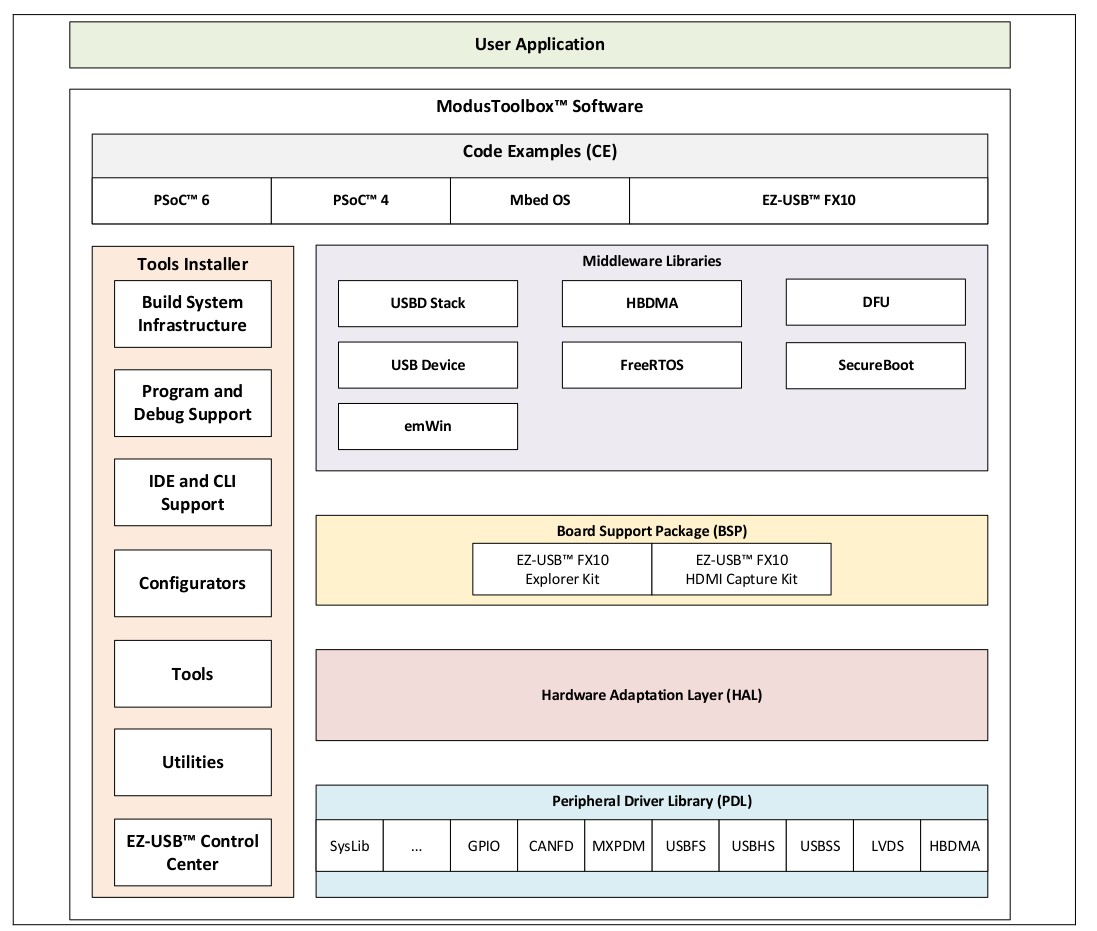

(1)開發環境和編譯器

FX10 SoC端開發環境使用Modus ToolBox交叉環境+Visual Studio Code IDE(或IAR、ARM MDK等)編譯器實現。官方提供的SDK基于FreeRTOS(當前基于內核版本version 10.4.6),SDK提供外設驅動庫、LVDS IP驅動、USB協議棧和DMA管理等等。

官方提供了若干個例程,包括UAC、UVC、USB3 Vision等音視頻流協議,使用LVCMOS接口的Slave FIFO協議等。用戶可以基于例程修改開發自己的應用。需要特別注意的是Slave FIFO例程僅支持LVCMOS接口輸入。

根據所選的編譯器IDE,可以支持GUN、ARMCC或IAR。建議用戶選擇自己熟悉的IDE和編譯工具鏈。官方給的例程是基于Modus ToolBox 3.1.0及以上版本+Visual Studio Code IDE+OpenOCD KitProg3調試。

下圖3是Modus ToolBox支持EZ-USB FX10開發框架。

圖3 ModusToolbox For EZ-USB FX10

(2)在線調試

在線調試支持SWD接口和JTAG接口。FX10支持OpenOCD和GDB調試協議,對應的調試器分別是KitProg3和Segger J-Link。所有的官方開發套件都搭載KitProg3調試器,這個調試器原廠的1千多,第三方貳佰來塊。對國內用戶而言,似乎更加熟悉J-LINK。

(3)計算機端

與上一代的CyUSB3014類似,提供了一個EZ-USB Control Center實現一些基本的功能,如編程、查看設備信息。UVC、U3V等協議可以直接使用第三方工具播放,Slave FIFO也是老辦法,自己寫客戶端軟件接收數據和解析、保存、播放。

好了,今天算是起了個頭。對FX10的器件特點、硬件設計和開發調試環境的搭建做了一個簡要介紹。下一期是修改、編譯和調試SDK軟件的內容。各位晚安。Good Night。

:廣播消息)

)

)

與入侵防御系統(IPS):功能對比與部署實踐)

![P12167 [藍橋杯 2025 省 C/Python A] 倒水](http://pic.xiahunao.cn/P12167 [藍橋杯 2025 省 C/Python A] 倒水)

和IPv6(互聯網協議版本6))

)