????????由于FPGA需要被反復燒寫,它實現組合邏輯的基本結構不可能像ASIC 那樣通過固定的與非門來完成,而只能采用一種易于反復配置的結構。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM 工藝的查找表結構。LUT本質上就是一個RAM。它把數據事先寫入 RAM后,每當輸入一個信號就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出。

7系列FPGA中的函數發生器實現為六輸入查找表(LUT)。slice的4個函數發生器(A,B,C和D)中的每一個都有六個獨立輸入(A輸入A1至A6)和兩個獨立輸出(O5和 06)。這篇短文中,我們通過一個簡單的加法器來了解下LUT 如果實現加法器功能。

module ADDER(

input [0:0]A,

input [0:0]B,

output [1:0]Q

):

? ? ? ? assign Q=A+B;endmodul?

其原理圖如下:

?

經過綜合后如下:

?

?

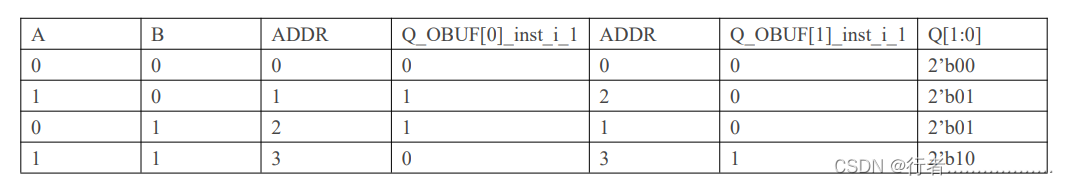

A:LUT2初值位4'h6二進制表示位3’b110;B:LUT2初值位4'h8二進制表示位4'b1000?

通過以上的簡單舉例,可以看到LUT實現邏輯單元功能的本質了。

通過以上的簡單舉例,可以看到LUT實現邏輯單元功能的本質了。

效果 粒子、線條和拖尾)

)