GPIO(General Purpose Input Output)可用于執行數字輸入或輸出功能。典型的應用包括從/向模擬或數字傳感器/設備讀寫數值、驅動LED、為I2C通信驅動時鐘、生成外部組件的觸發、發出中斷等。

文章目錄

- 1 GPIO簡介

- 2 輸出模式

- 2.1 推挽輸出

- 2.2 開漏輸出

- 3 輸入模式

- 3.1 高阻態(浮空)、上拉、下拉

- 3.2 施密特觸發輸入

1 GPIO簡介

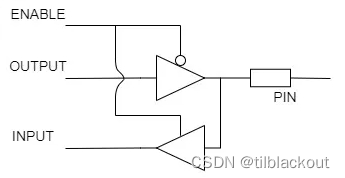

一個GPIO引腳主要有兩個緩沖區,即輸入和輸出。

輸入和輸出由使能引腳ENABLE控制:

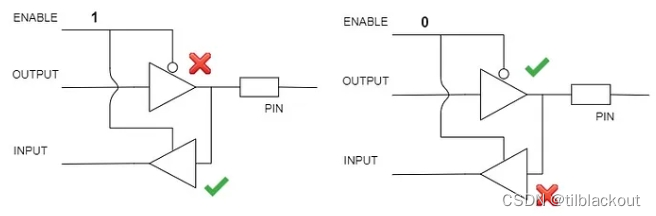

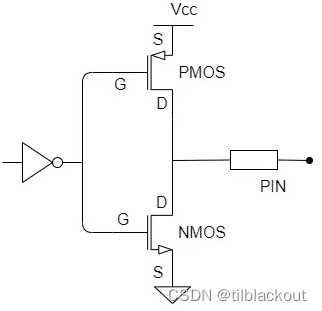

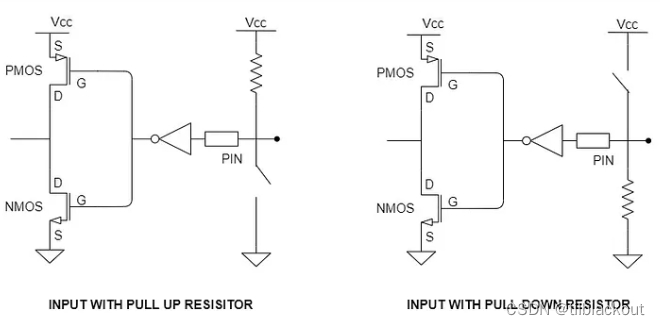

每個輸入/輸出緩沖區都有一個PMOS和NMOS晶體管以及一個非門。這兩個晶體管的柵極和漏極連接在一起,如下圖所示:

2 輸出模式

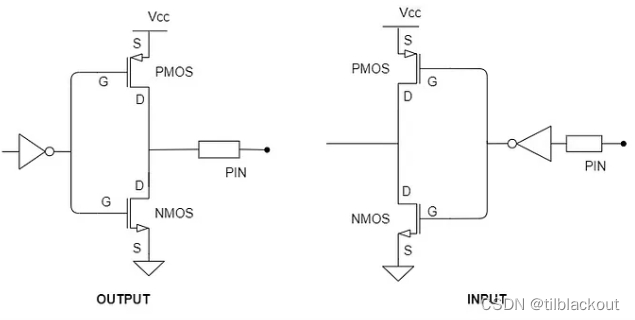

如果將邏輯高電平輸出到引腳,則PMOS打開,NMOS關閉,從而將VCC連接到輸出引腳。這個階段被稱為推相位,因為它類似于推動電流。如果輸出邏輯低電平到引腳,則NMOS打開,PMOS關閉,從而將輸出引腳連接到地,由于它看起來像是在拉電流,因此被稱為拉相位。

2.1 推挽輸出

推挽模式是GPIO輸出模式的默認狀態。引腳可以使用PMOS晶體管或NMOS晶體管將信號“推”高或者“拉”低。

流入緩沖區地端的電流被稱為灌電流(Current Sinking),相反地,從緩沖區產生的電流被稱為拉電流(Current Sourcing)。拉電流始終通過PNP或PMOS晶體管完成,而灌電流通過NPN或NMOS晶體管完成。

由于PMOS(PNP)晶體管通常具有較高的電流驅動能力,即拉電流時所需的電流較大。因此一個GPIO引腳就可以驅動多個GPIO引腳。

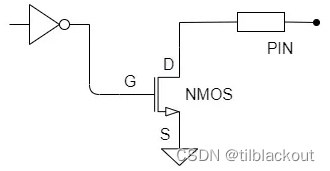

2.2 開漏輸出

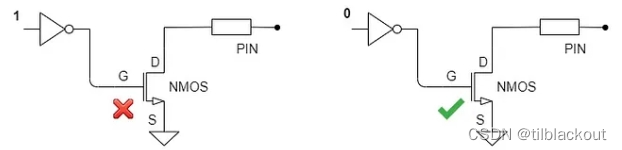

在這種配置中,沒有PMOS晶體管,而NMOS晶體管的漏極保持在浮空狀態。因此這種配置被稱為開漏。

當輸出邏輯低電平時,NMOS將打開并接地。輸出高電平時,NMOS不會打開,引腳處于浮動狀態。

換句話說,這種模式僅支持灌電流。為了避免這種浮動狀態,我們可以在NMOS的漏極接一個上拉電阻。

何時使用推挽和開漏?

- 推挽用于不需要在同一組引腳上同時傳輸和接收數據的協議,如UART、SPI

- 開漏可用于執行雙向通信的引腳,如I2C協議

3 輸入模式

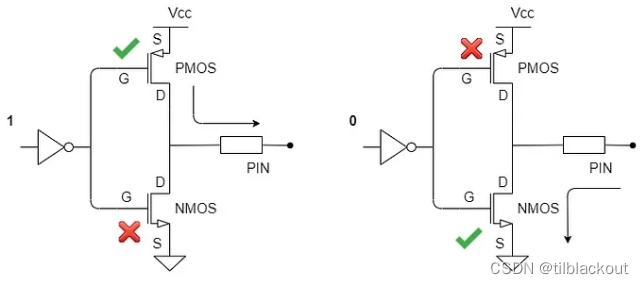

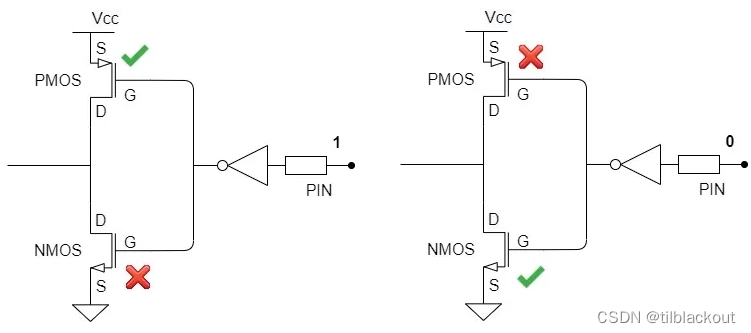

如果引腳處于邏輯高電平輸入狀態,那么PMOS晶體管將打開,NMOS晶體管關閉,從而將Vcc連接到GPIO。 反之GPIO連接到地。

3.1 高阻態(浮空)、上拉、下拉

高阻態就是引腳既沒有上拉也沒有下拉,而是保持漂浮狀態。在沒有外部驅動的情況下,該狀態是不確定的。

默認情況下,在上電后GPIO引腳處于高阻態輸入模式。浮動引腳極易受到噪聲干擾,可能會導致兩個晶體管導通并提供直接路徑從VCC到GND的漏電流。我們絕對不應將引腳保持在浮動狀態,因為漏電流將導致高功耗,在最壞的情況下還可能導致芯片復位。 為了避免這種情況,可以配置上拉電阻或下拉電阻。

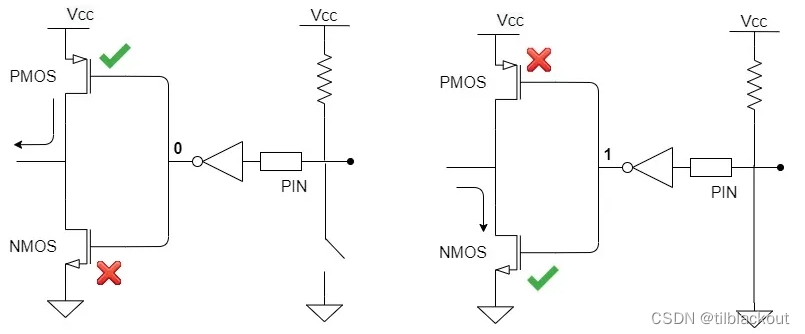

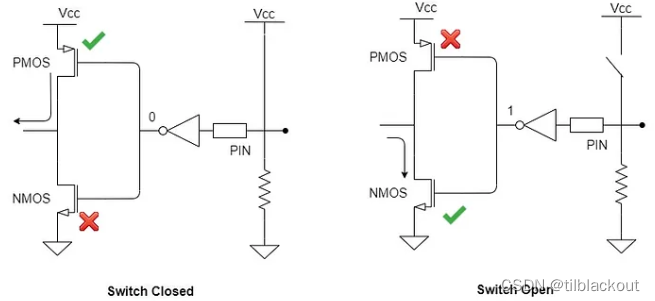

在GPIO配置為上拉時,下面的開關打開,則PMOS導通;下面的開關閉合,則NMOS導通。

反之,GPIO配置為下拉時,上面的開關閉合,則PMOS導通;上面的開關打開,則NMOS導通。

3.2 施密特觸發輸入

這種輸入類型與我們之前討論的常規輸入緩沖區不同,它連接到一個施密特觸發器。在輸入信號接近閾值時,由于噪聲或其他不穩定性因素,輸入信號可能會在上升和下降閾值之間擺動。這可能導致觸發器在閾值之間多次切換,產生不確定的輸出狀態。所以為了確保可靠性,需要添加上拉或下拉電阻來明確信號的狀態。

什么是施密特觸發器?

施密特觸發器是一種電壓比較器,只有在輸入電壓超過上閾值時才會啟動,一旦啟動,它只有在輸入電壓低于下閾值時才會關閉。施密特觸發器表現出的這種特性被稱為滯回(hysteresis)。

下面為普通輸入緩沖區和帶有施密特觸發器的輸入緩沖區在處理嘈雜信號時的輸出比較:

可以看出,普通輸入緩沖區的輸出隨噪聲而波動。而施密特觸發器抑制了很多噪聲并提供了穩定的輸出。因此,在嘈雜的環境中,使用施密特觸發器輸入是很有用的。

)

)

)

)

)