一、eMMC 技術深度解析

1.定義與背景

eMMC(Embedded Multi Media Card)是一種專為嵌入式系統設計的非易失性存儲解決方案,它將 NAND 閃存、主控芯片和接口協議封裝在一個 BGA(Ball Grid Array)封裝中。其核心目標是簡化系統設計、提升數據傳輸效率、降低功耗,并滿足移動設備對存儲容量和性能的不斷增長需求。eMMC 由 JEDEC(固態技術協會)制定標準,目前最新版本為 eMMC 5.1,傳輸速率可達 400MB/s,廣泛應用于智能手機、平板電腦、工控系統、電力儲能、車載系統、物聯網設備等場景。

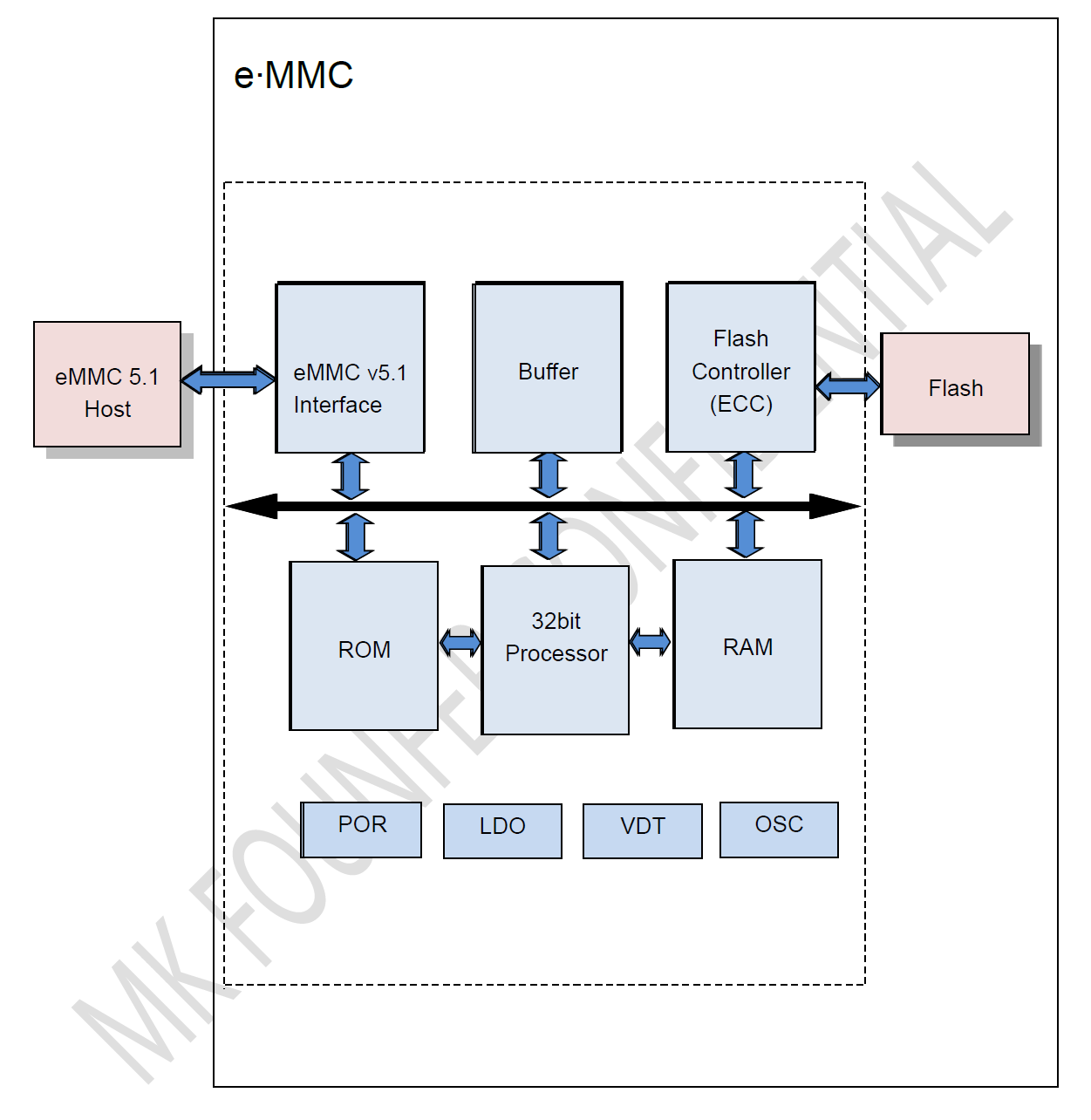

2.MK-米客方德內部架構與工作原理

(1)核心組件

- NAND 閃存陣列:存儲數據核心,采用 pSLC/SLC/MLC/TLC 等制程,提供不同容量與性能選擇。

- 主控芯片:管理閃存讀寫、壞塊管理、磨損均衡(ECC 糾錯、GC 垃圾回收)、協議轉換(將外部命令轉換為閃存操作指令)。

- 接口邏輯:兼容 MMC/SD 協議,支持 HS400、HS200 等高速模式,通過并行數據線(DAT0~DAT7)實現數據并行傳輸。

(2)關鍵技術

- 壞塊管理:出廠時通過掃描標記不可用塊,運行時動態監測新增壞塊并更新映射表,確保數據不寫入失效區域,通過映射表記錄壞塊位置,避免數據寫入失效區域,延長閃存壽命。

- 磨損均衡算法:分為動態均衡(如基于空閑塊選擇)和靜態均衡(如數據遷移),通過算法優化延長閃存整體壽命避免特定區塊頻繁擦寫導致壽命提前耗盡。

- ECC 糾錯機制:采用 BCH/LDPC 算法,自動糾正數據讀寫過程中的比特錯誤。

- BCH:適用于 SLC/MLC,糾錯能力強但開銷高。

- LDPC:適用于 TLC/QLC,糾錯效率更高,支持更大容量糾錯碼。

數據讀寫流程:

- 主機發送讀寫命令至 eMMC 主控。

- 主控解析命令并執行地址映射,將邏輯地址轉換為物理地址。

- 通過 ECC 生成校驗碼,并寫入/讀取閃存數據。

- 返回數據及狀態信息至主機。

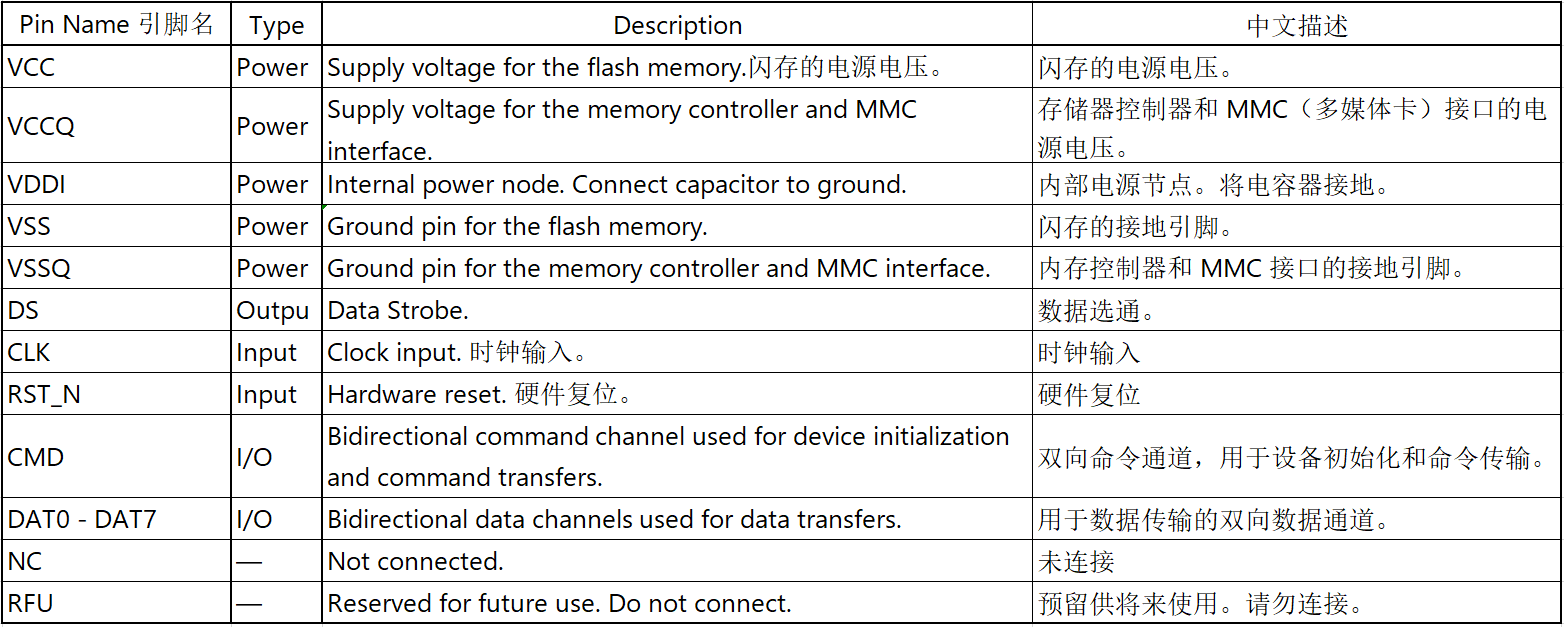

(3)通信協議-引腳介紹

米客方德 eMMC 采用基于命令/響應的異步通信機制,通過以下信號線實現數據傳輸:

- CLK:時鐘信號,決定數據傳輸速率(最高支持 200MHz)。

- CMD:命令信號線,用于發送指令(如讀/寫、初始化、配置等)。

- DAT[0:7]:數據信號線,支持并行傳輸,提升帶寬。

- RST_N:復位信號,低電平有效。

eMMC 框圖

3.eMMC 版本演進與性能對比

| 版本 | 發布年份 | 最大速率 | 關鍵特性 |

|---|---|---|---|

| eMMC 4.3 | 2009 | 52MB/s | 支持 HS200 模式,滿足早期移動設備需求。 |

| eMMC 4.5 | 2011 | 200MB/s | 引入 HS400 高速模式,支持 LPDDR 接口。 |

| eMMC 5.0 | 2013 | 400MB/s | 增強功耗管理,支持硬件加密(eMMC Security)。 |

| eMMC 5.1 | 2016 | 400MB/s | 優化隨機讀寫性能,提升溫度適應性。 |

二、MK-米客方德 eMMC 硬件電路設計詳解

(一)電路設計基礎

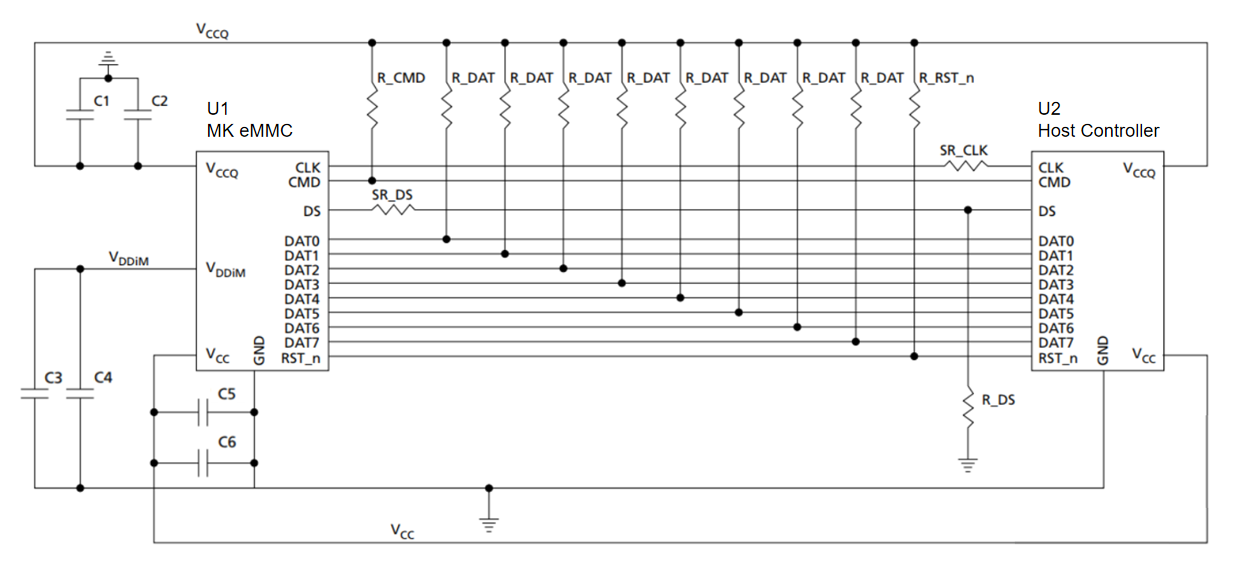

1.典型應用電路

eMMC 電路設計需關注電源、信號連接及保護,以下為典型電路示意:

eMMC 典型應用電路示意圖,包含 VCC、VCCQ、VDDi、CLK、CMD、D[0:7]、RST_N 等信號,標注濾波電容、上拉電阻等。

2.電源設計

-

VCC(供電電源):通常為 3.3V 或 1.8V,需通過 LC 濾波電路(如 10uF+0.1uF 電容并聯)抑制高頻噪聲。

-

VCCQ(IO 電源):與 VCC 相同或獨立,需確保電平匹配以避免邏輯沖突。

-

VDDi(內部核心電源):用于主控芯片供電,需單獨濾波(如 2.2uF 電容),并避免與 IO 電源共線。

3.? 信號線處理

-

CLK 信號:需 50Ω 阻抗匹配,避免反射導致時序錯誤。

-

數據線(D0~D7):采用并行傳輸,需等長布線(誤差<50mil),并預留上拉電阻(10KΩ)以增強信號驅動能力。

-

CMD 信號:需上拉至 VCCQ,確保空閑狀態為高電平。

(二)關鍵設計要素

1.濾波與去耦電容布局

- 電源引腳附近放置多個不同容值電容(0.1uF~10uF),形成“金字塔”濾波結構,吸收不同頻段噪聲。

- VCC 與 VCCQ 通過 0Ω 電阻隔離,確保電平一致性。

- 電容盡量靠近芯片引腳,縮短走線長度,減少寄生電感。

- 采用 PMIC(電源管理芯片)為 eMMC 提供獨立 3.3V 供電,減少系統電源干擾。

2.PCB 布線規則

- 分層設計:推薦使用 4 層及以上 PCB,信號層與地層相鄰,降低信號輻射。

- 信號隔離:eMMC 信號與其他高速信號(如 USB、射頻)保持間距(≥3W),數據線組間添加地線隔離,避免串擾。

- CLK 走線:采用蛇形走線補償長度差異,確保與數據線同步到達。

- 熱設計考慮:eMMC 芯片下方鋪銅散熱,通過過孔連接至地層,增強散熱效率。

- 地平面分割:若存在多個電源域,需在分割區通過 0Ω 電阻或磁珠連接,確保信號回流路徑最短。

3.ESD 與浪涌保護

- 信號線可添加 TVS 二極管或 ESD 保護芯片,防止靜電或瞬態高壓損壞接口。

- RST_N 信號線需串聯限流電阻(如 1KΩ)并上拉,避免誤觸發復位。

三、eMMC 性能優化與調試

1.時序參數優化

- CLK 頻率與數據建立/保持時間:根據 eMMC 規格調整 CLK 頻率,確保數據在窗口期內穩定傳輸。

- 信號延遲匹配:通過仿真工具(如 HyperLynx)驗證 CLK 與數據線延遲差,調整 PCB 布線長度。

2.功耗管理

- 利用 eMMC 的 Deep Power Down 模式(DPD)降低待機功耗,通過軟件控制進入/退出 DPD 狀態。

- 動態調整讀寫電壓(如 1.8V→1.2V),平衡性能與功耗。

3.調試工具與測試方法

- 使用示波器抓取 CLK、數據波形,分析時序違規問題。

- 通過壓力測試(如連續讀寫、高溫老化)驗證 eMMC 可靠性。

)

和 部署方式(--deploy-mode))