0.簡介

通用異步收發器(Universal Asynchronous Receiver/Transmitter,UART)可以和各種標準串行接口,如RS 232和RS 485等進行全雙工異步通信,具有傳輸距離遠、成本低、可靠性高等優點。一般UART由專用芯片如8250,16450來實現,但專用芯片引腳都較多,內含許多輔助功能,在實際使用時往往只需要用到UART的基本功能,使用專用芯片會造成資源浪費和成本提高。

一般而言UART和外界通信只需要兩條信號線RXD和TXD,其中RXD是UART的接收端,TXD是UART的發送端,接收與發送是全雙工形式。由于可編程邏輯器件技術的快速發展,FPGA的功能日益強大,其開發周期短、可重復編程的優點也越來越明顯,在FPGA芯片上集成UART功能模塊并和其他模塊組合可以很方便地實現一個能與其他設備進行串行通信的片上系統。

FPGA(Field Programmable Gate Array)現場可編程門陣列在數字電路的設計中已經被廣泛使用。這種設計方式可以將以前需要多塊集成芯片的電路設計到一塊大模塊可編程邏輯器件中,大大減少了電路板的尺寸,增強了系統的可靠性和設計的靈活性。[1]

1. Uart時序

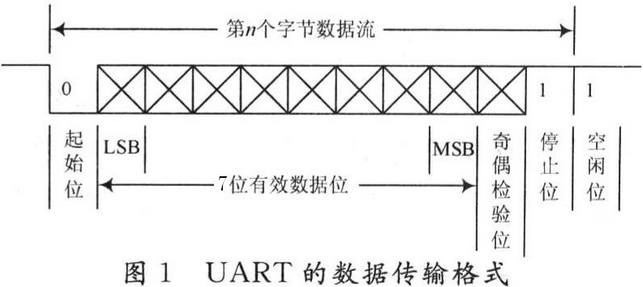

UART的一幀由四部分組成起始位(1bit),數據位(6\7\8bit),奇偶校驗位(1bit),停止位(1\1.5\2bit)?

uart 是將傳輸數據的每個字符一位接一位地傳輸。 其中每一位(Bit)的意義如下:

空閑位:高電平,表明當前無傳輸事務。

起始位:一位低電平信號,標志著數據傳輸的開始。

數據位:緊接著起始位之后。數據位的個數可以是 6、7、8 等,構 成一個字符。通常采用 ASCII 碼。從最低位開始傳送,依靠時鐘定位。

奇偶校驗位:數據位加上這一位后,使得“1”的位數應為偶數(偶校驗)或 奇數(奇校驗),以此來校驗數據傳送的正確性。

停止位:一個字符數據的結束標志。可以是 1 位、1.5 位、2 位的高電平。

由于數據是在傳輸線上定時的,并且每一個設備有其自己的時鐘,很可能在通 信中兩臺設備間出現了小小的不同步。因此停止位不僅僅是表示傳輸的結束, 并且提供計算機校正時鐘同步的機會。停止位的位數越多,不同時鐘同步的容 忍程度越大,但是數據傳輸率同時也越慢。[2]

1.1 通信協議

UART(Universal Asynchronous Receiver/Transmitter),通用異步收發器,是一種異步全雙工串行通信協議,可實現單工通信、半雙工通信和全雙工通信。

單工通信方式:主機只能發送數據,從機只能接收數據,數據流向始終由發送端流向接收端;

半雙工通信方式:同一時刻,只能由主機向從機或從機向主機發送數據;

全雙工通信方式:同一時刻,主機和從機都可以互發數據。

想實現奇偶校驗功能的朋友,可以參考下面的代碼[4]:

test

用以確定奇偶校驗,其中0為無校驗位,1為偶校驗,2為奇校驗

case(test)2'b00 : test_reg <= 1'b0;2'b01 : test_reg <= !(^rx_out_reg);2'b10 : test_reg <= (^rx_out_reg);default : test_reg <= 1'b0;endcase

- 1、無校驗(no parity)。

- 2、奇校驗(odd parity):如果數據位中“1”的數目是偶數,則校驗位為“1”,如果“1”的數目是奇數,校驗位為“0”。

- 3、偶校驗(even parity):如果數據為中“1”的數目是偶數,則校驗位為“0”,如果為奇數,校驗位為“1”。[5]

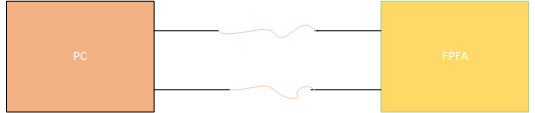

2. 串口的物理層

UART通信只有兩根信號線,一根是發送數據端口線叫tx(Transmitter),一根是接收數據端口線叫rx(Receiver),如圖所示,對于PC來說它的tx要和對于FPGA來說的rx連接,同樣PC的rx要和FPGA的tx連接,如果是兩個tx或者兩個rx連接那數據就不能正常被發送出去和接收到[6]。

3 Top層代碼實現:

`timescale 1ns / 1psmodule my_uart_top(clk,rst_n,rs232_rx,rs232_tx);input clk ; // 50MHz主時鐘

input rst_n ; // 低電平復位信號input rs232_rx ; // RS232接收數據信號

output rs232_tx ; // RS232發送數據信號wire bps_start1,bps_start2; // 接收到數據后,波特率時鐘啟動信號置位,高電平有效

wire clk_bps1,clk_bps2; // clk_bps_r高電平為接收數據位的中間采樣點,同時也作為發送數據的數據改變點

wire[7:0] rx_data; // 接收數據寄存器,保存直至下一個數據來到

wire rx_int; // 接收數據中斷信號,接收到數據期間始終為高電平speed_select speed_rx( .clk(clk), //波特率選擇模塊.rst_n(rst_n),.bps_start(bps_start1),.clk_bps(clk_bps1));my_uart_rx my_uart_rx( .clk(clk), //接收數據模塊.rst_n(rst_n),.rs232_rx(rs232_rx),.rx_data(rx_data),.rx_int(rx_int),.clk_bps(clk_bps1),.bps_start(bps_start1));///

speed_select speed_tx( .clk(clk), //波特率選擇模塊.rst_n(rst_n),.bps_start(bps_start2),.clk_bps(clk_bps2));my_uart_tx my_uart_tx( .clk(clk), //發送數據模塊.rst_n(rst_n),.rx_data(rx_data),.rx_int(rx_int),.rs232_tx(rs232_tx),.clk_bps(clk_bps2),.bps_start(bps_start2));endmodule

?speed_select代碼

`timescale 1ns / 1psmodule speed_select(clk,rst_n,bps_start,clk_bps);input clk ; // 50MHz主時鐘

input rst_n ; //低電平復位信號

input bps_start ; //接收到數據后,波特率時鐘啟動信號置位

output clk_bps ; // clk_bps的高電平為接收或者發送數據位的中間采樣點 /*

parameter bps9600 = 5207, //波特率為9600bpsbps19200 = 2603, //波特率為19200bpsbps38400 = 1301, //波特率為38400bpsbps57600 = 867, //波特率為57600bpsbps115200 = 433; //波特率為115200bpsparameter bps9600_2 = 2603,bps19200_2 = 1301,bps38400_2 = 650,bps57600_2 = 433,bps115200_2 = 216;

*///以下波特率分頻計數值可參照上面的參數進行更改

`define BPS_PARA 5207 //波特率為9600時的分頻計數值

`define BPS_PARA_2 2603 //波特率為9600時的分頻計數值的一半,用于數據采樣reg[12:0] cnt ; //分頻計數

reg clk_bps_r ; //波特率時鐘寄存器//----------------------------------------------------------

//reg[2:0] uart_ctrl ; // uart波特率選擇寄存器

//----------------------------------------------------------always @ (posedge clk or negedge rst_n)if(!rst_n) cnt <= 13'd0;else if((cnt == `BPS_PARA) || !bps_start) cnt <= 13'd0; //波特率計數清零,bps_start信號來自uart_rx模塊的輸出else cnt <= cnt+1'b1; //波特率時鐘計數啟動always @ (posedge clk or negedge rst_n)if(!rst_n) clk_bps_r <= 1'b0;else if(cnt == `BPS_PARA_2) clk_bps_r <= 1'b1; // clk_bps_r高電平為接收數據位的中間采樣點,同時也作為發送數據的數據改變點else clk_bps_r <= 1'b0;assign clk_bps = clk_bps_r;endmodule?my_uart_rx代碼

`timescale 1ns / 1psmodule my_uart_rx(clk,rst_n,rs232_rx,rx_data,rx_int,clk_bps,bps_start);input clk ; // 50MHz主時鐘

input rst_n ; // 低電平復位信號

input rs232_rx ; // RS232接收數據信號,可以是仿真輸入激勵產生

input clk_bps ; // clk_bps的高電平為接收或者發送數據位的中間采樣點

output bps_start ; // 接收到數據后,波特率時鐘啟動信號置位

output[7:0] rx_data ; // 接收數據寄存器,保存直至下一個數據來到

output rx_int ; // 接收數據中斷信號,接收到數據期間始終為高電平//----------------------------------------------------------------

reg rs232_rx0,rs232_rx1,rs232_rx2,rs232_rx3 ; //接收數據寄存器,濾波用

wire neg_rs232_rx ; //表示數據線接收到下降沿always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrs232_rx0 <= 1'b0;rs232_rx1 <= 1'b0;rs232_rx2 <= 1'b0;rs232_rx3 <= 1'b0;endelse beginrs232_rx0 <= rs232_rx;rs232_rx1 <= rs232_rx0;rs232_rx2 <= rs232_rx1;rs232_rx3 <= rs232_rx2;end

end

//下面的下降沿檢測可以濾掉<20ns-40ns的毛刺(包括高脈沖和低脈沖毛刺),

//這里就是用資源換穩定(前提是我們對時間要求不是那么苛刻,因為輸入信號打了3拍)

//(當然我們的有效低脈沖信號肯定是遠遠大于40ns的)

assign neg_rs232_rx = rs232_rx3 & rs232_rx2 & ~rs232_rx1 & ~rs232_rx0; //接收到下降沿后neg_rs232_rx置高一個時鐘周期//----------------------------------------------------------------

reg bps_start_r ;

reg[3:0] num ; //移位次數

reg rx_int ; //接收數據中斷信號,接收到數據期間始終為高電平always @ (posedge clk or negedge rst_n)if(!rst_n) beginbps_start_r <= 1'bz;rx_int <= 1'b0;endelse if(neg_rs232_rx) begin //接收到串口接收線rs232_rx的下降沿標志信號,起始位信號拉低bps_start_r <= 1'b1; //啟動串口準備數據接收rx_int <= 1'b1; //接收數據中斷信號使能endelse if(num==4'd12) begin //接收完有用數據信息,1bit start +8bit數據 + 沒有奇偶檢驗 +2bit停止位=11, 12是空閑位bps_start_r <= 1'b0; //數據接收完畢,釋放波特率啟動信號rx_int <= 1'b0; //接收數據中斷信號關閉endassign bps_start = bps_start_r;//----------------------------------------------------------------

reg[7:0] rx_data_r; //串口接收數據寄存器,保存直至下一個數據來到

//----------------------------------------------------------------reg[7:0] rx_temp_data; //當前接收數據寄存器always @ (posedge clk or negedge rst_n)if(!rst_n) beginrx_temp_data <= 8'd0;num <= 4'd0;rx_data_r <= 8'd0;endelse if(rx_int) begin //接收數據處理if(clk_bps) begin //讀取并保存數據,接收數據為一個起始位,8bit數據,1或2個結束位 num <= num+1'b1; // 跳過第一個num,起始位case (num) // 然后是8bit的數據,先發送低bit數據,再發送高bit數據4'd1: rx_temp_data[0] <= rs232_rx; //鎖存第0bit4'd2: rx_temp_data[1] <= rs232_rx; //鎖存第1bit4'd3: rx_temp_data[2] <= rs232_rx; //鎖存第2bit4'd4: rx_temp_data[3] <= rs232_rx; //鎖存第3bit4'd5: rx_temp_data[4] <= rs232_rx; //鎖存第4bit4'd6: rx_temp_data[5] <= rs232_rx; //鎖存第5bit4'd7: rx_temp_data[6] <= rs232_rx; //鎖存第6bit4'd8: rx_temp_data[7] <= rs232_rx; //鎖存第7bitdefault: ; // 不用careendcaseendelse if(num == 4'd12) begin //我們的標準接收模式下只有1+8+1(2)=11bit的有效數據num <= 4'd0; //TQ老師說接收到STOP位后結束,num清零,FIXME:這里的代碼有歧義rx_data_r <= rx_temp_data; //把數據鎖存到數據寄存器rx_data中endendassign rx_data = rx_data_r; endmodule

uart_tx代碼

`timescale 1ns / 1psmodule my_uart_tx(clk,rst_n,rx_data,rx_int,rs232_tx,clk_bps,bps_start);input clk; // 50MHz主時鐘

input rst_n; // 低電平復位信號

input clk_bps; // clk_bps_r高電平為接收數據位的中間采樣點,同時也作為發送數據的數據改變點

input [7:0] rx_data; //接收數據寄存器

input rx_int; //接收數據中斷信號,接收到數據期間始終為高電平,在該模塊中利用它的下降沿來啟動串口發送數據

output rs232_tx; // RS232發送數據信號

output bps_start; //接收或者要發送數據,波特率時鐘啟動信號置位//---------------------------------------------------------

reg rx_int0,rx_int1,rx_int2; //rx_int信號寄存器,捕捉下降沿濾波用

wire neg_rx_int; // rx_int下降沿標志位always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginrx_int0 <= 1'b0;rx_int1 <= 1'b0;rx_int2 <= 1'b0;endelse beginrx_int0 <= rx_int;rx_int1 <= rx_int0;rx_int2 <= rx_int1;end

endassign neg_rx_int = ~rx_int1 & rx_int2; //捕捉到下降沿后,neg_rx_int拉高保持一個主時鐘周期//---------------------------------------------------------

reg[7:0] tx_data; //待發送數據的寄存器

//---------------------------------------------------------

reg bps_start_r;

reg tx_en; //發送數據使能信號,高有效

reg[3:0] num;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginbps_start_r <= 1'bz;tx_en <= 1'b0;tx_data <= 8'd0;endelse if(neg_rx_int) begin //接收數據完畢,準備把接收到的數據發回去bps_start_r <= 1'b1 ;tx_data <= rx_data ; //把接收到的數據存入發送數據寄存器tx_en <= 1'b1 ; //進入發送數據狀態中endelse if(num==4'd11) begin //數據發送完成,復位bps_start_r <= 1'b0;tx_en <= 1'b0;end

endassign bps_start = bps_start_r;//---------------------------------------------------------

reg rs232_tx_r;always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginnum <= 4'd0;rs232_tx_r <= 1'b1;endelse if(tx_en) beginif(clk_bps) beginnum <= num+1'b1;case (num)4'd0: rs232_tx_r <= 1'b0; //發送起始位4'd1: rs232_tx_r <= tx_data[0]; //發送bit04'd2: rs232_tx_r <= tx_data[1]; //發送bit14'd3: rs232_tx_r <= tx_data[2]; //發送bit24'd4: rs232_tx_r <= tx_data[3]; //發送bit34'd5: rs232_tx_r <= tx_data[4]; //發送bit44'd6: rs232_tx_r <= tx_data[5]; //發送bit54'd7: rs232_tx_r <= tx_data[6]; //發送bit64'd8: rs232_tx_r <= tx_data[7]; //發送bit74'd9: rs232_tx_r <= 1'b1; //發送結束位default: rs232_tx_r <= 1'b1; //空閑位拉高endcaseendelse if(num==4'd11) num <= 4'd0; //復位end

endassign rs232_tx = rs232_tx_r;endmodule特權老師實現的代碼,比較簡單些,沒有用到奇偶校驗位,也沒有用到FIFO。功能基本上都已經實現了。

總結

人生總會起起伏伏,總有一篇文章,適合你!加油!期待明天美好的事情發生!

參考文獻:

[1]FPGA——UART Verilog程序設計_uart verilog狀態轉移圖-CSDN博客

[2]Verilog UART串口詳解(代碼及整體思路)-CSDN博客

[3]【Verilog實戰】UART通信協議,半雙工通信方式(附源碼)_uart 半雙工-CSDN博客

[4]【數字IC】從零開始的Verilog UART設計_ic數字前端verilog設計-CSDN博客

[5]【FPGA協議篇】UART通信及其verilog實現(代碼采用傳參實現模塊通用性,適用于快速開發)_fpga 串口波特率-CSDN博客

[6]FPGA實現串口(UART)_fpga uart-CSDN博客?