【 聲明:版權所有,歡迎轉載,請勿用于商業用途。 聯系信箱:feixiaoxing @163.com】

? ? ? ? zynq最大的優勢,就是把arm和fpga結合在一起了。這樣一顆soc里面,就可以用軟件去驅動外設ip,這是之前沒有過的體驗。因為以前,arm和fpga通信,大多數都是分列式設計,arm是單獨的一顆soc,fpga也是單獨的芯片,兩者通過外部總線溝通,比如pcie等等。現在有了zynq,直接借助于axi總線就能通信。但是很多小伙伴呢,還是不太明白fpga該怎么開發,以及verilog、仿真、fpga和芯片設計的關系,正好借此機會聊一下。

1、verilog

? ? ? ? verilog是一門描述語言,和它類似的還有vhdl。有了描述語言,我們就可以描述時序電路、組合邏輯電路,這兩部分都是設計的基礎。再加上輸入接口、輸出接口、時鐘、復位、狀態機,不管是硬件協議,還是算法電路,都可以去實現了。所以學好verilog的前提是數字電路,只要掌握了數字電路,就可以明白verilog的基本原理了。至于語法中的阻塞、非阻塞,以及綜合、不可綜合,這些概念遇到的時候處理一下即可。

2、仿真

? ? ? ? verilog的仿真,就類似于c語言port到嵌入式開發板子前,先用windows平臺仿真一下是一個道理。仿真不僅可以模擬出各種激勵信號,還能實現自動化測試,非常適合上板之前的功能確認。從工具層面,verilog不考慮布局布線,也不考慮功耗,只是從功能層面確認下實現是否ok。而且,仿真的效率一般非常之高,有興趣的小伙伴甚至可以自己寫一個仿真器。

? ? ? ? 從大的地方說,仿真就是按照復位信號,組合邏輯、時序邏輯、組合邏輯一步一步往前走,按照這個思路,自己就可以寫一個最簡單的仿真器。比如,我們出現這樣一個電路,

assign d = a ? b : c;? ? ? ? 如果改成c語言,基本就是這樣的組合邏輯,

int get_data(int a, int b, int c)

{if(a){return b;}else{return c;}

}int d = get_data(a,b,c);? ? ? ? 哪怕是時序邏輯,也可以處理。計算的時候,如果clock沒有到,先計算組合邏輯,然后clock來臨之后,把組合邏輯的結果賦值給寄存器,這樣就可以實現時序仿真了。

3、fpga

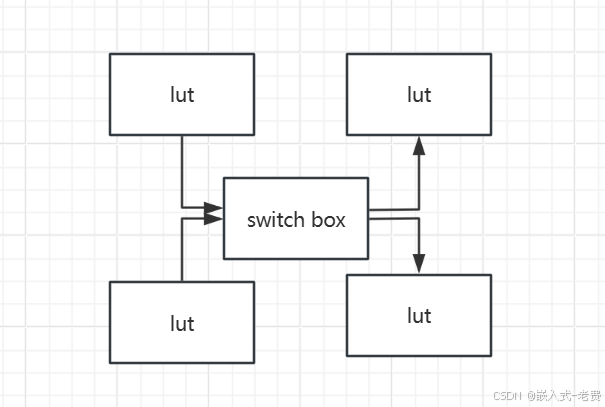

? ? ? ? fpga是介于軟件和硬件的產物。本質上fpga是由一個一個的lut查找表、開關連線、外設三部分組成。當然,除了這三部分,還是pll、rom、ram、fifo、dsp等資源。最主要的部分,還是剛才說的lut、switch box、io。

????????其中lut本質上就是查找表,它不知道什么與或非,我們需要什么功能,工具幫忙編譯成對應的lut就可以了。比如一個或門,就可以是 0 0 0/ 0 1 1/ 1 0 1/ 111。前面兩個輸入,最后一個是輸出。當然除了組合邏輯之外,lut內部一般還有d觸發器,這個用來處理時序電路。因此,我們寫的組合邏輯和時序邏輯都是由這樣一個一個lut拼起來的。

? ? ? ? 既然是拼起來的lut,那么就會涉及到模塊和模塊的互聯。比如下面這句話,

assign flag = (a|b) & (c|d);? ? ? ? 這個flag信號的處理,來自于a、b、c、d。假設lut最大只能處理兩路信號,那么這個電路就需要三個lut才能實現。第一個lut處理a和b,第二個lut處理c和d,然后兩個lut的處理結果送到第三個lut,這樣才實現了基本的flag輸出。那么lut直接按怎么通信呢,其實內部可以看成是這樣一個結構,

? ? ? ? 有了swich box之后,就可以這樣一直把信號傳遞下去。當然,換一個角度來看,switch box也是一種特殊的lut。至于輸入輸出模塊也是一樣,只不過這種輸入、輸出要涉及到fpga的引腳,本質上也是一種特殊的lut。

4、asic芯片

? ? ? ? verilog本身作為描述語言,可以描述fpga,也可以描述芯片的設計。fpga下面除了lut,還有pll、dsp、fifo、rom、ram等很多資源,所以fpga看上去更像是搭積木,fpga的工具就是把用戶的verilog的描述映射到這一個一個資源上面。雖然整體很方便,不過也容易出問題,比如布局布線,信號和信號之間會不會距離太長,需不需要加時間約束等等。所以對于fpga來說,前端設計和后端設計是一體的,后端設計是fpga廠家的工具幫助自動完成的。因此,很多芯片設計開發功能的時候,都是用fpga來做前端設計的,甚至是幾塊fpga芯片一起來仿真。

? ? ? ? 而asic設計,看上去更像是從0到1開始造房子。雖然也是用verilog開發,但是底層實現來自于代工廠的工藝庫,里面有組合邏輯、時序邏輯、rom、ram模塊等等。工藝庫就是實實在在的mos管邏輯電路,而不是fpga那種查表機制的lut了。不過,soc里面有些ip需要從第三方購買,有些ip需要自己設計,這些ip都ok之后,通過總線連接在一起之后,這才相當于完成了基本的soc邏輯設計。接下來就是后端工程師的工作。

? ? ? ? 芯片的前后端設計,非常類似于電路的前后端設計,電路的前端設計就是原理圖設計,電路的后端設計就是pcb layout。原理圖ok不見得pcb就ok。比如電源擺放是不是合理,模數有沒有分開,高頻、低頻有沒有分開,發熱有沒有提前布局,這都是pcb layout考慮的。后端芯片設計也是一樣,比如pin腳布局、時鐘樹設計、電源信號處理等等,既要有利于生產、提高良品率,也要考慮到后續客戶的使用習慣。哪怕現在很多芯片后端設計都是外包的,至少發包方要在關鍵指標上提出明確訴求,不然很容易爛尾掉,畢竟芯片流片也不便宜。

? ? ? ? fpga本身依賴于查表和ram機制,這是它自身的可編程性決定的,也是fpga得以存在的基礎。因此不管是功耗上,還是頻率上,都不如asic。但是fpga勝在一個靈活,因此只有量大的場景才會asic化,如果是非標類的應用,一般用fpga就可以了,尤其是圖像和通信類領域。

詳解)

數據庫遷移實戰:Spring Boot項目完整遷移指南)

的用途)