【 聲明:版權所有,歡迎轉載,請勿用于商業用途。 聯系信箱:feixiaoxing @163.com】

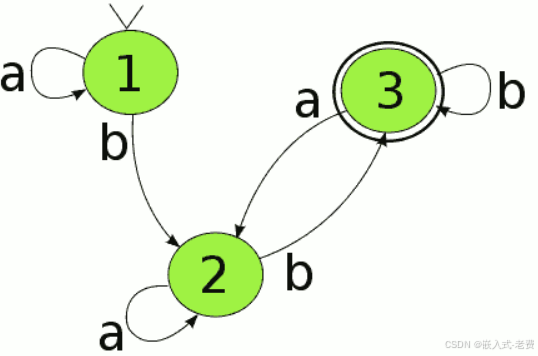

? ? ? ? 前面說過,fpga上面最基礎的部分是寄存器,而所有寄存器存在每一個clock下,都有被翻轉的可能性。至于這些寄存器是不是真的翻轉,或者說是保持不變,取決于當時的狀態。所以在clock運行的區間內,我們習慣于把任務切分成若干個狀態,不同狀態下的register是不一樣的,當然只有一部分register參與工作,大部分保持不變。等到條件成熟的時候,再切換到下一個狀態。這就是fpga下狀態機運行的基本原理。

1、時序邏輯是基礎

? ? ? ? 寄存器是fpga的基本電路。或者可以這么說,fpga的基本構成就是一個一個的時序邏輯。這些時序邏輯或者置0,或者置1,或者取反,或者保持不變。針對這些寄存器的運算,那就是組合邏輯。當然組合邏輯不能鏈路太長,否則影響時序。除了寄存器的運算之外,組合邏輯的另外一個信號來源就是外部輸入。所有的外部輸入都可以看成是組合邏輯。

2、組合邏輯是輔助

? ? ? ? 時序邏輯可以保證,信號在clock的周期內保持不變,這是極為重要的特性。如果信號隨時發生改變,那也就沒有辦法參與運算了,因為很多的運算本身就是依賴于其他信號的存在,這樣才會一步一步向前推進,而組合邏輯則不一樣。

? ? ? ? 就拿外部信號舉例,假設來一個gpio信號,fpga正常運行,此時由于gpio優先級高,那么下一個clock就要優先處理這個gpio。但是如果下一個clock來臨之前,又有一個gpio信號出來。不失一般性,前者命名為signal A,后者命名為signal B,那么此時就會發生仲裁,如果signal B優先級高,下一次優先處理的信號就是signal B。在clock之間的這段時間,時序電路是不變的,但是組合邏輯可能隨時由于外部的輸入而發生變化,這就是組合邏輯的特點。

3、clock和rst是最重要的兩個信號

? ? ? ? clock是寄存器的發動機,它推動著寄存器,或者是時序電路不停向前走。形象一點比喻,它就類似于交響樂隊的指揮棒,每一個演奏者都要跟著這個指揮棒進行操作。而rst就是復位信號,在板子還沒有啟動的時候,或者說clock還不穩的時候,rst保證了信號最初始的一個狀態。所以,正是由于clock和rst的存在,讓fpga可以按照我們的設計來處理各種各樣的信號。

4、小模塊的狀態機和系統狀態機

? ? ? ? 狀態機不僅僅是小模塊可以使用,大模塊也可以使用。在小模塊里面,不同狀態下,相當于一部分register參與運算,另外一部分register不參與運算。而在大模塊下,則相當于一部分模塊參與運算,另外一部分模塊不參與運算。本質上,兩者是一樣的。

5、從波形到代碼,再到波形

? ? ? ? 了解了時序邏輯、組合邏輯和狀態機之后,我們發現fpga的顆粒度很低,本質上,它就是一個信號計算器。抽象出來,就是一個一個波形。所以,如果我們需要設計什么功能,可以先設計出原型、狀態機,或者是自己先把波形畫出來,接著把這些波形轉成verilog代碼,最后在仿真測試、實際測試,驗證一下實際的波形和設計的波形是不是同一個,這樣就可以驗證自己寫的到底對不對,是設計的問題、寫的問題、還是測試的問題。

6、時刻牢記寄存器的并發性

? ? ? ? fpga最大的不同,就是寄存器的并發性。只要有時鐘在驅動,所有寄存器就有翻轉、改變的可能性。至于是不是真的改變,完全取決于當時的狀態。所以編寫verilog的時候,可以考慮下,當前信號屬于什么信號,什么時候復位,什么時候改變,改變的時候屬于什么狀態,什么時候又保持不變,這樣不停思考下去,fpga才能越寫越好,越寫越穩定。

? ? ? ? 不同的task,一旦發現數據合法性不對,就立馬恢復到初始狀態。等到所有input和register都ok之后,再去開始對應的工作,這樣就可以讓fpga一直穩定地運行下去。

)

)

7.27)

)

市場調研 如何在行業研究中快速有效介入 起頭篇)

)

)