目錄

1 硬件描述語言簡介

1.1 硬件描述語言簡介

1.2 硬件編程語言的發展歷史

1.3 兩種硬件描述的比較

1.4 硬件描述語言的應用場景

1.5 基本程序結構

1.5.1 基本程序結構

1.5.2?基本語句和描述方法

1.5.3 仿真?

1 硬件描述語言簡介

1.1 硬件描述語言簡介

硬件描述語言(Hardware Description Language, HDL)是一種用于描述電子系統(尤其是數字電路)結構、行為和功能的專用編程語言。它允許工程師以文本形式對硬件(如集成電路、FPGA、ASIC等)進行建模、設計和驗證,是電子設計自動化(EDA)流程的核心工具之一。

相較于傳統的編程語言,例如C、Java等,硬件描述更加注重硬件之間的連接關系、時序運行以及并行操作等物理特性。主流的硬件描述語言包括Verilog HDL和VHDL,如下所示:

1.2 硬件編程語言的發展歷史

上世紀1970s開始,隨著電路的復雜度的提升,傳統的手工繪圖的方式開始變得低效,學術界開始研究文本硬件描述方法。1972年,美國南加州大學?D. D. Gajski開始研究AHDL(A Hardware Programing Lauguage),這是早期的數字電路描述語言。

目前主流的兩種硬件描述語言均誕生在20世紀80年代,在上世紀80年代時,已經有上百種硬件描述語言,是硬件描述語言快速發展的時代。其中,Verilog HDL是由Gateway Design Automation公司開發的,后來被Cadence公司收購。VHDL是上世界80年代美國國防部資助開發的,作為ADA語言的一部分,用于規范文檔和設計。VHDL和Verilog HDL分別在1985年和1997年成為IEEE標準。

2000年以后,衍生了更加高級的HDL,支持系統級驗證和混合信號建立。

1.3 兩種硬件描述的比較

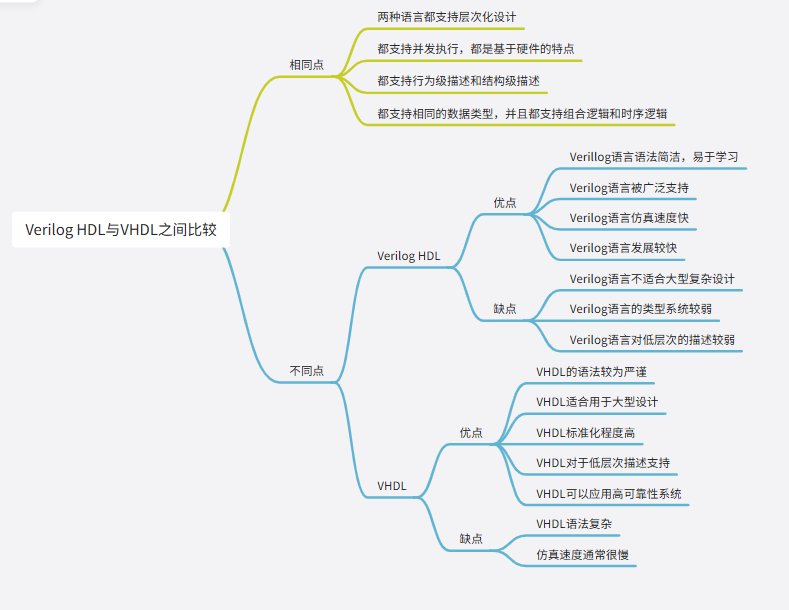

Verilog HDL和VHDL之間都有相同點:

- 兩種語言都支持層次化設計。

- 都支持并發執行,都是基于硬件的特點。

- 都支持行為級描述和結構級描述。

- 都支持相同的數據類型,并且都支持組合邏輯和時序邏輯。

除了相同點之外,Veriilog HDL和VHDL之間也存在不同點,對于Verilog HDL語言來說,相對于VHDL,優點為:

- Verillog語言語法簡潔,易于學習。

- Verilog語言被廣泛支持。

- Verilog語言仿真速度快。

- Verilog語言發展較快。

缺點為:

- Verilog語言不適合大型復雜設計。

- Verilog語言的類型系統較弱。

- Verilog語言對低層次的描述較弱。

對于VHDL語言,其優勢為:

- VHDL的語法較為嚴謹。

- VHDL適合用于大型設計。

- VHDL標準化程度高。

- VHDL對于低層次描述支持。

- VHDL可以應用高可靠性系統。

而其劣勢為:

- VHDL語法復雜。

- 仿真速度通常很慢。

將上面內容進行總結得:

1.4 硬件描述語言的應用場景

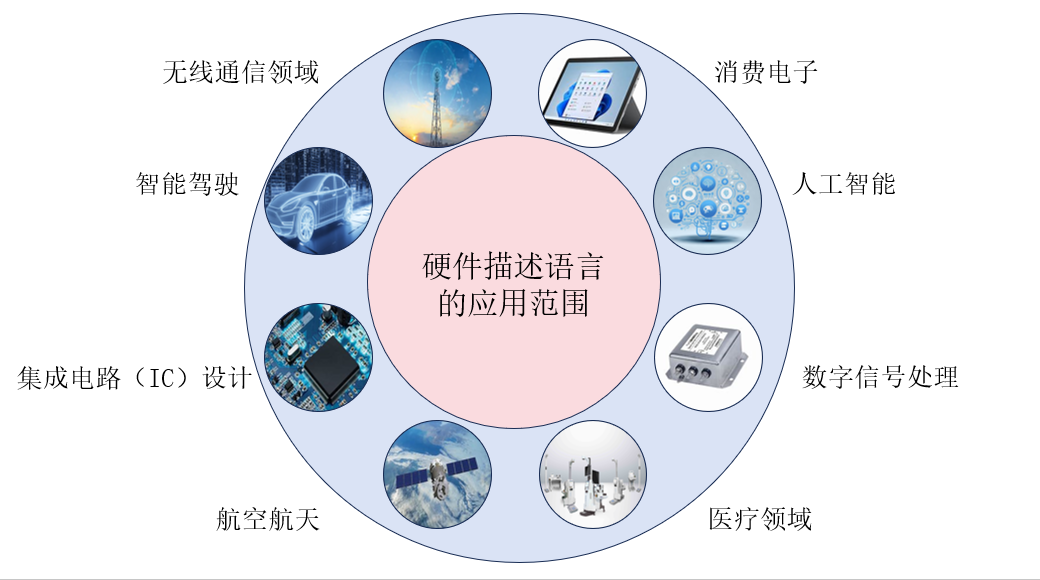

硬件描述語言的應用十分廣泛,涵蓋范圍如下所示:

下面對于各個方面基進行簡答介紹。

(1)人工智能

人工智能是當下火熱的研究內容,HDL可以顯著提升了深度學習中的神經網絡計算,特別是圖像識別中的卷積運算。通過硬件并行性,HDL可以有效地處理大量的圖像數據,減少計算資源的浪費。同時,隨著物聯網(IoT)的發展,邊緣計算是相對熱門的話題,FPGA在邊緣計算中可以提供快速、高效的數據處理能力,減少數據傳輸到云端的需求,降低延遲和帶寬消耗。

(2)智能駕駛

CAN(Controller Area Network)總線是一種廣泛應用于汽車電子、工業控制、航空航天等領域的可靠串行通信協議。CAN協議的數據幀結構包括幀起始位、仲裁字段、控制字段、數據字段、校驗字段等多個部分。VHDL可以通過行為級描述來實現對這些字段的解析和生成,同時利用其并行處理能力來處理多個字段的同步操作。VHDL的高抽象性和模塊化設計使得CAN協議的實現具有很高的靈活性和可擴展性。設計者可以根據不同的應用場景和需求,對CAN協議進行定制和優化。

(3)通信領域

HDL在通信領域同樣也有應用。例如,在基帶信號處理方面,完成各種調制方式,如相移鍵控(PSK)、正交幅度調制(QAM)等。HDL可根據不同的通信標準和需求,靈活實現調制和解調算法,將數字信號轉換為適合在信道中傳輸的模擬信號。在射頻信號處理方面,在發射端將基帶信號上變頻到射頻頻段以便通過天線發射,在接收端,將射頻信號下變頻到基帶頻段進行后續處理。FPGA 可以生成各種頻率的本振信號,并與基帶信號進行混頻,實現頻譜搬移。

(4)集成電路(IC)設計

在 IC 設計的早期階段,設計人員通常使用 HDL 進行行為級描述。這種描述方式側重于對電路功能的抽象表達,而不涉及具體的硬件結構。在 IC 設計過程中,需要對設計的功能進行驗證,確保其符合設計要求。HDL 可以用于搭建測試平臺,生成激勵信號并監測電路的輸出響應。例如,對于一個設計好的存儲器芯片,使用 HDL 編寫測試平臺可以模擬不同的讀寫操作,檢查存儲器的讀寫功能是否正常。

(5)數字信號處理

HDL在數字信號處理有很多應用。例如在濾波器的設計方面,如果想設計一個FIR(有限沖擊響應)濾波器,可以通過HDL代碼在FPGA中實現。HDL代碼可以定義濾波器的系數存儲、乘法累加運算等邏輯,從而實現對輸入信號的濾波處理。在快速傅里葉變化的應用中,FFT是數字信號處理中的重要算法,用于將時域信號轉換為頻域信號。HDL可以在FPGA中實現FFT算法的硬件加速。通過編寫HDL代碼,可以定義蝶形運算單元、數據存儲和調度等邏輯,實現高效的FFT運算。

(6)醫療領域

HDL在醫療領域也有較多的應用,例如在醫療成像領域,在 MRI、CT 等醫學成像設備中,HDL 可用于設計圖像重建算法模塊。通過對采集到的大量原始數據進行快速處理和運算,利用 HDL 實現如反投影算法、迭代重建算法等,能夠在短時間內重建出高質量的人體內部器官圖像,為醫生提供準確的診斷依據。在醫療監護領域,DL 可用于設計生理信號采集與處理模塊。可以對心電、血壓、血氧等多種生理信號進行實時采集、放大、濾波和模數轉換等處理。

(7)航空航天

HDL在高性能、高可靠性和和復雜系統設計方面有很多應用。例如,在航空發動機系統設計中,基于模型的系統工程(MBSE)方法結合HDL工具,可以實現需求驅動的正向設計流程,快速搭建系統模型,并與多學科聯合仿真驗證程序融合。HDL工具通過內置的設計規則集合(包括DO-254等安全關鍵設計規則集),能夠確保設計滿足航空航天行業的嚴格標準。

(8)消費電子

消費電子是普通人接觸較多的領域,HDL在消費電子也有很大的應用。例如,在顯示驅動方面實現屏幕控制和顯示優化,在智能手機、平板電腦、智能手表等各類顯示屏設備中,HDL 可用于設計顯示驅動芯片。它能精確控制屏幕的像素點發光,實現不同分辨率、刷新率和色彩模式的顯示。在音視頻處理方面對于高清視頻的解碼,在智能電視、機頂盒、藍光播放器等設備中,HDL 可用于設計專用的視頻解碼芯片。

1.5 基本程序結構

1.5.1 基本程序結構

和其他編程類似,Verilog HDL也是采用模塊化的結構,以模塊化的形式來描述數字電路系統。模塊(module)是Verilog HDL語言中描述電路的基本單元。模塊的基本語法如下所示:

module<模塊化>(<端口列表>)

<定義>

<模塊條目>

endmodule??最基本的模塊如下所示:

module module_name (input [width] input1, // 輸入端口input [width] input2,output [width] output1, // 輸出端口output [width] output2

);// 模塊內部邏輯

endmodule上面的端口定義兩個輸入端口和兩個輸出端口。

1.5.2?基本語句和描述方法

對于組合邏輯來說,使用assign實現組合邏輯:

assign output = input1 & input2; // 邏輯與操作組合邏輯是輸出信號僅依賴于當前輸入信號的邏輯。例如,設計一個簡單的2輸入與門:

module and_gate (input wire a,input wire b,output wire y

);assign y = a & b; // 組合邏輯

endmodule而對于時序邏輯電路來說,使用always塊實現時序邏輯,通常與clock信號結合。如下所示:

always @(posedge clk) beginif (reset) beginreg_out <= 0;end else beginreg_out <= input;end

end

時序邏輯的輸出不僅依賴于當前輸入,還依賴于過去的輸入。例如,設計一個D觸發器:

module d_ff (input wire clk, // 時鐘信號input wire reset, // 異步復位信號input wire d, // 數據輸入output reg q // 數據輸出

);always @(posedge clk or posedge reset) beginif (reset) beginq <= 0; // 異步復位end else beginq <= d; // 數據鎖存endend

endmodule?生成結構是Verilog中一種強大的功能,允許在編譯時根據參數條件創建或重復模塊實例、寄存器、線網或其他Verilog元素。它主要用于創建可配置和可重用的設計。主要的生產結果包括generate-for循環、generate-if循環、generate-case循環:

例如generate-for循環:

generateif (WIDTH > 4) begin : wide_block// 當WIDTH>8時包含的代碼reg [WIDTH-1:0] wide_reg;endelse begin : narrow_block// 否則包含的代碼reg [7:0] narrow_reg;end

endgenerateVerilog中一種編譯時循環結構,主要用于在硬件描述中創建重復的電路結構。

1.5.3 仿真?

仿真用于驗證Verilog代碼的功能是否正確。通常使用仿真工具(如ModelSim、Vivado Simulator等)進行仿真。仿真工具會生成波形圖,顯示輸入和輸出信號隨時間的變化。設計人員可以根據波形圖判斷是否設計正確。

因為本系列主要講的是數字電子技術內容,在這里對于Verilog HDL和VHDL不進行更加細致的講解,以后有機會的話可能對于這編程語言進行講解。

)

默認不聚焦問題處理)

)

)