一、MOSFET

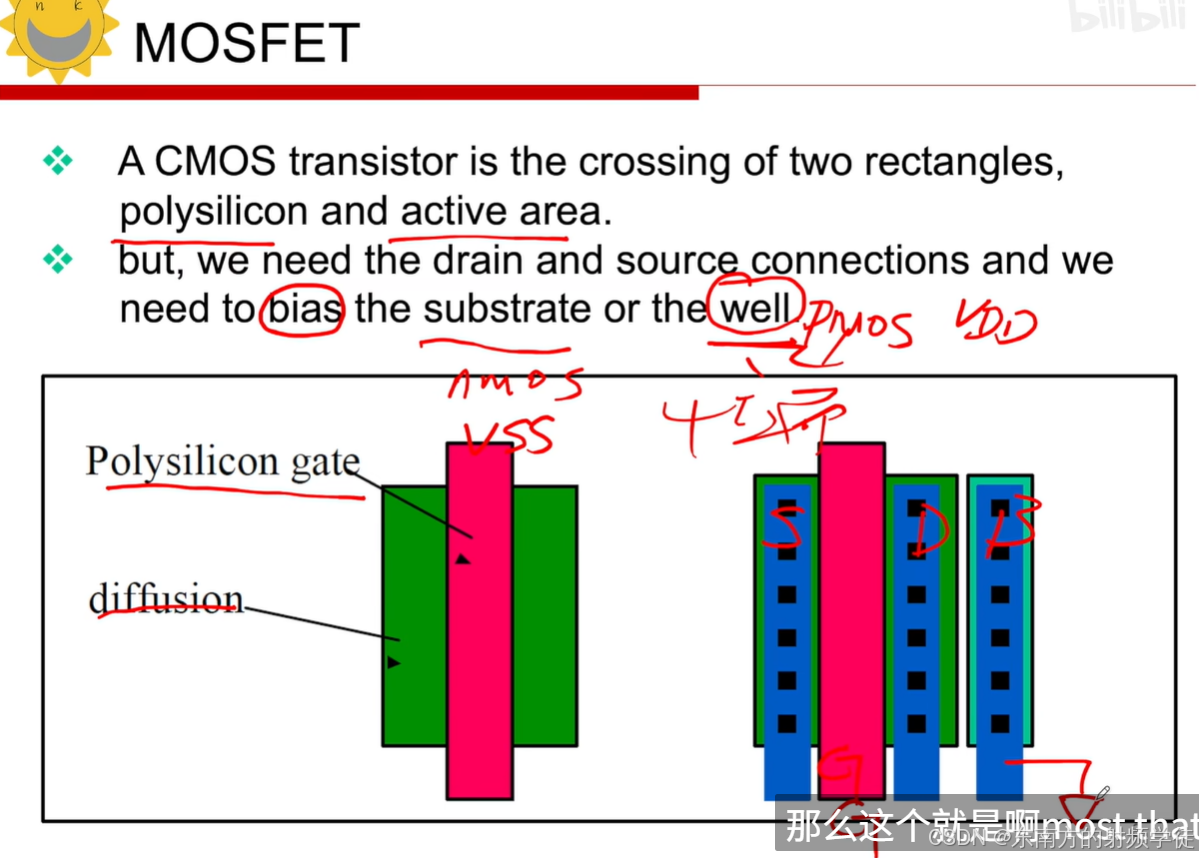

- 在版圖設計中,要定義一個mosfet,最關鍵的層次是polysilicon(多晶硅)和active(有源區)。用有源區定義了一個矩形的區域,在這個區域內才可以形成一個有源器件,然后再用多晶硅畫出的矩形與有源區進行交疊,這樣就形成了器件的核心區。

- 下圖中,綠色區域是有源區,上面還要覆蓋上一層摻雜(diffusion),這樣去定義其源漏區。然后再交疊上polysilicon gate(多晶硅柵極),這樣mosfet器件的基本結構就出來了。

- 之后我們要將其源漏和襯底進行互連。

- 此外,我們要注意,將襯底(nmos的p襯底)或者阱well(pmos的nwell)進行合理的偏置,即接到相應的電源或者地上。

端口的可靠連接

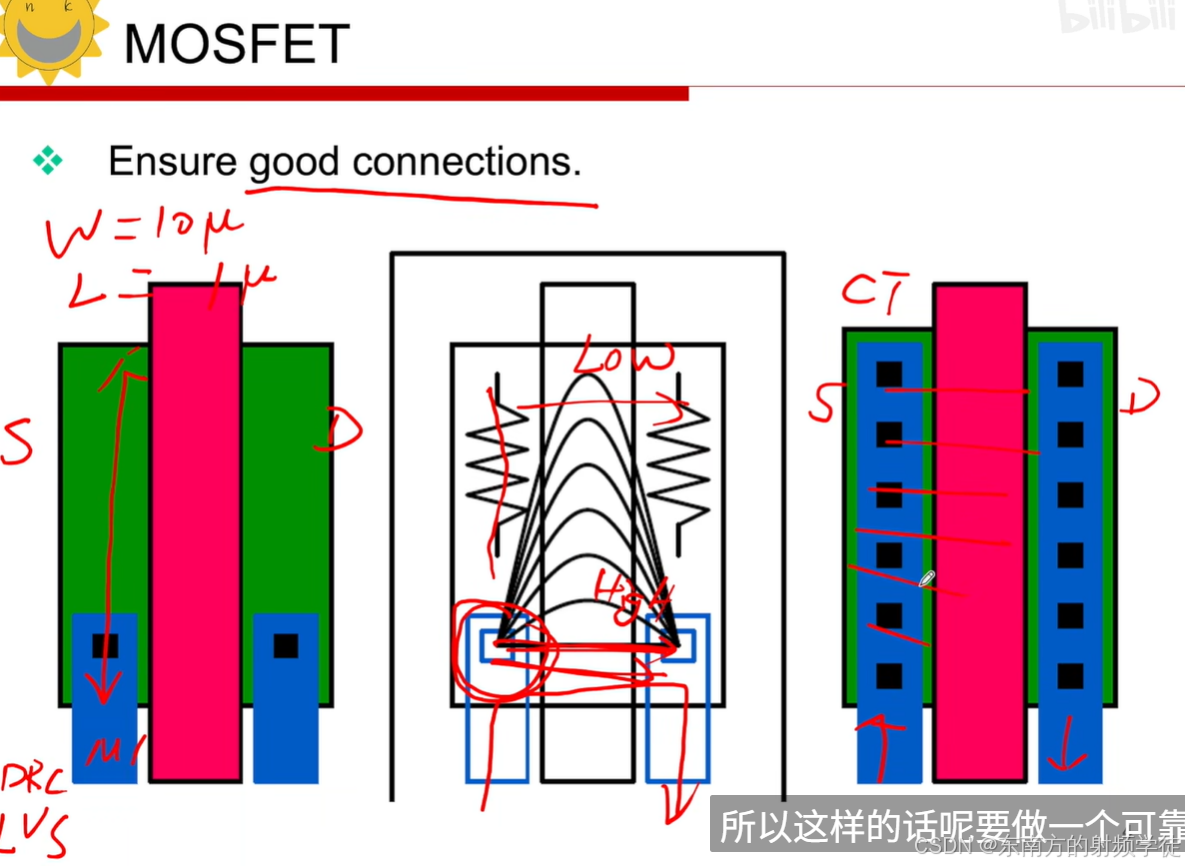

- 當我們做好mosfet的基本結構之后,一定要有可靠的連接。

- 如果一個mosfet的漏源區比較長,然后需要把漏源區進行連接,則要借助contact連接到M1上。如果只是在邊緣處用一個過孔進行連接,DRC和LVS檢測都是不會出現問題的,因為確實是連接上了。

- 但是這種連接是不可靠的,因為整個源漏區都是通過摻雜連接在一起的,阻抗是比較高的。假如把這種不可靠連接的晶體管作為開關,電流要流通這個晶體管,會導致有金屬連接的區域電阻比較低,而越往里的電阻較高,電流會趨向于在有可靠金屬連接的區域流動,因此電阻低的地方電流密度大,電阻高的地方電流密度小。這會很大程度上影響晶體管的特性,因此一定要做可靠的連接

- 我們要把源漏區均勻的覆蓋上contact,把整個源漏都用金屬M1進行覆蓋,這樣整個源漏區的電位基本上是統一的,因為金屬的電阻非常低,做到比較低的壓降,電流在晶體管內是均勻分布的。

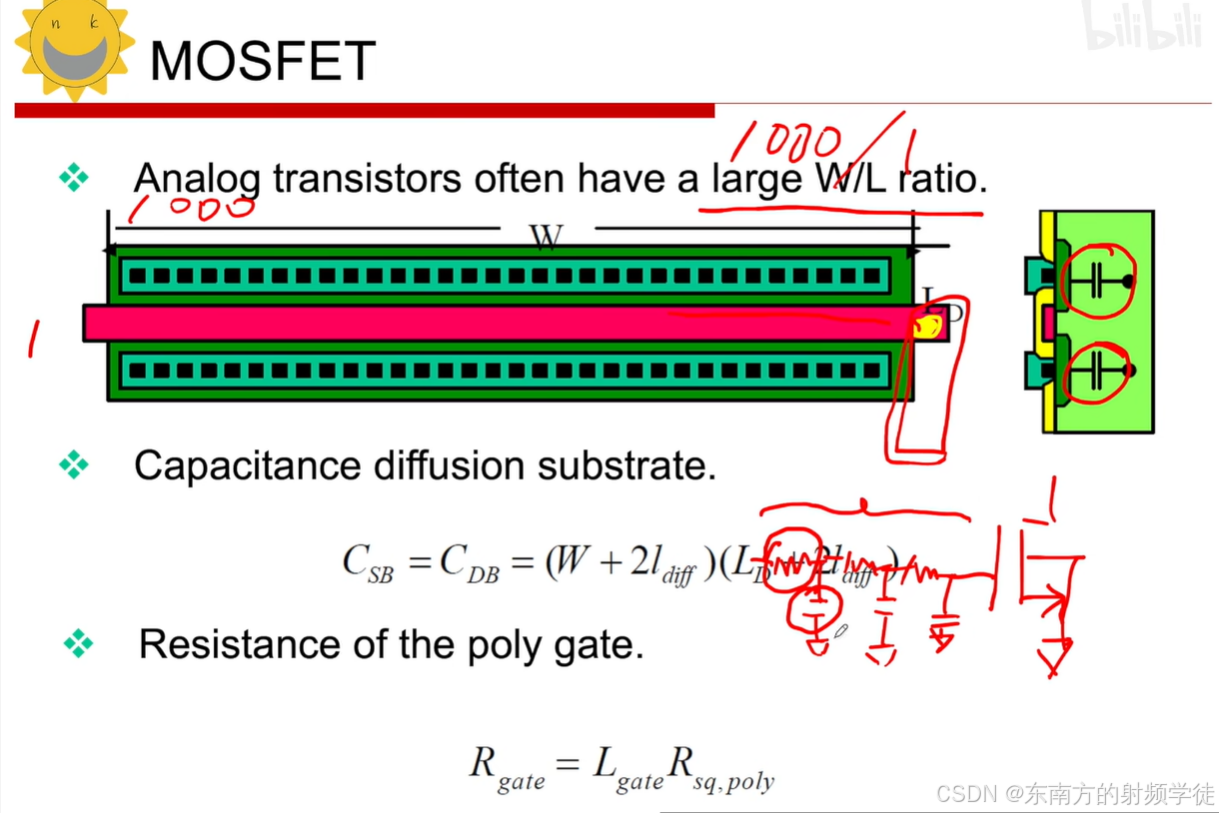

大寬長比晶體管的問題

- 當我們在繪制非常大寬長比的晶體管的時候,比如在設計低噪聲放大器的時候,輸入晶體管會比較大,比如1000/1寬長比,其L=1um,W=1000um,這個晶體管是一個細長的線條,這會導致兩個問題

- 問題1:源漏區的面積會非常大,導致源漏的寄生電容會非常大,因為源漏區和襯底之間時會有一個反偏PN結的,就會出現勢壘電容,其容值和源漏區的面積相關。

- 問題2:gate會特別長,由于gate需要通過contact連接到金屬上,然后在gate另一端用contact連接出去。但是由于gate的寄生電阻和電容是比較大的,當信號從contact傳輸進去的時候,會出現RC分布延時的問題,相當于是柵極上串聯了很多個RC的分布式模型。如果gate比較長的話,則RC的分布式模型也會特別長,那么信號從柵極輸入進去,出來肯定會出現一個畸變,如果信號頻率特別高的話,很可能出來的控制信號已經消失掉了。(問題2比問題1更嚴重,因為gate的寄生導致傳遞信號的速度跟不上了)

- 有一種解決辦法是,在gate上多打上contact,像漏源區一樣,然后用整個金屬把gate覆蓋上,實際上信號是通過金屬傳遞到一段一段的gate上的。這種辦法在理論上是可以解決這個問題的,但是在design rule不允許在溝道上方畫contact的,主要是因為溝道是一個比較敏感的結構,容易影響到溝道的電學特性。

- 在真正去畫版圖解決大寬長比晶體管的問題,通常采用finger

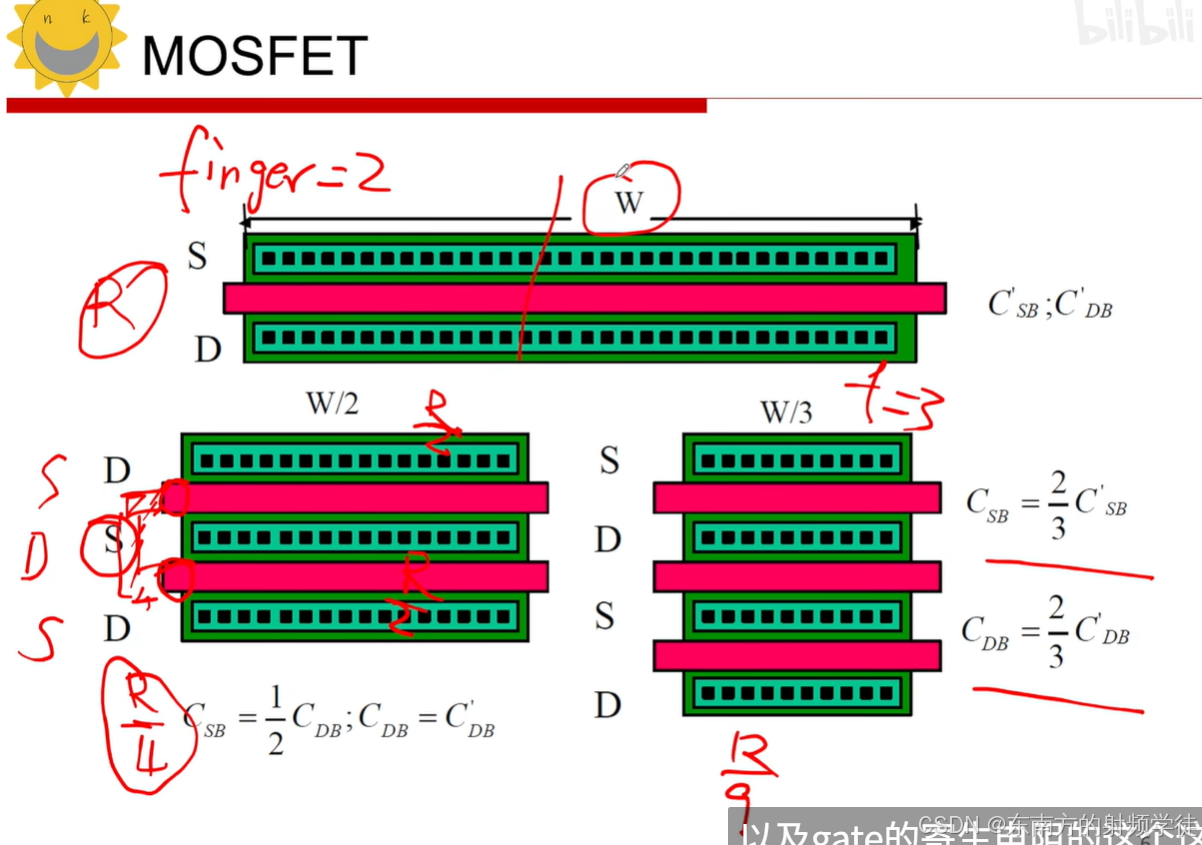

finger

- 拆分晶體管為漏源漏的方式。

- 當finger為2,原來源的長度變為原來的一半,源極的寄生降低了,漏有兩個,因此原來漏的寄生并沒有變化。gate被拆成兩截,因此我們可以在不同截的端口處打上contact,用金屬將他們給并聯起來,相當于原來gate的寄生變小了,降低了4倍。

- 當finger變為3的時候,源漏源漏的結構,那么源漏的寄生變為原來的1/3,gate變為原來的1/9。這樣gate的寄生電阻將會很大程度的降低。

- finger數越多,gate的寄生就會越小

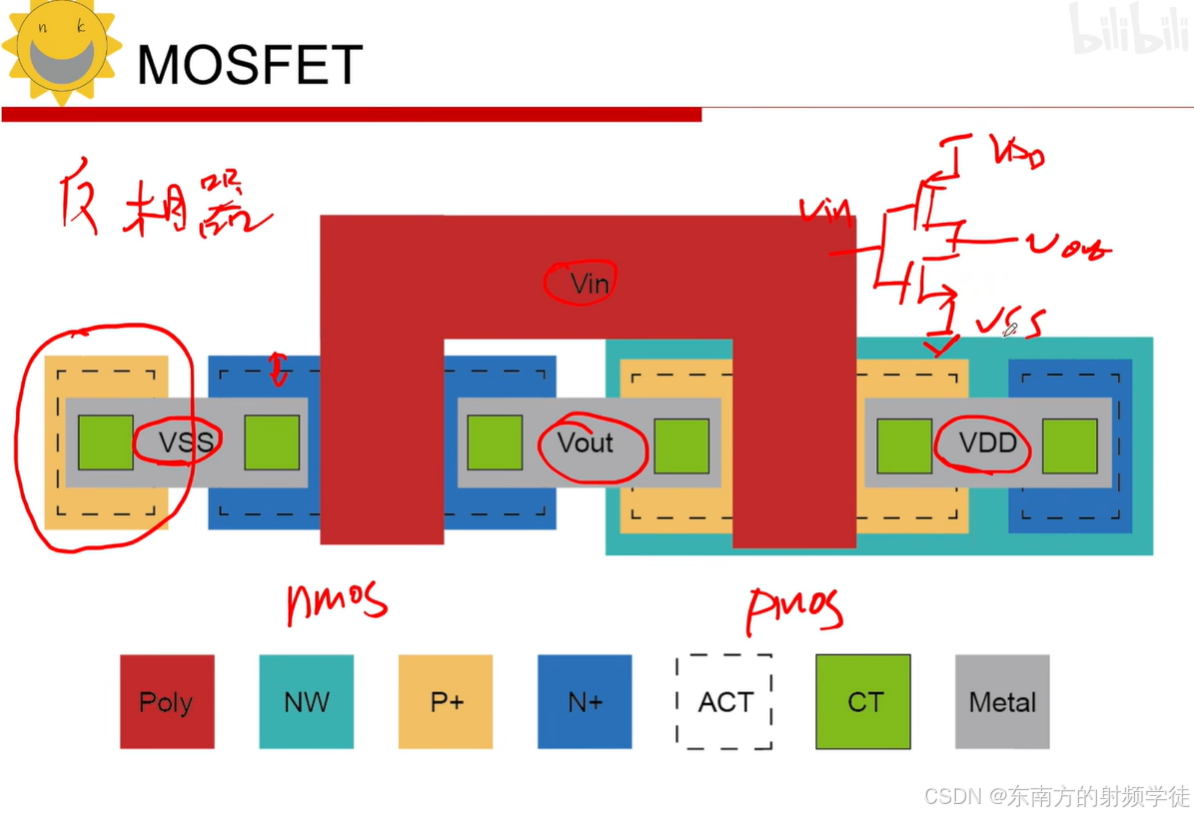

MOSFET版圖的示意圖

- 下圖是一個反相器的版圖示意圖,左側是NMOS,右側是PMOS。

- 左側的NMOS用有源區(黑色虛線框)包圍了,有源區外有N+(藍色區域)的注入,即N+要enclosure有源區。然后用gate poly覆蓋住有源區的中心位置,形成溝道區,并在兩側畫上contact,再用金屬連接出去,

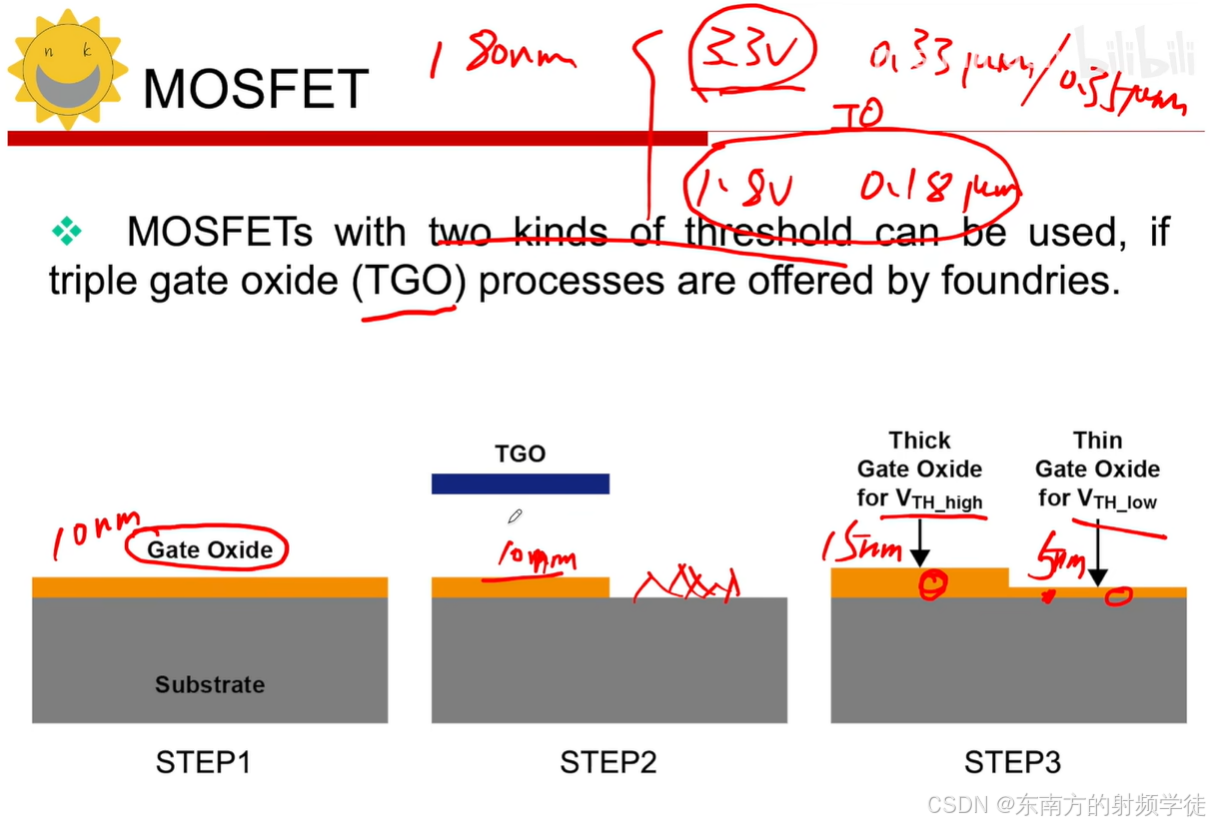

TGO(triple gate oxide)

- 這個工藝主要是為了提供兩種不同閾值的晶體管。通常一個工藝中會提供兩種不同閾值的晶體管,一個是高閾值,一個是低閾值。高閾值的柵氧厚度要厚一些

- 低閾值的柵氧會很薄,其承受的電壓比較低,器件尺寸也會比較小,工作電壓也可以更低,這樣可以減小功耗,也可以節省面積。一般數字電路常使用這種低閾值的器件;

- 但是模擬電路比較喜歡用具有高本征增益的器件,那么其溝道長度會比較長一些,尺寸也較大;此外為了信號幅度更寬(承受更大的噪聲,信噪比更好),但是帶來的犧牲就是功耗和面積。或者IO接口電路

- 這就需要一個新的光刻板(TGO)。

- 做柵氧首先會在全芯片上都長出一定厚度的gate oxide,然后再加入TGO這一層光刻板,將TGO以外的柵氧給刻蝕掉。然后再在整個wafer上生成一遍較薄的柵氧

- 由于整個器件經歷了三個步驟,因此叫triple gate

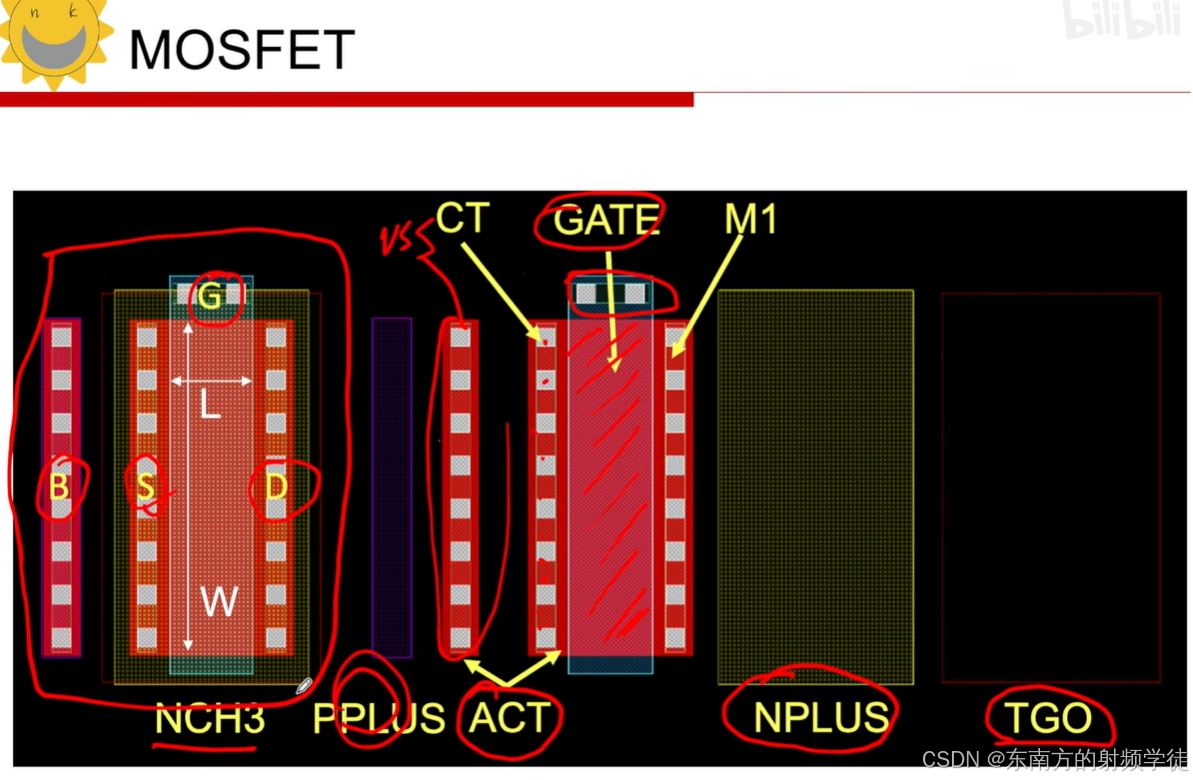

典型NMOSFET版圖

- 左側是完整版圖的形狀(NCH3),然后把所有器件都大散拆開,看下里面有哪些層次。

- 有源區(active)和柵極(gate)交疊,就構成了溝道區,然后在整個區域覆蓋上n plus(n+注入),就定義好了源漏。然后使用contact做可靠的連接,在源漏區均勻覆蓋上contact,再使用M1進行連接。

- 還有TGO層的layer,意味著這是高壓的厚氧化層的器件。

- 不同工藝器件名字不一樣,比如這里的NCH3,表示n channel溝道的mosfet的3.3v的器件。

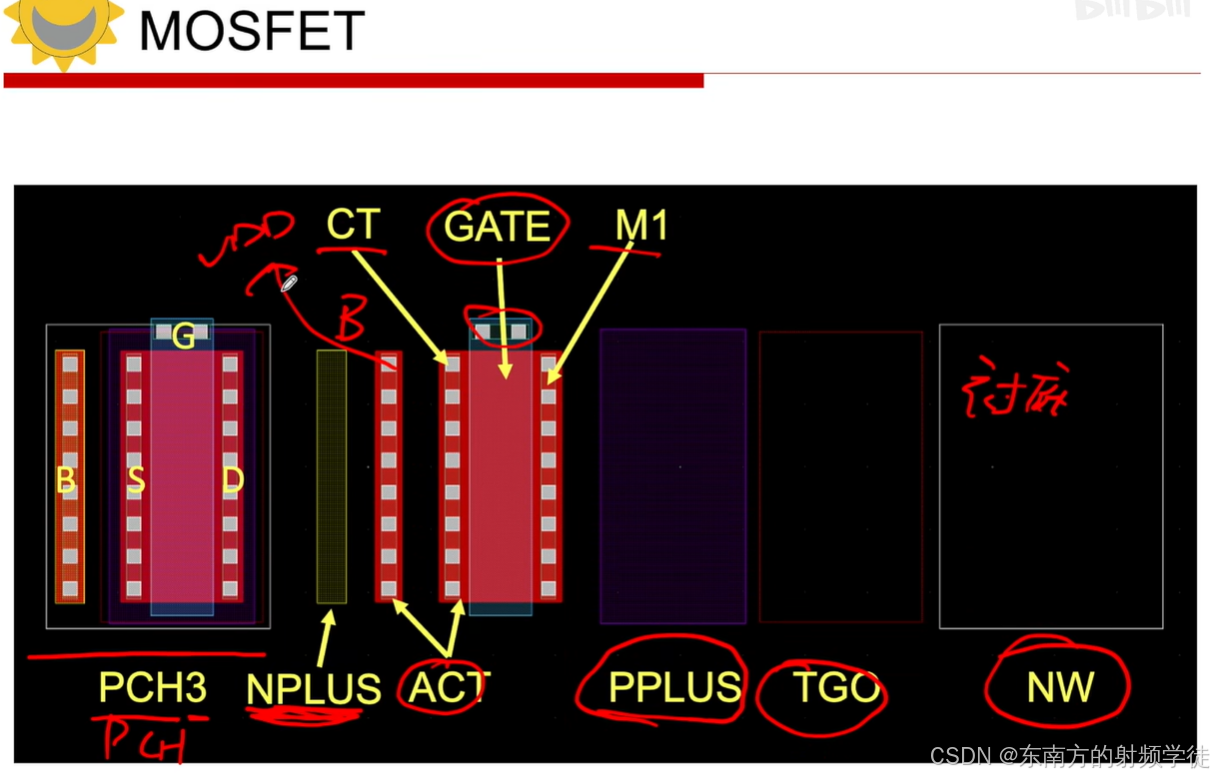

典型的PMOS版圖

- PCH3,表示p channel溝道的高壓器件,3是高壓的

- 核心區域和nmos都是一樣的,但還覆蓋p plus(P+注入),

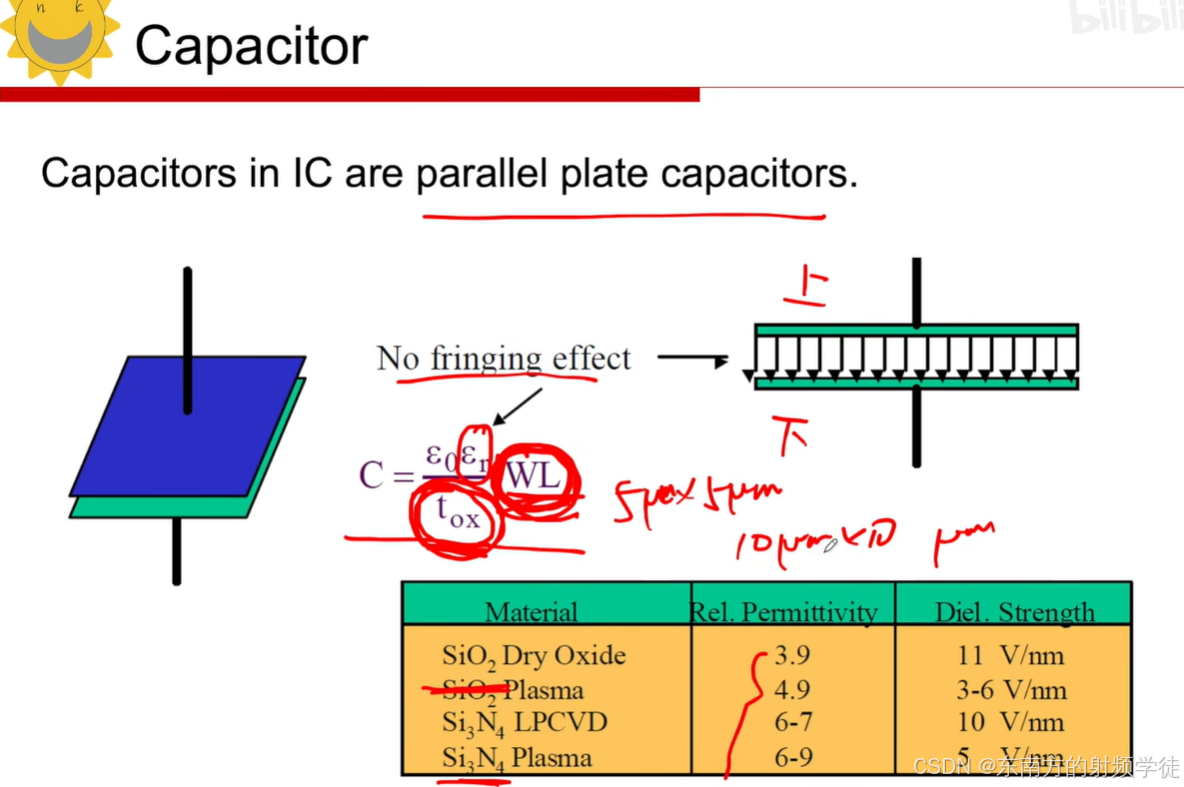

二、電容Capacitor

- 最簡單的電容是由兩個平行的金屬板,中間夾著絕緣的介質層,這兩個板就成為了電容的兩個電極。

- 在集成電路中,通常的絕緣介質是二氧化硅,或者是氮化硅(Si3N4)。所以在選擇好工藝之后,相對介電常數是固定的。

- 對于設計者來說,能改變的只有氧化層的厚度tox,還有金屬板的面積W*L

- 厚度tox也不能去靈活去改動,但可以去選擇,一般一個工藝會提供不同的厚度

- 所以更多的是去改變金屬板的面積

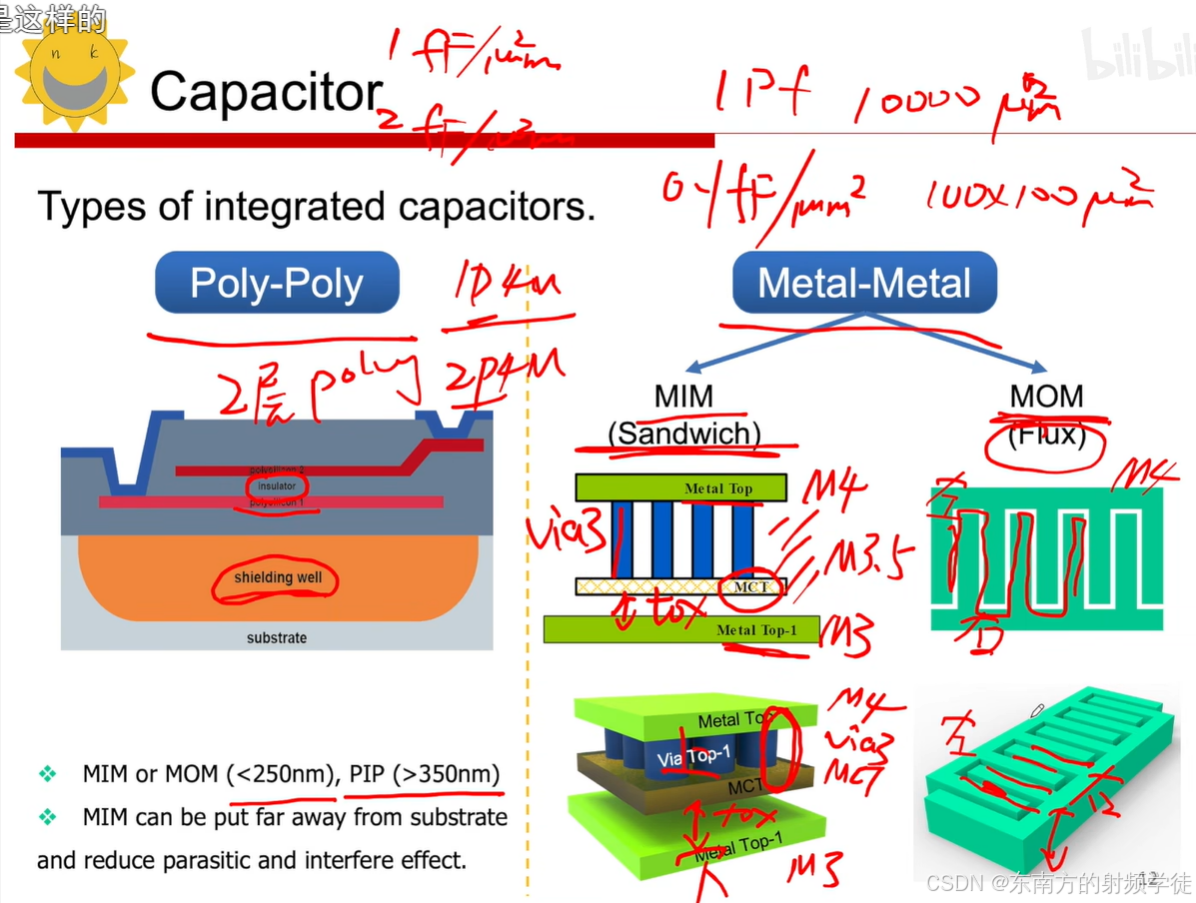

IC電容類型

- 集成電路中的電容主要有兩大類

- 第一類是poly to poly。是兩個poly之間形成的電容,電容上下極板都是poly,中間夾著isulator絕緣介質構成的電容器件。

- 意味著需要有兩層的poly,比如像1P4M工藝是做不了的,因為只有一層poly,像2P4M工藝才有可能提供poly-poly電容。

- 但這種電容一般是在特征尺寸比較粗的情況下(大于350nm工藝)

- 這種類型的電容存在一些問題,由于poly與襯底離的比較近,對襯底的寄生是比較大的,串擾是很難規避的。

- 這種天生的缺陷,因此要進行隔離(shielding well)

- 第二類是metal to metal。是兩個金屬之間夾著的絕緣介質,構成的絕緣器件。先進工藝使用的比較多mim和mom電容。

- 第一種是MIM電容(metal inter metal)金屬-絕緣層-金屬結構,類似三明治(sandwich)。

- 首先要有兩層金屬(metal top層金屬和metal top-1層金屬),如果只使用這兩層金屬做電容的問題是,產生的電容密度會比較小(單位面積下的容值),比較浪費面積。

- 所以只能降低絕緣層厚度tox了。工藝上會提供MCT層金屬,可以理解為M3.5層,介于M3和M4之間,作為電容的上極板。然后通過通孔和Metal top層金屬進行連接。MCT和M3之間是絕緣介質,形成電容。

- MCT層的位置是可以移動的,距離M3的高度可調節。通過移動,可以將厚度tox降到很低很薄,提高電容密度。這樣就意味著一道工藝可以提供不同電容密度的電容。但是要注意MCT在加工過程中是全芯片的,只能是同一個MCT。所以這次流片只要選定好這個距離后,整個芯片的距離都是這個距離不能再改變了。一次流片不能提供兩種距離

- 第二種是MOM(metal outside metal),這是flux(叉指)結構。即將同層金屬做成這樣的叉指架構交錯在一起。他們是通過叉指中間的縫隙形成的電容。可以通過叉指的個數和叉指的長度控制電容的大小。

- 第一種是MIM電容(metal inter metal)金屬-絕緣層-金屬結構,類似三明治(sandwich)。

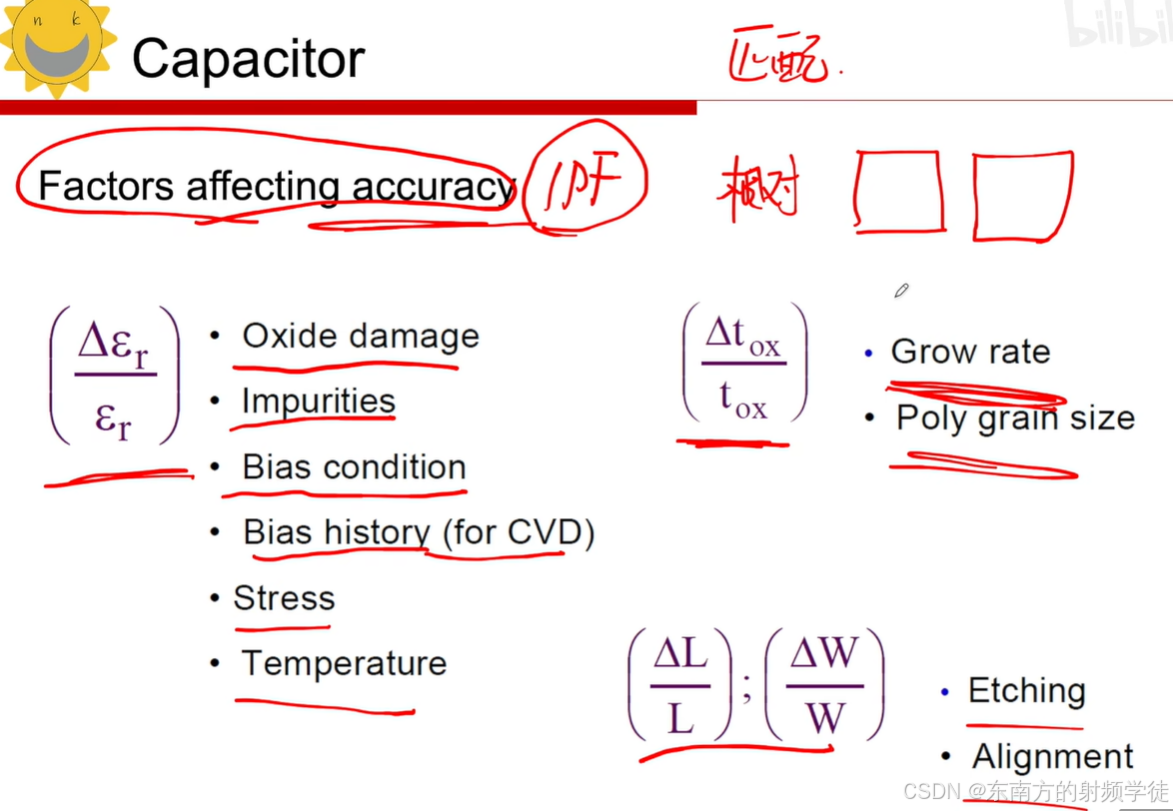

影響電容的精度

- 集成電路加工出來的電容是有一定的誤差的,影響電容的參數主要有以下幾種

- 第一個是相對介電常數。比如下面這些情況可能會產生影響

- Oxide demage(氧化層的損傷)

- Impurities(氧化層中的雜質)

- Bias condition(電容的電學偏置狀態)

- 氧化層在淀積的時候用到的CVD(化學氣象電機)

- stress(應力)和temperature(溫度)

- 第二部分是氧化層的厚度(tox)

- grow rate(生長的速率)生長的快慢厚度會不一樣

- poly grain size(精力的大小)

- 第三部分是金屬板的寬和長,尺寸帶來的變化

- etching(刻蝕)和alignment(對齊)帶來的誤差

- 第一個是相對介電常數。比如下面這些情況可能會產生影響

- 在集成電路中可以比較好的保證相對精度,即做兩個電容的容值接近的程度

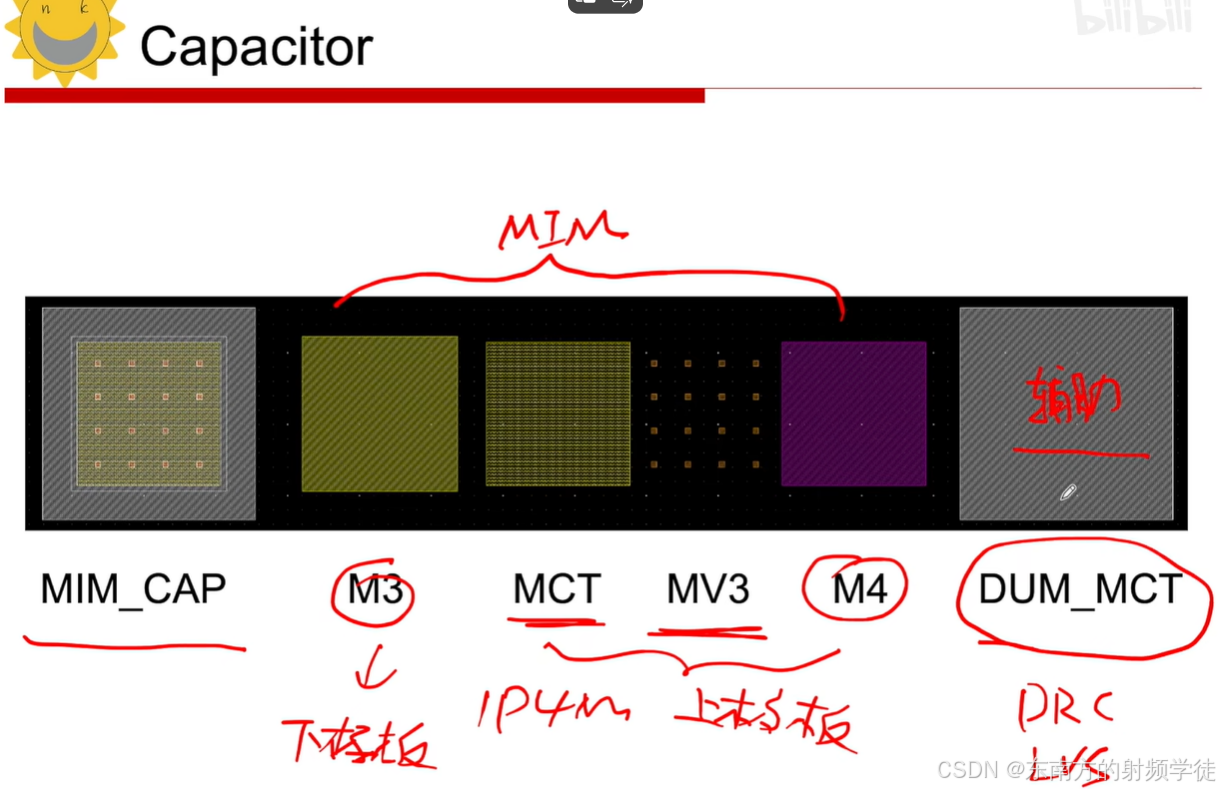

典型MIM電容的版圖

- MIM結構類似三明治,所以有頂層金屬M4,然后是MV3過孔,再下面是MCT,三層結合在一起構成電容的上極板,M3層金屬構成下極板。這些layer其實已經可以構成MIM電容了

- DUM_MCT層實際上是輔助層,并沒有真正的掩膜板mask與之對應。主要是為了讓DRC和LVS工具能夠識別出來這部分區域是電容。

三、電阻Resistor

電阻的類型

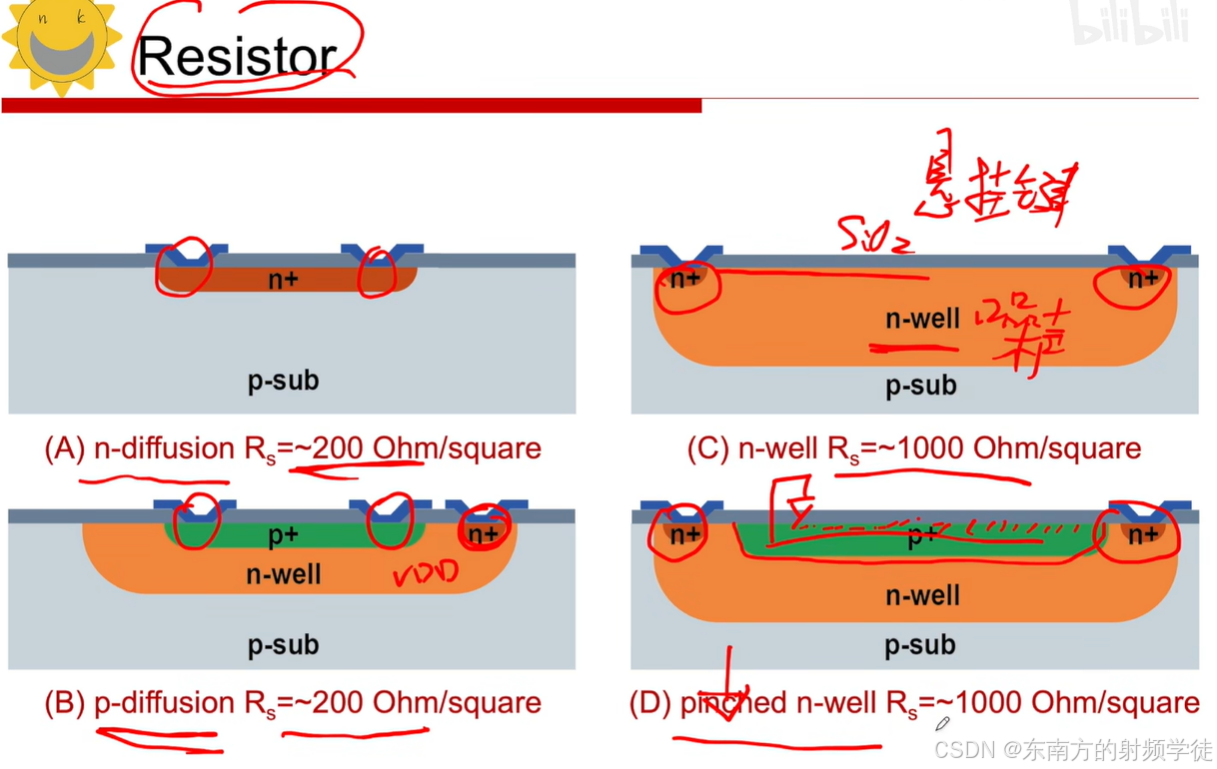

- 在集成電路工藝中,電阻的類型是比較多的,

- 第一種是N+注入形成的電阻,實際上就是在P襯底上畫一塊N+注入,然后再兩端用金屬連接出去。其方塊電阻大致為200歐

- 第二種是P+注入形成的電阻,首先得畫上N阱,在N阱里面畫上P+注入,此外N阱還要做N+的連接,形成合理的偏置到VDD上。靠注入形成的電阻,其方塊電阻值一般都在200歐左右

- 第三種是N阱形成的電阻,畫一塊N阱,然后在兩邊畫上N+注入連接出去。N阱形成的電阻較大,其方塊電阻可以達到上千歐。由于第三種直接在N阱形成的電阻,其表面是wafer的表面(二氧化硅),所以這樣的N阱表面的晶格是斷裂的,就會有很多的懸掛鍵,就會成為失主或者受主,隨機的釋放或者捕捉電子,影響到噪聲的特性,且電阻表面的電流是會有波動的,加劇電阻的噪聲。

- 第四種是Pinched(前衛)N阱,即在N阱的表面加上P+的注入,把P+也接到VDD上。為了降低第三種電阻的噪聲,在表面加入P+的注入,這樣表面的噪聲都通過P+流入到地上了,而且N阱和P+之間的晶格是完美的,沒有缺陷,這樣N阱的表面就不會有懸掛鍵了,就不會有因為懸掛鍵和表面缺陷造成的噪聲了。但是方塊電阻還是沒有太大的變化,也是在上千歐的量級上。

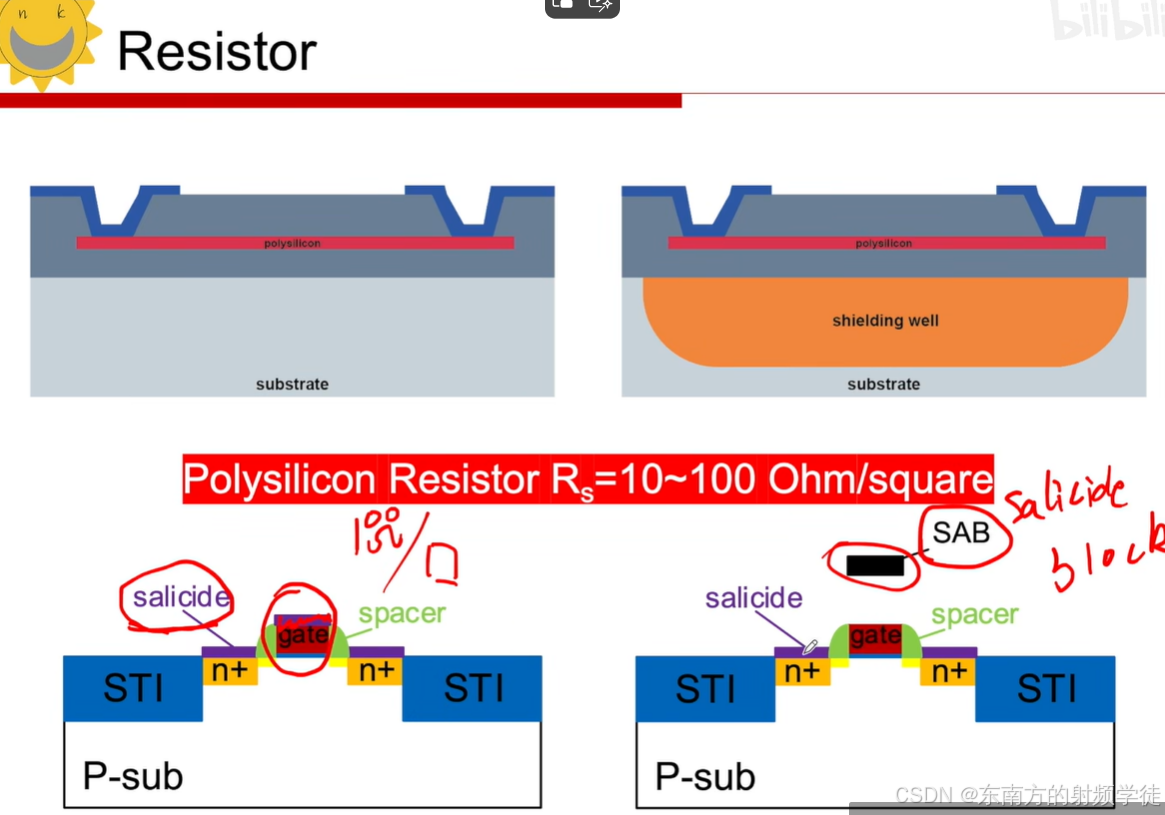

- 還有就是多晶硅(poly silicon)形成的電阻,然后在兩端用contact連接出去,形成poly電阻。

- 為了屏蔽襯底下的噪聲,也可以在poly層下面加上保護阱(shielding well)。

- poly型電阻分為有注入型和無注入型,因為純poly的電阻太高了,所以一般還會在上面加上一層P+或N+的注入。

- poly類型的電阻的方塊電阻值范圍很大,取決于是否有注入和salicide。

- 此外還有salicide(金屬硅化物)工藝,有了這個工藝可以進一步的降低電阻。

- 實際上在集成電路加工過程中,會把整個wafer都涂上salicide,然后再把具有電學連接的位置保留下salicide,剩下的都刻蝕掉。這意味著有源區上的源漏區和gate上面都是覆蓋上salicide的。

- salicide是一種電阻率比較低的材質,覆蓋上它的目的就是為了降低寄生電阻,讓源漏之間的連接更好。

- 方塊電阻值越大,占用的版圖的面積就越小,希望gate層不要用salicide涂上。所以需要對gate做特殊的處理,有一個特殊的層次是SAB(salicide block)金屬硅化物阻抗,有SAB的區域就不會加工salicide了,其他區域才加工。這樣就能提升方塊電阻

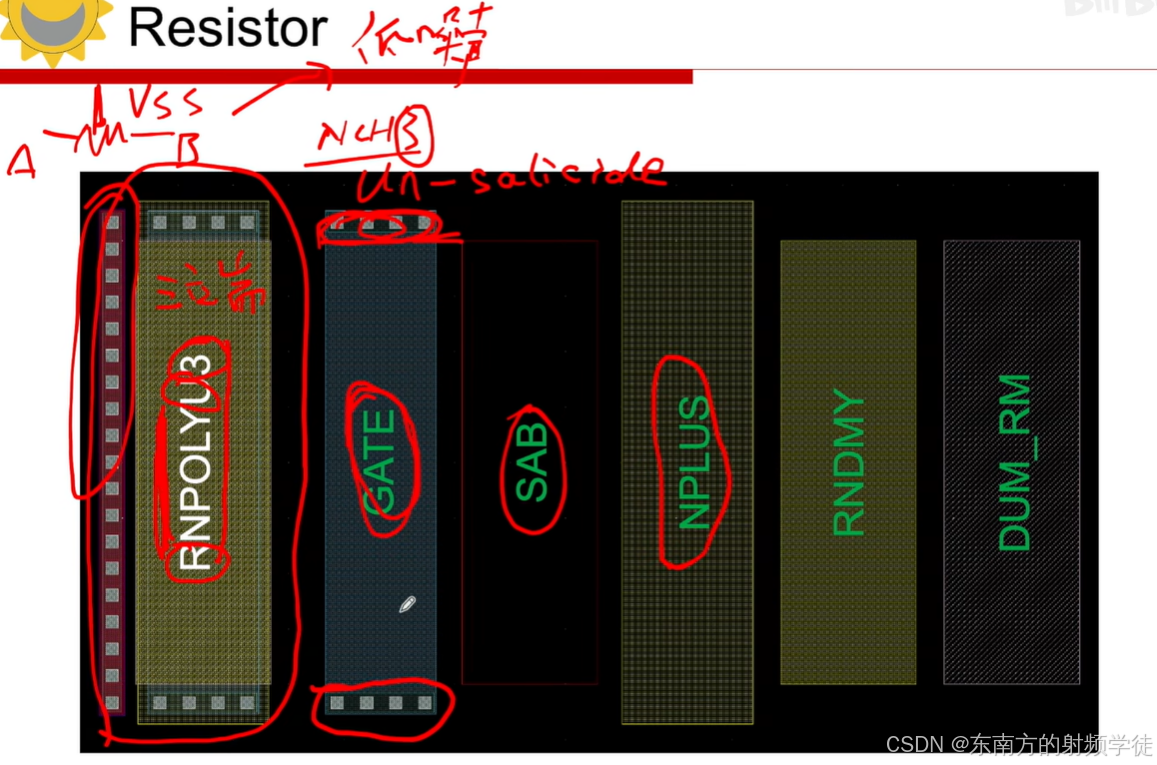

電阻的版圖

- 左邊的器件名字叫做r npoly U3,開頭的r表示resistor電阻,npoly表示有poly且上方有N+的注入,U表示un-salicide(不加salicide)也就是電阻的gate poly上要畫SAB,3表示三端口器件,第三端口主要為了接地,即這個電阻周圍要做接地的處理,目的是為了讓電阻下面的襯底電學特性更好一些,接地后底下的襯底不會有電壓的波動,降低電阻的噪聲。

- 拆開后有幾個層次,gate層作為電阻,N+注入(Nplus)(電阻的兩端也要有NPlus的覆蓋,SAB不能覆蓋到端口連接區),SAB增加方塊電阻,這些層次在一起就可以構成電阻器件了。

- RNDMY和DUM_RM是作為輔助層次

---【AniYaGUI1.2.0、AV_Evasion_Tool掩日、FoxBypass_V1.0】)

)

框架基礎)

——設計模式)