- 傳統方式

? ? ? ? 參考Xilinx官方文檔xapp524。對于AD9253器件 - 125M采樣率 - DDR模式,ADC器件的DCO采樣時鐘(500M?Hz)和FCO幀時鐘是中心對齊的,適合直接采樣。但是DCO時鐘不能直接被FPGA內部邏輯使用,需要經過BUFIO和BUFR緩沖后,得到s_bit_clk和s_frame_clk。此時,s_bit_clk和DCO時鐘不是相位對齊的。如果s_bit_clk直接采樣數據總線,則不能保證采樣到正確的數據。故需要進行鏈路訓練。

參考之前博客:? AD9253 LVDS 高速ADC驅動開發_lvds adc-CSDN博客??

step1:

? ? ? ?大概流程為:s_bit_clk采樣DCO時鐘信號,通過調節IDELAY,配合ISERDES原語,先穩定得到8'b11111111或8'b00000000(根據ADC器件手冊時鐘和數據相位關系來選擇),則表明s_bit_clk和DCO處于固定的相位關系,但不是邊沿對齊。然后再調節IDELAY,使得s_bit_clk采樣DCO時鐘信號,得到的結果為一個不確定值,則表明DCO和FCO時鐘信號已邊沿對齊,即鏈路s_bit_clk和DCO時鐘信號的相位關系已訓練完畢。

step2:每個數據點比特位的鏈路訓練,用于對齊采樣時鐘和每個數據點的比特順序。

s_bit_clk采樣FCO幀時鐘信號,通過調節ISERDES的bitslip,使得采樣到特定pattern,對于ADC9253器件而言,特定pattern為8'hf0。則表明每個數據點比特位的鏈路訓練完畢。

- 本文方式

傳統方式存在一個問題:需要DCO,FCO,多路DOUT走線和阻抗均需要保持完全一致,才能滿足手冊的時序關系。

在實際項目中,遇到一個問題:ADC9253的2個通道,有一個通道很穩定,另一個通道存在偶發的數據值跳變。于是修改訓練方案:

核心思路是每路數據總線和采樣時鐘s_bit_clk配合來單獨訓練,從而可以避免不同通道的差異性。因為傳統方法通過調節采樣時鐘s_bit_clk,使之與DCO對齊,這種調節類似于全局調節,DCO對每個通道都會起作用,如果兩個通道存在硬件設計差異,就會導致上述問題。

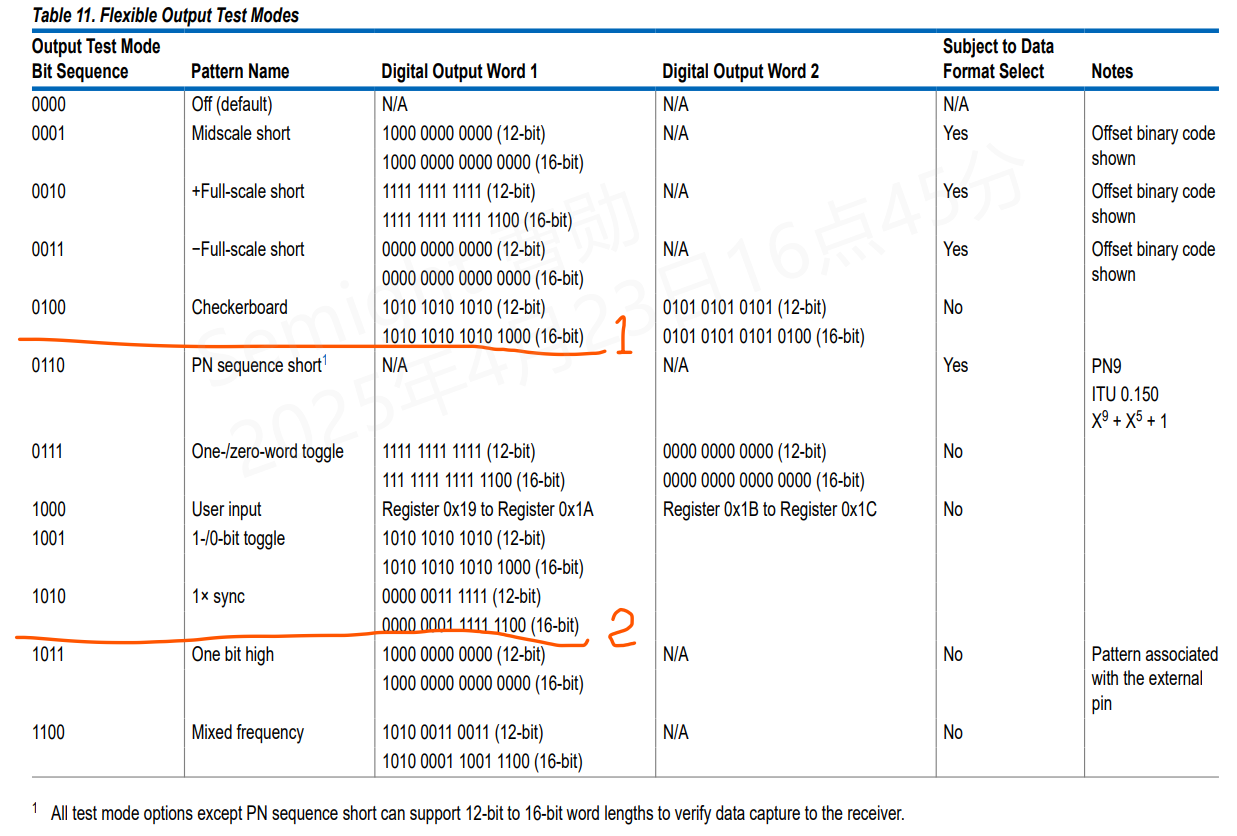

Step1:AD9253器件配置為test mode模式,test pattern為標號1所示。

通過調節IDELAY,配合ISERDES原語(可以使用selectio這個IP更方便),使得采樣時鐘s_bit_clk能采樣到穩定的值,比如10ms內采樣值都不變。說明:該值通常不會恰好等于測試pattern。

step2:每個數據點比特位的鏈路訓練,用于對齊采樣時鐘和每個數據點的比特順序。

對于每路數據總線,通過調節ISERDES的bitslip,使得采樣到預先設定的pattern,見標號1。當所有路數據總線均穩定采樣到預先設定的pattern,則表明AD9253鏈路訓練OK。

Step3:驗證環節。AD9253器件配置為test mode模式,test pattern為標號2所示。因為鏈路已經訓練OK,那么此時改變test pattern,所有通道,理論上也應該正確采樣到該test pattern值。實際項目測試,也驗證了該理論猜想。

- 補充說明:對于鏈路訓練,通常只訓練一次。但是如果受到溫度等因素干擾,鏈路可能失效。此時需要自適應的檢測到,并重新進入鏈路訓練環節。鏈路失效檢測方法:鏈路訓練OK后,可以用采樣時鐘s_bit_clk采樣FCO幀時鐘信號,當采樣值突然穩定的發生改變,不等于當前值,則表明鏈路失效。

- AD9253器件支持test mode。數據管腳可以輸出固定的 test pattern序列。

——大數據的意義與趨勢)

之三)