1 ?前言

FPGA(Field-Programmable Gate Array,現場可編程邏輯門陣列)是一種可編程的半導體器件,因其硬件可重構性、硬件并行計算能力、低延遲和實時性的優勢,廣泛應用于數字電路設計、原型驗證和系統加速等領域。但開發效率不足以及設計人員門檻較高,正在成為制約其應用落地的最大障礙。

在實際項目中,很多企業都會遇到這樣的困境:算法模型已經在仿真環境中跑通,但要真正達到在FPGA芯片上實現模型的功能,卻往往要經歷數周甚至數月的Verilog代碼開發設計、仿真測試和下板調試。這一過程不僅耗時耗力,并且對工程師也有較高的設計門檻,同時在整個開發周期中,需要算法、FPGA工程師密切配合和溝通,稍有不同步就可能導致返工,大大降低了開發驗證的效率和增加人力成本。

基于這一痛點,世冠科技GCKontrol平臺提供了“圖形化建模到自動生成Verilog代碼”的新方法,加速算法模型從理論到實踐下板驗證過程,幫助企業縮短FPGA開發周期和降低人力成本,促進產品化的進程,助力更高效的FPGA設計開發。

2 ?面臨的挑戰

在FPGA芯片上驗證的算法模型,從理論到實踐的全生命周期,以使用專業的工業軟件圖形化建模仿真為開始,到FPGA工程師編寫Verilog代碼,再到v代碼的仿真測試,最后以下板調試符合預期為結束。這一傳統流程存在四大挑戰:

01開發周期長

代碼開發和仿真時間往往占據整個項目周期的一半以上。

02跨專業協作成本高

算法工程師與FPGA工程師需要頻繁溝通,模型和代碼不同步的情況屢見不鮮。

03出錯率高

人工編碼語法或時序錯誤會導致大量返工與重復測試。

04代碼質量不穩定

人工編寫的代碼質量由工程師的水平決定,不同的工程師開發的代碼質量參差不齊,代碼風格不統一,不利于產品化。

對于追求快速原型驗證和產品迭代的企業而言,這些問題無疑嚴重制約了效率和競爭力。

3 ?解決方案

基于世冠科技GCKontrol平臺,提供了一種可以自動生成Verilog代碼的技術路線:工程師使用GCKontrol建模軟件,進行圖形化建模之后,經過一系列的操作,即可自動生成Verilog代碼,從而跳過人工編寫代碼和仿真測試的環節,通過IDE軟件將代碼綜合編譯后,將bit文件下載到FPGA芯片板卡上,實現對FPGA設計流程的高效優化。

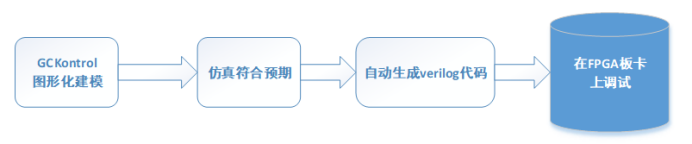

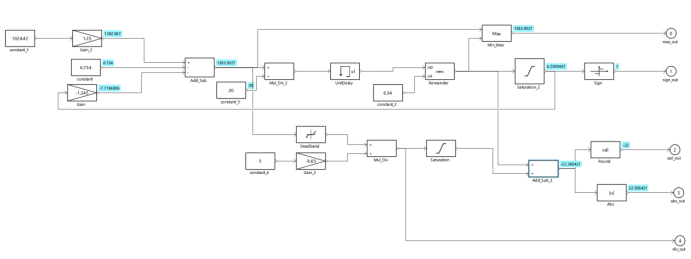

其方案框圖如圖1所示:

圖 1 方案框圖

接下來簡單介紹下目前GCKontrol建模軟件支持自動生成Verilog代碼的基礎模塊。

3.1 支持自動生成Verilog的基礎單元

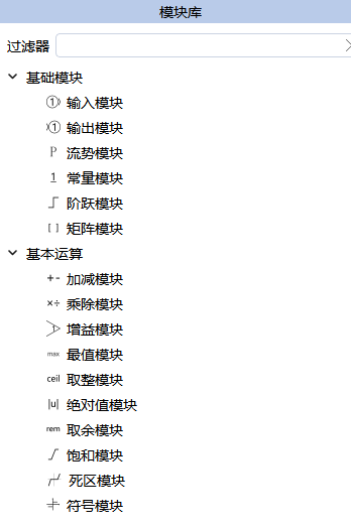

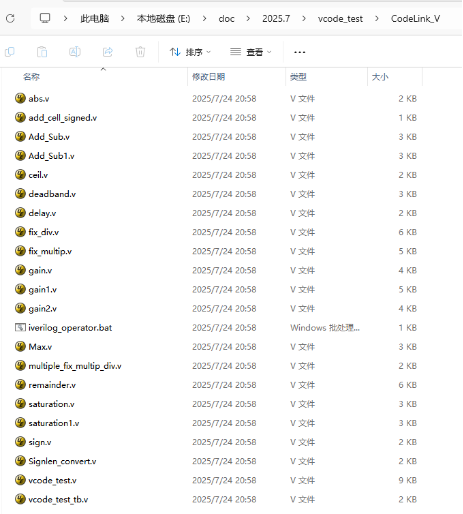

圖 2 支持自動生成Verilog代碼的基礎模塊

圖 3 支持自動生成Verilog代碼的模塊

由圖2和圖3可知,目前支持自動生成Verilog代碼的基礎模塊有輸入輸出模塊,常量模塊,加減模塊,乘除模塊,增益模塊,最值模塊,取整模塊,絕對值模塊,取余模塊,飽和模塊,死區模塊,符號模塊,積分模塊,微分模塊,延遲模塊,位轉換模塊,多條件表達式模塊,零階保持,斜坡函數,斜率限制函數等。

這些都是算法模型搭建的必要單元,這些模塊支持自動生成Verilog代碼,為滿足不同要求的算法模型的搭建提供了前提條件。目前還正在開發較為復雜的基礎函數和各種信號發生器等模塊,從而支持后續復雜度更高的模型搭建和下板驗證。

3.2 包含基礎運算模塊的工程示例

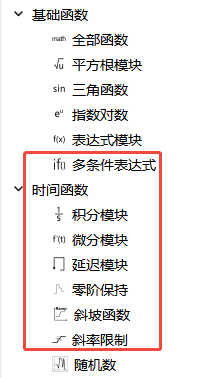

圖 4 搭建包含基礎運算模塊的gck工程

如圖4所示,可使用全部基本運算模塊搭建一個gck工程。點擊仿真后,如圖5所示,用戶可在界面上查看每個模塊的結果,也可通過2D面板靈活添加數據,查看任意模塊的仿真輸出。

圖 5 仿真結果顯示

價值點

工程師能夠在建模階段快速驗證算法邏輯,減少后期跨團隊的溝通與調試成本。

3.3 自動生成Verilog代碼

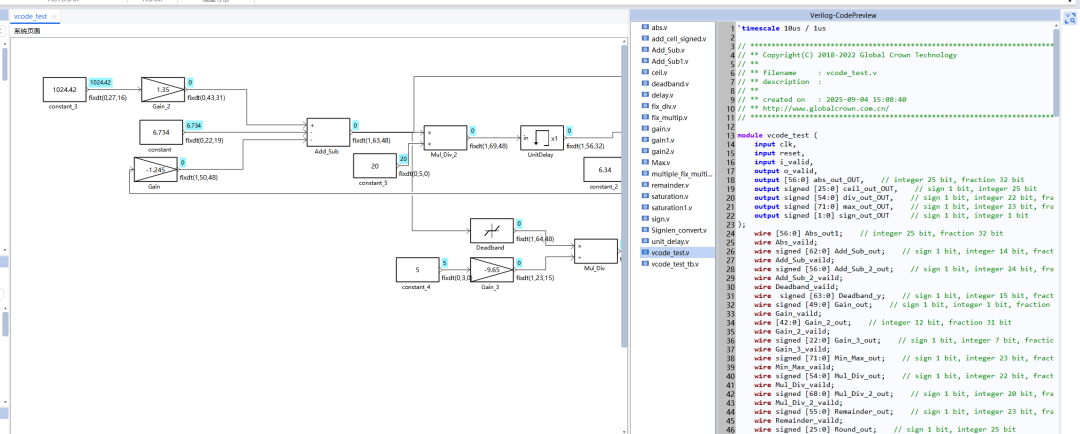

圖 6 自動生成Verilog代碼路徑

由圖6可知,在工程路徑的CodeLink_v的文件夾下,可以看到自動生成Verilog代碼的所有v文件。這些代碼符合行業規范,支持綜合編譯成bit文件并下板調試。

價值點

·自動生成的Verilog代碼與模型保持完全同步,杜絕“模型更新但代碼未更新”的問題;

·避免人工編碼語法錯誤和代碼質量不穩定的情形,提高一次性驗證成功率;

·直接可用的代碼顯著縮短下板調試周期。

3.4 附加功能——代碼預覽

圖 7 Verilog代碼預覽

由圖7可知,GCKontrol軟件自動生成Verilog代碼后,支持在界面對生成的代碼進行在線預覽,方便在模型級隨時查看自動生成的Verilog代碼。

價值點

模型與代碼實時對照,工程師在建模階段即可檢查邏輯,提前發現偏差,減少后期返工。

4 ?總結與展望

基于世冠科技GCKontrol平臺,通過將圖形化建模工程直接自動生成Verilog代碼,大大縮短了項目開發周期,節省了人力成本,并保證了代碼風格的穩定性和可靠性,極大的優化了FPGA的設計流程。

未來,GCKontrol將持續擴展模塊庫,支持通信、雷達、工業控制等更復雜的算法場景。助力更高效的FPGA設計開發,為復雜算法模型從理論到實踐的一鍵轉換提供更強有力的支持。

)

介紹(全球領先的云計算服務平臺,為企業和開發者提供包括計算、存儲、數據分析、人工智能、機器學習、網絡和安全等在內的全面云服務))

:Transformer在computer vision領域的應用(二))