再來對前仿和后仿的仿真內容回顧一下:

從概念上有個根本的理解

前仿真又可以分為布局前仿真和布局后仿真。前者是在設計的最初階段,建立和驗證詳細的電氣拓撲結構并以此制定出詳細的約束規則。后者是在布局完成的狀態下,在布線過程中遇到的具體設計問題需要仿真的過程,SI主要針對前者做仿真驗證。

后仿真是在PCB布線完成以后,對已經完成的關鍵網絡進行仿真驗證的過程。可以檢查實際的物理執行過程(布局布線)是否違背設計意圖:或是已知的改動,通過仿真來驗證這種改動給高速設計帶來的影響。

后仿真主要用的軟件有Allegro PCB SI、SIWave等。因為是做的后仿真工作,所以一般是導入已有的PCB文件也就是brd文件到軟件中進行建模。

SIWave后仿真的流程步驟

Siwave是-個用于信號完整性仿真的強大工具。它幫助工程師分析和優化高速電子設計,確保信號完整性并盡量減少電磁干擾(EMI)。

概述Siwave信號完整性仿真的一般流程。

1.模型創建,第一步是創建要分析的系統或PCB布局的模型。這涉及將設計文件,包括原理圖和布局,導入到Siwave中。您還可以定義模型中組件和互連的電氣特性。

2.電路仿真,模型創建后,您可以進行電路仿真,以分析系統的電氣行為。Siwave使用各種仿真技術,如暫態分析,頻域分析和眼圖分析,準確預測信號完整性性能。

3.電源完整性分析,對于高速設計來說,電源完整性至關重要,因為電壓波動可能影響系統的性能。Siwave允許您分析電源分配網絡(PDN),并識別潛在的問題,如電壓下降,地彈跳和解電容器優化。

4.信號完整性分析,Siwave使工程師能夠分析信號完整性問題,如反射,串擾和阻抗不匹配。您可以模擬高速信號并在時間和頻率域中分析其行為。Siwave提供各種分析工具,如眼圖,S參數和TDR圖,以幫助識別和解決信號完整性問題。

5.電磁干擾分析,電磁干擾(EMI)可能會降低電子系統的性能。Siwave提供EMI分析功能,以識別潛在的EMII源并評估其對設計的影響。您可以進行近場和遠場仿真,了解輻射圖案,并評估EMI減輕技術的有效性。

6.優化和設計驗證,在分析仿真結果后,您可以優化設計以改善信號完整性并盡量減少EMI。Siwave提供設計規則檢查(DRC)和制造設計(DFH)功能,以確保設計符合行業標準和制造要求。您還可以執行假設情景以評估設計更改并驗證最終設計。

總的來說,Siwave提供了一個全面的信號完整性仿真流程,從模型創建到設計優化。它使工程師能夠識別和解決信號完整性和EMI問題,確保高速電子系統的可靠性能。

通常情況下對于SI和PI是劃分不同部門的,SI不會去做PI的那部分工作,所以主要是還是對信號完整性做分析。

Allegro PCB SI 后仿真的基本流程

1、準備仿真模型和其他需求

1.1 、獲取所使用元器件的仿真模型

( 1 ) 通過官網,供應商等渠道獲取 IBIS 模型

( 2 ) IBIS 模型轉化為 DML 模型

( 3 ) 通過 Allegro 建立簡單 DML 模型以及模型分配

( 4 ) 通過 Allegro 建立復雜 DML 模型以及模型分配

1.2、了解 PCB 的布線規則以及原理圖部分邏輯

2、仿真配置

2.1、使用 SI Design Setup 配置

2.2、選擇需要配置的信號線

2.3、設置仿真庫

2.4、設置電源和地網絡

2.5、設置疊層

2.6、設置元器件類別

2.7、為元器件分配和創建模型

2.8、設置差分對

2.9、設置仿真參數

2.10、SI Design Audit 相關

2.11、提取拓撲

3、后仿真報告結果驗證

3.1、信號波形

3.2、反射報告,延時報告以及同步噪聲報告

這里面截幾張圖把涉及到的幾個點說明一下:

A、導入brd文件

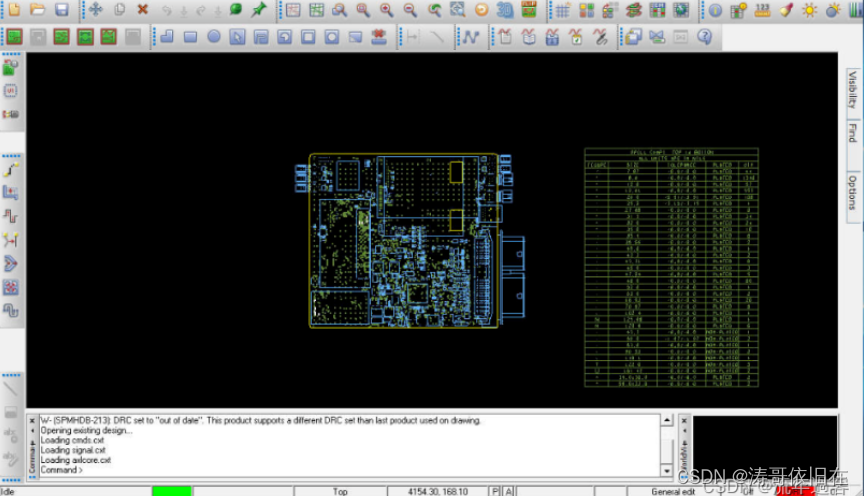

圖1.Allegro通過通過File->Open打開brd文件

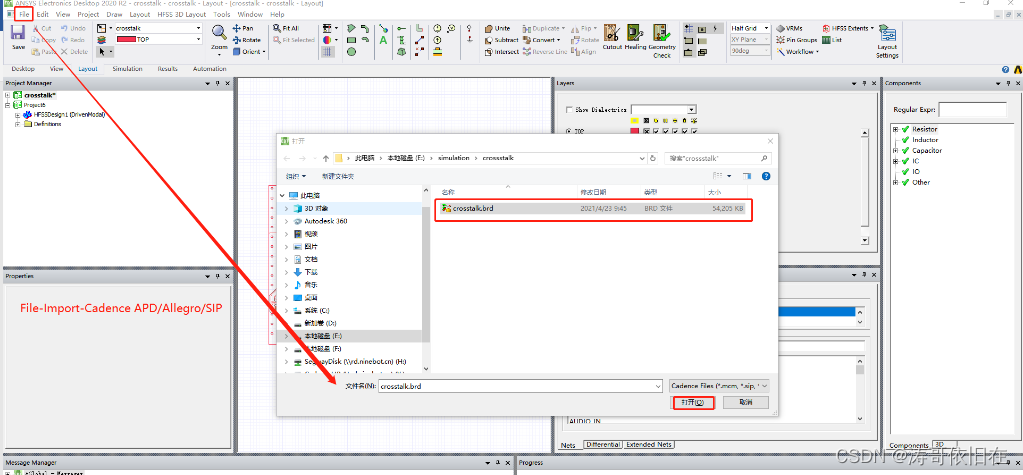

圖2.SIWave通過通過File->import-打開allegro brd文件

B、打入brd后,設置疊層(每層的厚度、材料、Dk\Df、銅的粗糙度、微帶線的形狀等)、過孔、焊盤、差分對、電源、接地、元器件設置等這兒不展開說了。

C、仿真后的報告結構驗證和文件導出

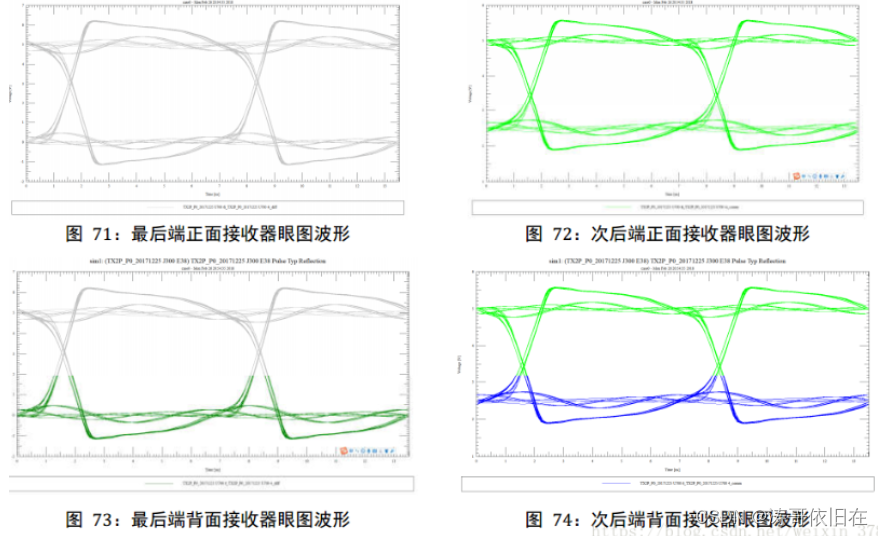

圖3.眼圖結果

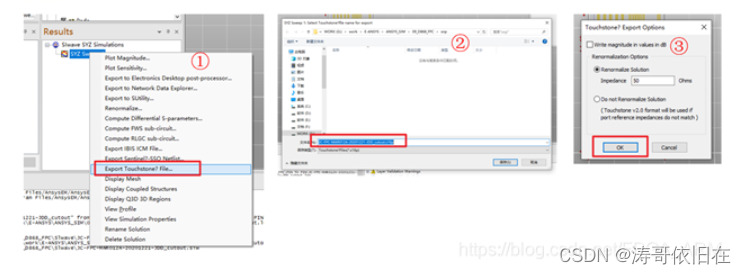

圖4.導出snp文件

以上種種是細節,本文不展開,就是讓大家了解后仿真和前仿真的不同,從概念上說就是是在PCB布線完成以后,對已經完成的關鍵網絡進行仿真驗證的過程。可以檢查實際的物理執行過程(布局布線)是否違背設計意圖;或是已知的改動,通過仿真來驗證這種改動給高速設計帶來的影響。

); 會導致內存泄露嗎?里面有SurfaceView ViewBinding)

)